### Réalisation d'un système de mesures d'impédances pour la caractérisation de cellules vivantes en régime dynamique

Nicolas Georges

### ▶ To cite this version:

Nicolas Georges. Réalisation d'un système de mesures d'impédances pour la caractérisation de cellules vivantes en régime dynamique. Sciences de l'ingénieur [physics]. 2013. hal-01860227

### HAL Id: hal-01860227 https://hal.univ-lorraine.fr/hal-01860227

Submitted on 23 Aug 2018

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-memoires-contact@univ-lorraine.fr

### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

54506 VANDOEUVRE LES NANCY

# Université de Lorraine Faculté des Sciences et Technologies

# Master Systèmes Embarqués et énergie

Spécialité « systèmes électroniques embarqués »

Année universitaire 2012/2013

Réalisation d'un système de mesures d'impédances pour la caractérisation de cellules vivantes en régime dynamique

Mémoire présenté par « Georges Nicolas » Soutenu le 13 septembre 2013

Stage effectué à l'Institut Jean Lamour Équipe 406 « Mesure Architectures Electroniques » Faculté des Sciences et Technologies BP 70239 bâtiment 2eme cycle Entrée 2A 3ème étage 54506 VANDOEUVRE LES NANCY Cedex

> <u>Tuteur universitaire</u> : Claudel Julien <u>Tuteur universitaire</u> : Kourtiche Djilali

54506 VANDOEUVRE LES NANCY

### Remerciements

Dans un premier temps, je remercie mes tuteurs de stage M. CLAUDEL Julien, Doctorant à l'Université de Lorraine travaillant sur le sujet de thèse sur lequel nous avons réalisé notre projet et M. KOURTICHE Djilali, Professeur à l'Université de Lorraine pour nous avoir introduit clairement le sujet de stage et d'avoir été disponibles pour répondre à mes questions.

Puis dans un second temps, nous remercions l'Université de Lorraine et l'Institut Jean Lamour qui m'ont accueilli et ont su trouver des financements pour l'achat des éléments qui m'ont permis d'avancer sur notre projet.

### 54506 VANDOEUVRE LES NANCY

### Table des matières

| Int | roduct | tion                                                                 | 4  |

|-----|--------|----------------------------------------------------------------------|----|

| 1.  | Prés   | sentation du sujet de stage                                          | 5  |

| :   | 1.1.   | Contexte.                                                            | 5  |

|     | 1.2.   | Travail à réaliser                                                   | 5  |

| :   | 1.3.   | Compétences requises.                                                | 5  |

| 2.  | Etuc   | de Bibliographique                                                   | 6  |

| :   | 2.1.   | Caractéristiques électriques et diélectriques du milieu.             | 6  |

| :   | 2.2.   | Techniques de mesure d'impédance.                                    | 8  |

| 3.  | Imp    | olémentation du système de mesure                                    | 11 |

| ;   | 3.1.   | Support utilisé                                                      | 11 |

| ;   | 3.2.   | Système de mesure de type détection synchrone                        | 12 |

| ;   | 3.3.   | Simulation.                                                          | 13 |

| ;   | 3.4.   | Réalisation.                                                         | 14 |

|     | 3.4.   | 1. Simulation de la PLL.                                             | 14 |

|     | 3.4.   | 2. Simulation et test de la génération des signaux sinusoïdaux       | 15 |

|     | 3.4.   | 3. Test d'envois et de réceptions des signaux sinusoïdaux            | 18 |

|     | 3.4.   | 4. Test de la multiplication.                                        | 20 |

|     | 3.4.   | 5. Implémentation du filtre et conditionnement des données en sortie | 21 |

|     | 3.4.   | 6. Implémentation du projet sur la carte                             | 24 |

| 4.  | Con    | oclusion                                                             | 26 |

| 5.  | Ann    | nexes                                                                | 28 |

| Bib | liogra | phie                                                                 | 38 |

#### 54506 VANDOEUVRE LES NANCY

### Introduction.

Le sang est un fluide vital circulant de façon continue dans les vaisseaux sanguins et le cœur. Ce liquide permet de diffuser le dioxygène ainsi que les éléments nutritifs nécessaires à l'être humain. Il permet aussi de transporter les déchets, tels que le dioxyde de carbone, en vue d'être éliminés par le corps. Il permet également d'amener aux tissus les éléments indispensables au point de vu immunitaire et à diffuser les hormones dans tout l'organisme.

En cas d'anomalies chez un individu, il peut être nécessaire de procéder à des analyses de sang afin de déterminer la source du problème. D'autre part, afin d'en savoir plus sur le fonctionnement du corps humain, il peut être utile de connaître les caractéristiques des différentes cellules présentes dans le sang.

Au cours du siècle dernier, un certain nombre de méthodes ont été développées pour déterminer les propriétés électriques et diélectriques des cellules biologiques en suspension dans un liquide tel que le sang. La majorité des techniques développées sont limitées étant donné qu'elles ne donnent qu'une indication globale des caractéristiques électriques et diélectriques des différents composants du milieu mesurés [1].

En effet, chaque élément présent dans le sang a des comportements et des caractéristiques différentes (globules blancs, globules rouges, plaquettes, plasma etc.). C'est pourquoi, les caractéristiques déterminées ne permettent pas une bonne discrimination des caractéristiques de chaque élément.

Depuis peu, avec le développement significatif des micro-technologies, des expériences mettant en évidence les caractéristiques unitaires des différentes cellules présentes dans le sang ont pu être effectuées [1] [2]. Ces expériences nécessitent des outils spécifiques et dédiés.

A travers ce stage, qui s'inscrit dans la continuité d'un projet effectué le semestre dernier, nous allons tenter de réaliser le conditionnement électronique d'un capteur de type micro-fluidique. Il consiste en la génération, le traitement et l'analyse de signaux permettant la caractérisation de cellules à l'aide d'une carte FPGA, permettant la miniaturisation et la diminution des coûts comparé aux appareils standard déjà présents sur le marché.

54506 VANDOEUVRE LES NANCY

# 1. Présentation du sujet de stage.

#### 1.1. Contexte.

Ce stage s'inscrit dans la continuité d'un projet effectué dans le cadre d'un travail de thèse effectué à l'institut Jean Lamour, sur la réalisation d'un capteur micro-fluidique pour la caractérisation de cellules en régime dynamique, par spectroscopie d'impédance. Les informations contenues dans les mesures d'impédance des milieux et tissus biologiques peuvent nous renseigner sur les propriétés physiques et chimiques de ceux-ci. Il est ainsi possible d'utiliser ces mesures comme moyens de diagnostic ou de suivit temporel de l'état d'un tissu (reproduction cellulaire, mort cellulaire...). Ce projet rejoint la dynamique actuelle des Lab-on-Chip (laboratoire sur puce); systèmes portatifs permettant des analyses rapides et peu couteuses sur des échantillons de faibles dimensions.

Lors de ce stage, il sera réalisé un outil de mesure d'impédance rapide appliqué à la mesure des caractéristiques de cellules en suspensions (typiquement le cas des cellules du sang). Cet outil sera réalisé grâce à une carte mère FPGA couplée à une carte fille embarquant des convertisseurs analogique/numérique et numérique/analogique haute vitesse; permettant la génération, l'acquisition et le traitement des signaux de mesure.

#### 1.2. Travail à réaliser.

- Etude bibliographique sur les caractéristiques électriques (conductivité) et diélectrique (permittivité) des milieux biologiques, ainsi que sur les techniques de mesure d'impédance.

- Implémentation d'un système de mesure basé sur le principe de la détection synchrone (Lock-In amplifier).

### 1.3. Compétences requises.

Afin de mener à bien ce sujet, il est nécessaire d'avoir des connaissances en implémentation FPGA et description VHDL ainsi qu'en programmation C/C++.

54506 VANDOEUVRE LES NANCY

# 2. Etude Bibliographique.

#### 2.1. Caractéristiques électriques et diélectriques du milieu.

Figure 1: Principaux composants du sang [5].

Les cellules en suspensions sont caractérisées de façon générale par leurs effets résistifs (conductivités des ions en solution) et capacitifs (permittivités propre des espèces présentes, effets d'interfaces, capacités membranaires). Ces caractéristiques peuvent être déduites des mesures d'impédances par application d'un modèle électrique ou mathématique. Les plus connus étant le modèle mathématique de Maxwell [1] [3] et le modèle électrique de Fricke [1] [4].

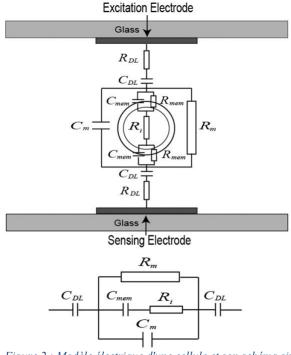

Figure 2 : Modèle électrique d'une cellule et son schéma simplifié [1].

#### 54506 VANDOEUVRE LES NANCY

Sur le schéma précédent, nous pouvons observer le modèle du circuit équivalent d'une cellule suspendue entre une paire de micro électrode.  $R_{DL}$  et  $C_{DL}$  représentent la résistance et la capacitance de la double couche électrique<sup>1</sup>, celle-ci à une haute impédance en basse fréquence,  $R_m$  et  $C_m$  représentent la résistance et la capacitance du milieu,  $R_{mem}$  et  $C_{mem}$  la résistance et la capacitance de la membrane de la cellule, et  $R_1$  la résistance du cytoplasme<sup>2</sup>. Dans la seconde partie de la figure 2 est représenté le schéma électrique simplifié.

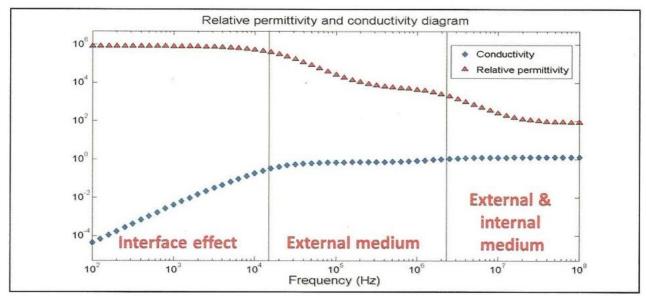

Figure 3 : Spectre électrique et diélectrique général d'une suspension de cellule.

Sur la figure ci-dessus, Nous pouvons y voir que les effets des différentes parties de ce modèle, se répercutent à des fréquences différentes, et peuvent donc être déterminés par des mesures à des fréquences discrètes.

<sup>&</sup>lt;sup>1</sup>La double couche électrique est un modèle décrivant la variation du potentiel électrique aux abords d'une surface.

<sup>&</sup>lt;sup>2</sup> Le cytoplasme désigne l'intérieur d'une cellule vivante.

#### 54506 VANDOEUVRE LES NANCY

#### 2.2. Techniques de mesure d'impédance.

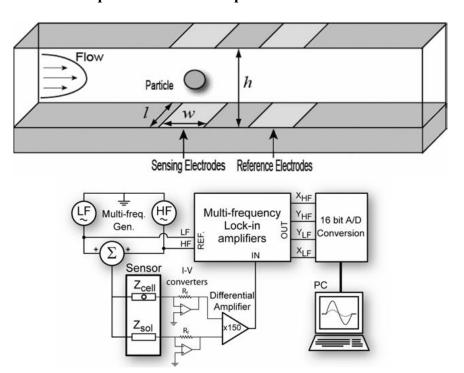

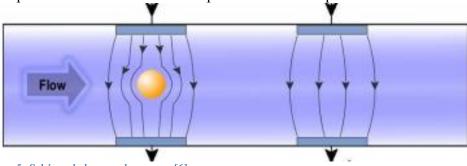

Figure 4 : Schéma d'un capteur micro-fluidique et d'un système de mesure par spectroscopie d'impédance [1]

Le capteur utilisé pour la mesure d'impédance est constitué de deux réservoirs. Un d'entrée pour le dépôt de l'échantillon liquide (sang) et un de sortie pour la réception de ce même échantillon. Ce liquide est déplacé par un système de pompage dans la zone de mesure, qui est composée de microélectrodes en platine dans un canal de section 20um x 20um. La figure ci-dessous schématise la zone de mesure. La mesure d'impédance doit s'effectuer en temps réel pendant le passage de la cellule au centre de cette zone de mesure. Seules les valeurs d'impédance mesurées lorsque la cellule se situe au centre de la zone de mesure sont utiles. Les figures 4 et 5 schématisent le principe de fonctionnement d'un capteur micro-fluidique.

Figure 5: Schéma de la zone de mesure [6]

#### 54506 VANDOEUVRE LES NANCY

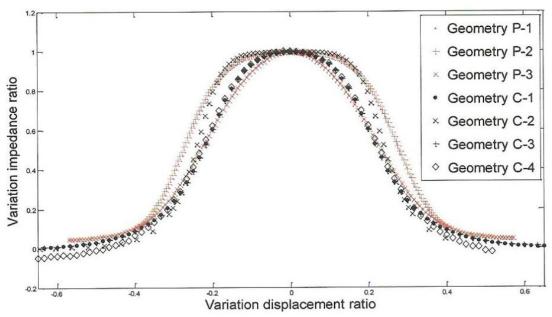

Figure 6: Variation de l'impédance lors du passage d'une cellule dans la zone de mesure

La courbe au-dessus est issue de résultats de simulation. Elle permet d'observer la variation d'impédance à une fréquence donnée lors du passage d'une cellule pour plusieurs géométries d'électrodes. On observe que les mesures "utiles" se situent dans la zone où la variation est maximale. Le système de mesure final doit donc être capable de mesurer des échantillons d'impédance à une fréquence suffisante, afin d'obtenir pour chaque passage de cellule au moins une mesure exploitable.

#### 54506 VANDOEUVRE LES NANCY

#### 2.3. Principe de la détection synchrone.

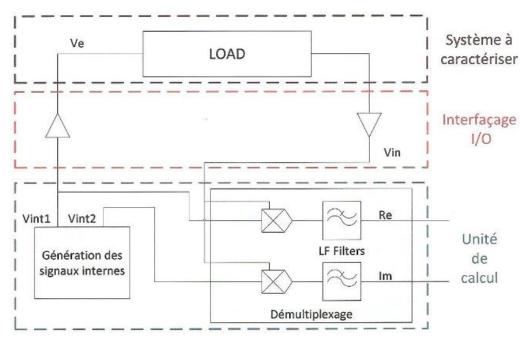

L'amplificateur à détection synchrone (Lock-in Amplifier) permet la mesure de faibles signaux sinusoïdaux, même très bruités. Ce mode de mesure est donc parfaitement adapté à la mesure de tissus biologiques, qui nécessitent l'utilisation de tensions et de courants très faibles afin de ne pas altérer ou détruire un échantillon de faibles dimensions ce qui entraine une forte sensibilité au bruit. Le principe repose sur une démodulation suivant une fréquence porteuse, comme dans le cas d'une transmission de données.

On génère en interne deux signaux de même fréquence mais en quadrature de phase: Vint1 et Vint2. Le premier est utilisé pour générer le signal d'excitation Ve.

Le signal de réponse Vin est ensuite multiplié d'une part par le signal Vint1 et de l'autre par Vint2. Cette action permet d'obtenir deux signaux dont les composantes continues sont respectivement fonction de la partie réelle et de la partie imaginaire du signal mesuré. On obtient ainsi directement la réponse du système après application d'un filtre passe bas à ces signaux.

La figure ci-dessous illustre le principe de fonctionnement d'un système de mesure à détection synchrone, et les calculs (voir "Equations sur les sinus") associés permettent d'éclaireir l'obtention des résultats décrits précédemment.

Figure 7: Schéma de principe d'un système de mesure par détection synchrone

54506 VANDOEUVRE LES NANCY

# 3. Implémentation du système de mesure.

### 3.1. Support utilisé.

La caractérisation de la cellule doit se faire à l'aide de 2 fréquences au minimum. En effet, une fréquence permet de déterminer la conductivité et la permittivité relative du cytoplasme et l'autre celle de la membrane et de la dimension de la cellule. La fréquence permettant de déterminer l'impédance de la partie externe se situe dans les alentours de 100kHz alors que celle de la partie interne se situe dans les alentours de 10MHz. La carte de développement doit donc être capable de générer et traiter des signaux à ces fréquences. Nous devons donc faire appel à une carte dont la fréquence d'horloge doit pouvoir atteindre au minimum 100MHz. D'après le théorème d'échantillonnage, il faut au minimum une fréquence d'échantillonnage de 20MHz pour un signal de 10MHz. Cependant, il est préférable d'utiliser une fréquence plusieurs fois supérieure.

Les cellules étant des éléments très sensibles, il ne faut pas utiliser de tensions supérieures à 100mV. Ceci dit, pour avoir des signaux interprétables, les tensions ne doivent pas être inférieures à 10mV.

Voici les cartes utilisées qui répondent à nos attentes :

### <u>Caractéristiques de la carte mère : DE2–115</u>

- Horloge de 50MHz (possibilité d'augmenter à 100MHz en utilisant une PLL)

- Mémoires incluses : SDRAM (128Mo), SRAM (2Mo), Flash (8Mo), EEPROM (32Kbits)

- Ecran d'affichage LCD (16x2)

- Lecteur de carte SD

- Ports USB Type A & B (dialogue)

Comme nous avions déjà travaillé lors de notre cursus sur des cartes Altera, et que nous disposons de la licence complète pour Quartus, nous avons privilégié les FPGA de chez Altera.

#### 54506 VANDOEUVRE LES NANCY

### Caractéristiques de la carte fille : AD/DA Data conversion

- Connecteur HSMC

- 2 AD de 14bits à 150MSPS

- 2 DA de 14bits à 250MSPS

Les convertisseurs nous permettent de travailler à des fréquences suffisamment élevées pour pouvoir répondre aux contraintes qu'induit le système de mesure.

### 3.2. Système de mesure de type détection synchrone.

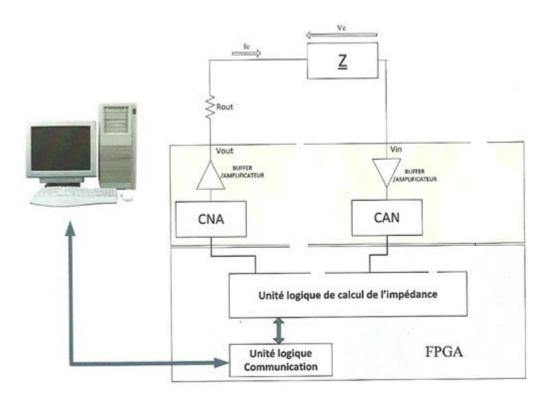

Figure 8: Schéma du système de mesure

#### 54506 VANDOEUVRE LES NANCY

Comme illustré dans la Figure 8, on utilisera un système de mesure deux points pour la détection synchrone, comme les valeurs des impédances sont suffisamment élevées on peut considérer que le courant sera image de la tension aux bornes de la charge.

Les convertisseurs se trouvent sur la carte fille, après la charge, il se peut que l'on ajoute un ampli/buffer entre celle-ci et la carte fille pour corriger des problèmes d'adaptation d'impédance et augmenter l'amplitude du signal mesurer si celui-ci est trop faible.

L'unité de calcul correspond à-peu-près à celle illustré dans la figure 7, un schéma détaillé sera présenté plus tard.

Ensuite les données seront rapatriées via l'unité logique de communication.

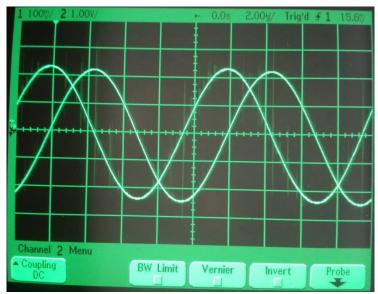

Les signaux générés par le système de mesures seront une sinusoïde et une autre sinusoïde avec un retard de  $\pi/2$ .

#### 3.3. Simulation.

Pour mieux cerné les signaux attendu, une simulation sous l'outil de CAO ProtelDXP a été effectué

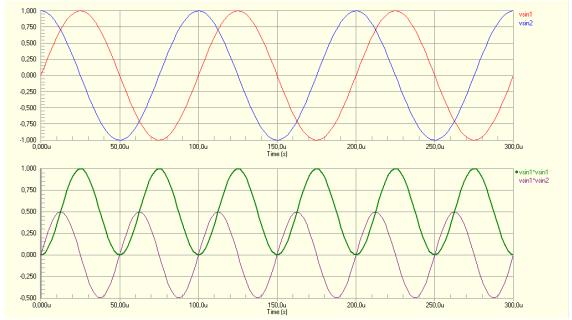

Figure 9: résultats de la simulation

Sur le premier graphique, les signaux décris sont ceux sur lesquels nous devons effectuer des traitements. En bleu, il s'agit du sinus envoyé sur la cellule et en bleu celui déphasé de Pi/2. Afin de simplifier la simulation, Vsin1 et Vsin2 ont la même amplitude. Sur le second graphique, Le sinus mesuré est dans un premier temps multiplié par Vsin1 puis par Vsin2. Nous obtenons donc les 2 sinus présents ici en violet et vert.

Si on observe la valeur moyenne du signal en vert, on s'aperçoit qu'elle est de 0.5V et qui lorsqu'elle est multipliée par 2 nous donne 1V. D'autre part, si on observe la valeur moyenne du signal en violet, on s'aperçoit qu'elle est de 0V et qui lorsqu'elle est multipliée par 2 donne toujours 0V.

En analysant les données ci-dessus, on peut donc dire que la partie réelle est de 1V, la partie imaginaire de 0V et le déphasage de 0.

#### 54506 VANDOEUVRE LES NANCY

Afin d'observer la composante continue, il faut effectuer une moyenne des signaux vert et violet en utilisant un filtre passe bas dont la fréquence de coupure est très inférieure à la fréquence des signaux initiaux (Vsin1 et Vsin2).

#### 3.4. Réalisation.

Pour la réalisation de ce projet, j'ai travaillé de manière progressive en décomposant et en testant fonction par fonction chacune des parties.

#### 3.4.1. Simulation de la PLL.

Si l'on souhaite travailler avec des signaux sinusoïdaux de fréquences de 10MHz, il faut avoir une fréquence d'horloge de 100Mhz pour pouvoir avoir 10 échantillons par période. La carte Terasic DE2-115 permet de générer jusqu'à 4 PLL. Nous allons utiliser la fonction ALTPLL généré à l'aide de l'outil Megawizard Plug-In Manager d'Altera. A partir de la fréquence d'horloge interne au FPGA de 50MHz, l'outil va nous permettre de générer le signal d'horloge voulu.

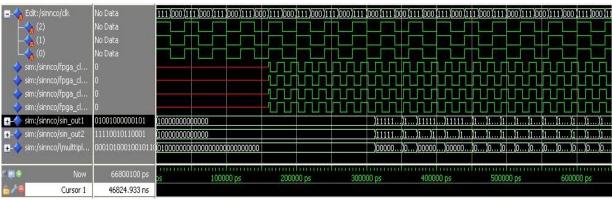

#### Résultats sous ModelSim:

En simulant les signaux de fréquence d'entrée et fréquence de sortie, on s'aperçoit que la PLL fonctionne correctement. En effet, le signal issu de la PLL a bien une période 2 fois plus faible que le signal d'horloge. Les signaux suivants prouvent son bon fonctionnement.

Figure 10 : Simulation de la PLL de 100Mhz sous ModelSim

Les résultats étant satisfaisants, la PLL sera implémenté sur le FPGA.

#### 54506 VANDOEUVRE LES NANCY

#### 3.4.2. Simulation et test de la génération des signaux sinusoïdaux.

Pour générer les sinusoïdes, plusieurs solutions étaient possibles. Utiliser une table d'observation (look-up table) pour lire les valeurs et les envoyer vers les convertisseurs étaient la solution la plus simple à mettre en œuvre mais n'est pas évolutive, si nous voulions éditer les valeurs ou la fréquence de lecture des donnés cela devenait plus compliqué.

Nous avons donc généré un sinus à l'aide de la fonction NCO<sup>3</sup> du MegaWizard Plug-In Manager d'Altera.

Dans la rubrique parameters : AngularResolution => 14 Magnitude Precision => 14 Phase Increment Value => 100MHz Décocher : Implement Phase Dithering

Dans la rubrique Implementation :

Target => Cyclone IV E Cocher: Single Output

#### Résultats:

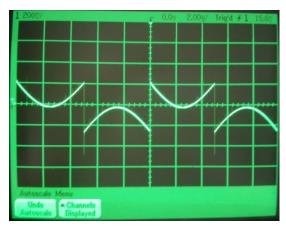

En observant le signal généré à l'aide d'un oscilloscope, nous avons remarqué que le signal ressemblait à un sinus avec débordement. Nous avons donc tenté de diminuer le nombre de bits qui était alors de 14 à 13. Le problème a persisté, nous avons constaté que si l'on inversait les 2 « demilobes », nous pouvions obtenir un sinus ; Nous avons donc pensé que le bit de signe (bit 13) était inversé. Nous avons donc complémenté la valeur du bit 13, ce qui s'est traduit par l'obtention d'un sinus.

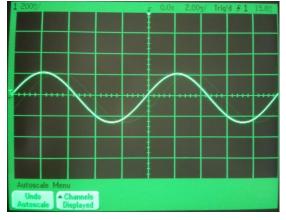

Figure 12: Deuxième tentative de génération de sinusoïde

<sup>&</sup>lt;sup>3</sup> Numerically Controlled Oscillator (oscillateur controlé numériquement)

#### 54506 VANDOEUVRE LES NANCY

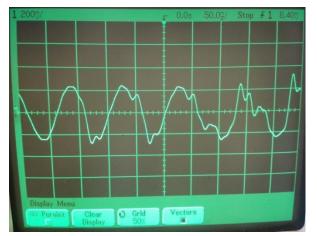

Nous avons ensuite tenté de générer un sinus à la fréquence de 1MHz puis à 10MHz. A 1MHz, nous avons obtenu un sinus à l'oscilloscope sans difficultés alors que pour la fréquence de 10MHz, nous avons éprouvé des difficultés étant donné que le NCO créait les échantillons suivants en fonctions des précédents (récursivité). Par la suite, il faudra trouver une méthode de génération de sinus qui elle sera non récursive afin d'éviter ce genre de soucis. C'est pourquoi, il suffit qu'un échantillon soit mal déterminé pour que tout le sinus soit altéré. Nous avons relevé les signaux suivants à l'aide de l'oscilloscope :

Figure 13: Sinusoïde à 10 MHz mal capturée

Figure 14: Sinusoïde à 10MHz bien capturée

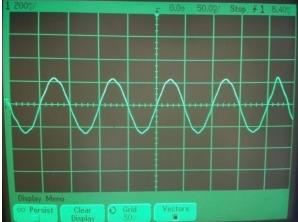

Suite à un changement de matériel, avec le nouvel oscilloscope à large bande de fréquence, les irrégularités n'étaient plus visibles. Cela venait donc de la bande passante limitée de l'oscilloscope Dans un second temps, nous avons essayé de générer un second sinus qui lui était déphasé de Pi/2 par rapport au premier.

Pour se faire, il a fallu choisir la fonction « NCO » dans DSP => Signal Generation => NCO. En gardant les paramètres initiaux, il a fallu modifier :

Dans la rubrique parameters :

AngularResolution => 14

Magnitude Precision => 14

Phase Increment Value =>100MHz

Décocher : Implement Phase Dithering

Dans la rubrique Implementation :

Target => Cyclone IV E

Cocher: Phase Modulation Input

ModulatorPrecision => 32 Modulator Pipeline Level => 1

Cocher: Single Output

### 54506 VANDOEUVRE LES NANCY

### <u>Résultats</u>:

De la même manière que précédemment, il a fallu inverser le bit de signe afin d'obtenir un sinus. Par défaut, la valeur maximum de « phase\_mod » correspond à un retard de 2Pi. Pour optenir un retard de Pi/2, il a fallu diviser la valeur de « phase\_mod » par 4 en mettant à 1 le 31eme bit et tous les autres à 0; Nous avons obtenu un sinus en quadrature.

Figure 15: Sinus et sinus retardé de PI/2

#### 54506 VANDOEUVRE LES NANCY

### 3.4.3. Test d'envois et de réceptions des signaux sinusoïdaux.

Une fois la génération des signaux effectuée nous avons testé l'envoi et la réception du sinus via la carte AD/DA Data conversion.

En sortie des CAN et en entrée des CNA se trouve des transformateurs de chez Mini-Circuit.

|                                                       | DE Tropoformor                                 |                                                                                       | TT1-6-KK81+<br>TT1-6-KK81                                     |

|-------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 50Ω 0.0                                               | 004 to 300 N                                   | √HZ<br>Features                                                                       | m                                                             |

| Operating Temperature Storage Temperature             | -20°C to 85°C<br>55°C to 100°C                 | wideband, 0.004 to 300 MHz     good return loss     also available with plug-in (X65) | CASE STYLE: KK81<br>PRICE: \$6.95 ea. QTY (1-9)               |

| RF Power DC Current Permanent damage may occur if any | 250mW<br>30mA<br>of these limits are exceeded. | and flat-pack (W38) leads                                                             | + RoHS compliant in accordance with EU Directive (2002/95/EC) |

Figure 16: Partie des spec. technique des transformateurs

On peut constater que le transformateur permet une adaptation d'impédance entre entrée et sortie en appliquant à celles-ci une impédance de 50  $\Omega$ . Autre spécification il agit comme un filtre passe haut en suppriment les valeurs continues.

A la réception, pour avoir des valeurs correspondant au signal réel et pouvoir effectuer les calculs il faut convertir le signal reçu en nombre signé en complément à deux. Pour cela il faut : Inverser les valeurs des bits reçus et ajouter la valeur '1'.

De même, il faut répéter la même opération pour les signaux internes qui étaient des nombres non signés.

#### 54506 VANDOEUVRE LES NANCY

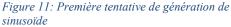

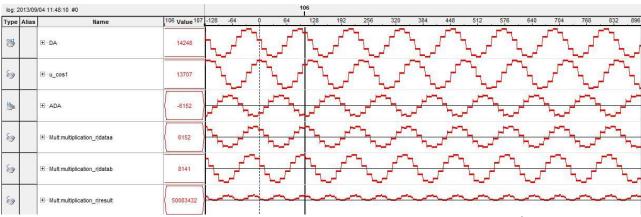

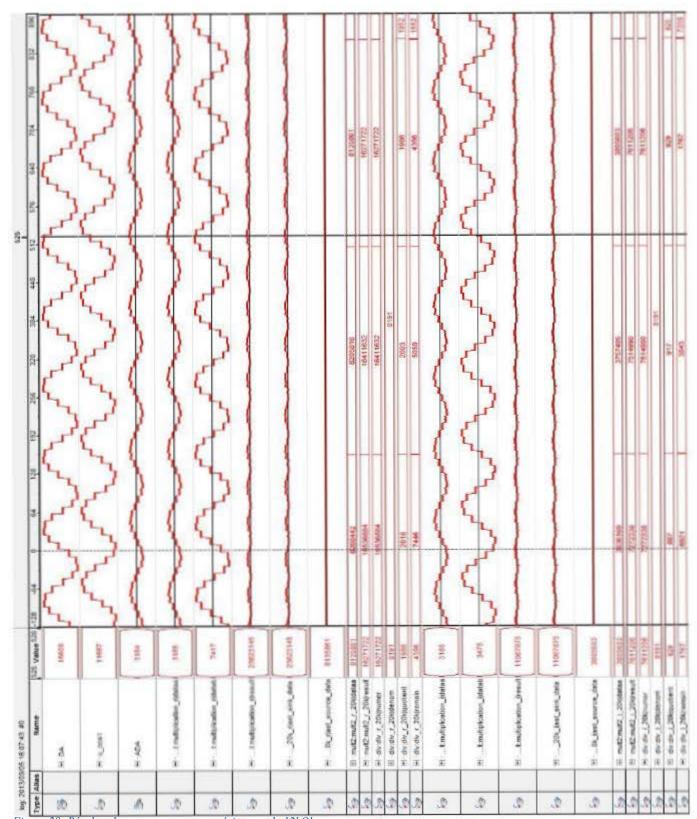

Figure 17: Aperçu des résultats de réception et de multiplication des signaux via SignalTap Logic Analyzer<sup>4</sup>

Dans la figure ci-dessus, on peut observer 6 signaux différents, ils correspondent aux signaux obtenus lorsque le CNA est relié directement au CAN. Le premier est la sinusoïde envoyée (en nombre non signé) via le CNA; u\_cos1 est le signal non signé correspondant à la sinusoïde retardée de  $\pi/2$ ; ADA est le signal reçu par le CAN, observé à sa sortie, il est systématiquement inversé : le signal dans son cheminement traverse deux transfo que l'on peut considérer comme élément purement inductif, chacun retarde donc le signal de  $\pi/2$ .

Au maximum, le signal ADA à une valeur de 6152 alors qu'il est censé être sans perte (soit 8192 ou 2^13), cela est dû aux transformateurs, ceux-ci induisent une baisse de niveau on peut évaluer la perte à hauteur de 2.48 dB :

#### Transformer Electrical Specifications

| RATIO | FREQUENCY<br>(MHz) | INSERTION LOSS* |             |             |

|-------|--------------------|-----------------|-------------|-------------|

|       |                    | 3 dB<br>MHz     | 2 dB<br>MHz | 1 dB<br>MHz |

| 1     | 0.004-300          | 0.004-300       | 0.02-200    | 0.1-50      |

<sup>\*</sup> Insertion Loss is specified with input at pin 4 and output at pin 1 with pins 6 & 3 grounded and pins 2 & 5 open.

-

<sup>&</sup>lt;sup>4</sup> Outil permettant d'observer les signaux interne au FPGA

#### 54506 VANDOEUVRE LES NANCY

#### Typical Performance Data

| FREQUENCY<br>(MHz) | INSERTION<br>LOSS<br>(dB) | INPUT<br>R. LOSS<br>(dB) |

|--------------------|---------------------------|--------------------------|

| 0.004              | 2.53                      | 4.71                     |

| 0.020              | 0.29                      | 15.34                    |

| 1.150              | 0.10                      | 37.84                    |

| 100.860            | 0.89                      | 10.71                    |

| 151.510            | 1.10                      | 9.32                     |

| 200.000            | 1.08                      | 9.41                     |

| 280.250            | 0.87                      | 12.74                    |

| 350.000            | 0.81                      | 24.39                    |

| 430.250            | 1.11                      | 11.24                    |

| 500.000            | 2.74                      | 6.16                     |

Figure 18: Pertes dans les transformateurs suivant la fréquence du signal

Ces signaux sont de fréquence de 500KHz et contiennent 10 échantillons par période. Nous aurions pu augmenter le nombre d'échantillons mais la nature du lock-in amplifier nous permet de nous contenter de ça, ce qui nous permet un gain de place sur le FPGA ainsi que de vitesse de traitement des données.

Ces observations permettent de constater que la transmission des signaux s'effectue correctement. Les signaux suivant correspondent à la multiplication du signal reçu par le CAN et du sinus généré en interne.

#### 3.4.4. Test de la multiplication.

Cette première multiplication va nous permettre de réaliser le produit entre le signal reçu par le CAN et les signaux générés en interne (voir figure 7).

Cette fonction est réalisée à l'aide de la fonction LMP\_MULT de l'outil MegaWizard Plug-In Manager d'Altera. Elle permet une certaine souplesse pour le choix du nombre de bits en entrée et en sortie ainsi que le type de multiplication (signé, non signé, etc...).

Figure 19: Signaux servant à la multiplication

En effectuant le calcul analytiquement nous observons sur le même résultat :

6152 \* 8141 = 50083432

Le produit entre les deux signaux est bien effectué.

### 54506 VANDOEUVRE LES NANCY

### 3.4.5. Implémentation du filtre et conditionnement des données en sortie.

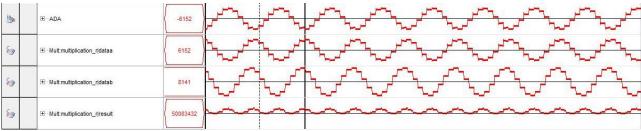

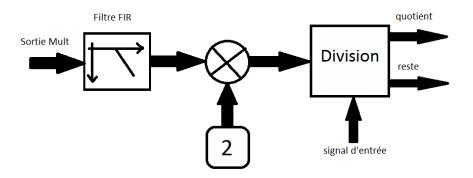

Le schéma en figure 7 n'étant pas complet pour en déduire la valeur de l'impédance mesuré, en voici un schématisant la suite du calcul :

Les équations en figure 25 montrent que l'équation après filtrage est la suivante :  $\frac{A^2G}{2} \times \cos \varphi$  C'est pour cela que l'on multiplie par 2 le signal et par la valeur maximal du signal d'entrée, c'està-dire A. Au final nous obtenons la valeur  $AG \cos \varphi$  correspondant à la partie continue du signal.

Pour réaliser le filtre, nous utiliserons la fonction FIR Compiler du MegaWizard d'Altera. Cette fonction est pratique pour pouvoir configurer facilement la fréquence de coupure et le nombre de coefficient.

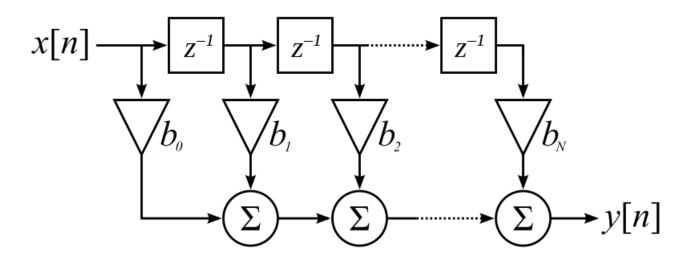

Un filtre FIR est un filtre à réponse impulsionnel fini, sont principe de fonctionnement est le suivant :

Figure 20: Structure quelconque d'un filtre FIR

#### 54506 VANDOEUVRE LES NANCY

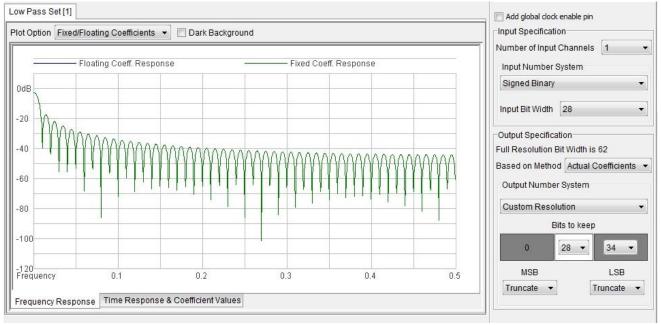

Le filtre que nous avons réalisé pour filtrer le signal à 500KHz est paramétré de la manière suivante :

- C'est un filtre passe bas

- Il possède 100 coefficients

- Sa fréquence de coupure est de 20KHz

- Sa fréquence d'échantillonnage est de 5 MHz

Figure 21: Réponse fréquentielle du filtre FIR

On peut observer que le signal est atténué de 35dB à 10% de la fréquence d'échantillonnage en lissant la courbe, ce qui dans notre cas est suffisant pour récupérer la valeur du signal continu. Mais ceci dit, il faudra tenir compte d'une légère atténuation du signal, de l'ordre de 2dB.

En pleine résolution, le signal de sortie du filtre est codé sur 62 bits ce qui donne une valeur de l'ordre de  $2 * 10^{18}$  ce qui n'est pas vraiment exploitable dans l'état.

Suite à une recherche sur le forum d'aide d'Altera, j'ai trouvé une formule permettant de réduire le nombre de bits en tronquant les bits de poids faible non nécessaire :

Nb bits =

$$\log_2\left((2^{28} - 1) \times \sum coefficients\right) = 27.53$$

Ce qui nous donne un total de 28 bits, ce qui revient à tronquer 34 LSB ( $2^{28} - 1$  correspond à la valeur maximal en entrée du filtre).

#### 54506 VANDOEUVRE LES NANCY

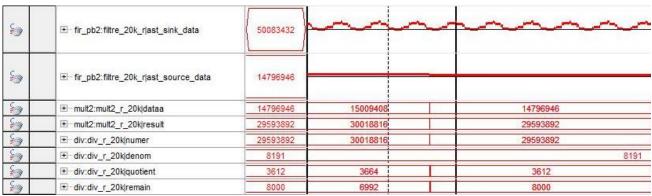

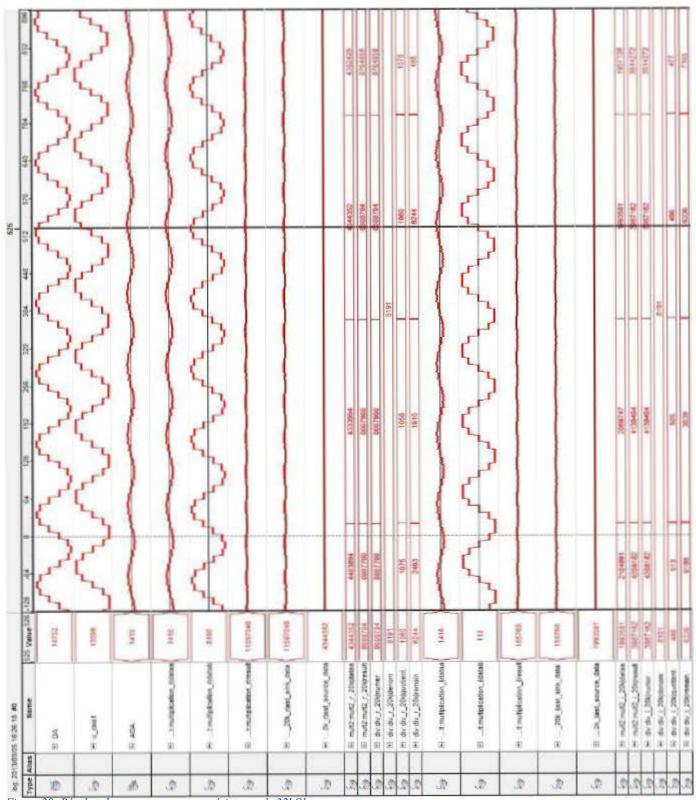

Ci-dessous se trouve les résultats du filtrage et des opérations suivantes.

Figure 22: Résultats du filtrage et des opérations permettant de récupérer la valeur correspondant à la partie réelle de l'impédance mesurée.

Nous pouvons constater que la valeur en sortie du filtre est continue sur plusieurs périodes. La suite des calculs est réalisée avec des fonctions simples (opérations mathématiques) qui ne sont pas nécessaire de présenter plus tard. Les résultats sont facilement démontrables de façon analytique.

Le signal finale correspondant à  $AG \cos \varphi$  est le signal nommé « div : div\_r\_20k|quotient ». Ici, il est calculé sans prendre en compte la baisse de niveau dans le continu du au filtre.

#### 54506 VANDOEUVRE LES NANCY

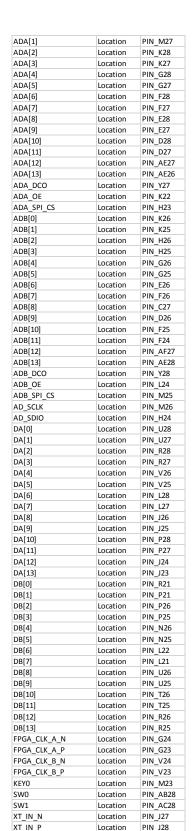

#### 3.4.6. Implémentation du projet sur la carte.

L'étape suivante est de mettre toutes ces fonctions sur la carte FPGA et la configurer de façon à ce qu'elle puisse générer des signaux de 500KHz et 5 MHz. Et qu'elle puisse effectuer les mesures et calculs pour les parties réels et imaginaires de ses fréquences. Ce qui implique de mettre 4 multiplieurs de 2 fois 14 bits en entrées et 28 bits en sorties, 2 filtres de fréquences de coupure de 20KHz, 2 filtres de fréquences de coupure 200KHz (il suffit de multiplier par 10 la fréquence d'échantillonnage et la fréquence de coupure), 4 multiplieurs par 2, et 4 diviseurs.

Divers switches et boutons ont été configurés pour gérer les reset des fonctions ainsi que le choix de la plage de fréquences et l'inversion de certains signaux en cas de besoins (voir annexes).

Les choix de fréquences ci-dessus nous permettent de ne pas utiliser de PLL.

Il a fallu aussi effectuer une table de correspondance entre la carte d'acquisition et la carte FPGA, celle-ci n'étant pas fournie par le constructeur. Il a fallu analyser les différentes documentations constructeur et en faire le lien (voir annexes).

Une fois tout cela effectuée, nous pouvons compiler le projet FPGA et voici le résultat de la compilation :

Flow Status Successful - Wed Sep 04 11:46:31 2013 13.0.0 Build 156 04/24/2013 SJ Full Version Quartus II 64-Bit Version Revision Name lockin\_amp Top-level Entity Name lockin\_amp Family Cyclone IV E Device EP4CE115F29C8 Timing Models Final 10,171 / 114,480 (9 %) Total logic elements 6,414 / 114,480 (6%) Total combinational functions Dedicated logic registers 9,050 / 114,480 (8 %) Total registers 9050 Total pins 76 / 529 (14 %) Total virtual pins 321,343 / 3,981,312 (8 %) Total memory bits Embedded Multiplier 9-bit elements 22 / 532 (4%) Total PLLs 0/4(0%)

Figure 23: Résultats de la compilation FPGA

Les différents choix effectués nous permettent d'utiliser qu'une petite partie des ressources du FPGA.

#### 54506 VANDOEUVRE LES NANCY

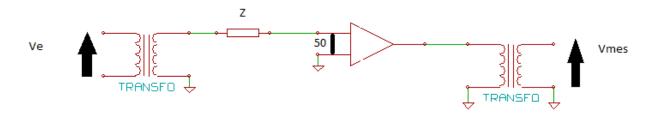

#### 3.4.7. Mesures d'impédances.

Figure 24: Schéma de la charge

Maintenant que la carte FPGA est configurée pour réaliser les mesures, nous allons effectuer des tests avec des résistances de  $12k\Omega$  et  $22k\Omega$ , symbolisé par la charge Z sur le schéma ci-dessus. Ici on aura configuré la résistance d'entrée de l'amplificateur à  $50\Omega$  et son gain G à 40dB (x100). Il nous donnera en sortie une image du courant traversant Z.

En négligeant les impédances des transformateurs et de la résistance d'entrée de l'amplificateur par rapport à l'impédance de Z, on peut estimer analytiquement la valeur de Z à partir de  $V_e$  et  $V_{mes}$ .

$$i_e = \frac{v_e}{Z + 50} \approx \frac{v_e}{Z}$$

$$v_{mes} = i_e \times 50 \times G$$

$$Z = \frac{v_e}{i_e} = \frac{v_e}{v_{mes}} \times 50 \times G$$

Maintenant nous allons tester le bon fonctionnement du projet FPGA. Vmes correspondra au signal ADA vu précédemment et Ve sera le signal en sortie du CNA. Pour les résultats voir annexes les figures 28 et 29.

Ici, pour les calculs nous appellerons 1/K le gain apporté par le filtre FIR comme vu précédemment et V<sub>out</sub> le signal de sortie du filtre une fois traité.

Pour retrouver l'impédance par rapport à la formule précédente on prendra  $V_{mes} = V_{out} \times K$ .

A partir de cela nous allons déterminer K.

Vout<sub>im</sub> et Vout<sub>re</sub> sont les valeurs des parties imaginaires et réelles

On a donc

$$V_{out} = \sqrt{Vout_{im}^2 + Vout_{re}^2}$$

Vu les résultats on a pour une résistance de  $22K\Omega$  et un gain de 100 on a Vout = 1211 (valeur interne au FPGA en nombre entier signé)

A partir de cette équation :  $|Z| = \frac{v_e}{v_{out} \times K} \times 50 \times G$  on peut déterminer K :

$$K = \frac{v_e \times 5000}{Z \times v_{out}} = 1.53$$

Vu les résultats on a pour une résistance de  $12K\Omega$  et un gain de 100 on a Vout = 2192 (valeur en INT)

A partir de cette équation :  $|Z| = \frac{v_e}{v_{out} \times K} \times 50 \times G$  on peut déterminer K :

#### 54506 VANDOEUVRE LES NANCY

$$K = \frac{v_e \times 5000}{Z \times v_{out}} = 1.55$$

En visualisant les deux résultats précédents on peut constater que K est constant donc on peut se permettre de dire que nous venons de caractériser le facteur K du filtre FIR ce qui donne une perte de -3.5 dB (20log<sub>10</sub> (1/K)).

Nous aurions pu essayer des mesures sur une impédance capacitive.

Pour la suite des calculs, pour caractériser l'impédance il faudrait appliquer un facteur de 50 x G/K.

### 4. Conclusion.

A partir d'une carte FPGA et d'une carte d'acquisition générique, nous avons pu réaliser un système spécifique de mesures d'impédances pour la caractérisation de cellules vivantes en régime dynamique en utilisant un outil de détection synchrone. Les caractéristiques de la chaine de mesure ont pu être modélisées et validées. Il nous permet effectivement de mesurer de faibles signaux bruités sur la plage de fréquence demandé. Ce qui nous permet de dire que ce dispositif est apte à caractériser les cellules.

Quelques imprévus et un manque de temps nous a empêché d'effectuer toutes les mesures et les fonctions souhaité. Effectivement nous aurions pu effectuer l'implémentation de la dernière partie des calculs ainsi que créer une interface PC-FPGA pour rapatrier les données.

Dans un avenir proche, ce travail pourrait servir de base pour la création d'un système compacte et autonome de mesure d'impédance avec l'association d'un capteur micro-fluidique.

| Figure 1 : Principaux composants du sang [5]                                                       | 6        |

|----------------------------------------------------------------------------------------------------|----------|

| Figure 2 : Modèle électrique d'une cellule et son schéma simplifié [1]                             | 6        |

| Figure 3 : Spectre électrique et diélectrique général d'une suspension de cellule                  | 7        |

| Figure 4 : Schéma d'un capteur micro-fluidique et d'un système de mesure par specti                | roscopie |

| d'impédance [1]                                                                                    | 8        |

| Figure 5: Schéma de la zone de mesure [6]                                                          | 8        |

| Figure 6: Variation de l'impédance lors du passage d'une cellule dans la zone de mesure            | 9        |

| Figure 7: Schéma de principe d'un système de mesure par détection synchrone                        | 10       |

| Figure 8: Schéma du système de mesure                                                              | 12       |

| Figure 9: résultats de la simulation                                                               |          |

| Figure 10 : Simulation de la PLL de 100Mhz sous ModelSim                                           | 14       |

| Figure 11: Première tentative de génération de sinusoïde                                           | 15       |

| Figure 12: Deuxième tentative de génération de sinusoïde                                           | 15       |

| Figure 13: Sinusoïde à 10 MHz mal capturée                                                         | 16       |

| Figure 14: Sinusoïde à 10MHz bien capturée                                                         | 16       |

| Figure 15: Sinus et sinus retardé de PI/2                                                          |          |

| Figure 16: Partie des spec. technique des transformateurs                                          |          |

| Figure 17: Aperçu des résultats de réception et de multiplication des signaux via SignalTa         | p Logic  |

| Analyzer                                                                                           |          |

| Figure 18: Pertes dans les transformateurs suivant la fréquence du signal                          | 20       |

| Figure 19: Signaux servant à la multiplication                                                     | 20       |

| Figure 20: Structure quelconque d'un filtre FIR                                                    | 21       |

| Figure 21: Réponse fréquentielle du filtre FIR                                                     |          |

| Figure 22: Résultats du filtrage et des opérations permettant de récupérer la valeur correspondent |          |

| la partie réelle de l'impédance mesurée                                                            |          |

| Figure 23: Résultats de la compilation FPGA                                                        | 24       |

| Figure 24: Schéma de la charge                                                                     |          |

| Figure 25: Equations sur les sinus                                                                 | 28       |

| Figure 26:Pin planer et le tableau associé                                                         |          |

| Figure 27: table de correspondance entre Carte mère et carte fille                                 |          |

| Figure 28: Résultat des mesures pour une résistance de 12kOhms                                     |          |

| Figure 29: Résultat des mesures pour une résistance de 22kOhms                                     | 32       |

#### 54506 VANDOEUVRE LES NANCY

### 5. Annexes.

#### Equations des deux signaux internes :

$$V \operatorname{int}_1 = A \sin(\omega t)$$

$$V \operatorname{int}_2 = A \sin(\omega t + \frac{\pi}{2})$$

#### Equations du signal mesuré:

$$V \text{ in} = AG \sin(\omega t + \phi) + b(t)$$

Avec G le gain du système (et des éventuels amplificateurs en entrées et sorties),  $\phi$  le déphasage par rapport au signal interne Vint<sub>1</sub>, et b(t) les bruits et perturbations.

#### Calcul réalisé en multipliant Vint<sub>1</sub> et Vin :

$$\begin{split} A\sin(\omega t). \big[ AG\sin(\omega t + \phi) + b(t) \big] \\ \frac{A^2G}{2} \big[ \cos(\omega t - \omega t + \phi) - \cos(2\omega t + \phi) \big] + A\sin(\omega t).b(t) \\ \frac{A^2G}{2} \cos(\phi) - \frac{A^2G}{2} \cos(2\omega t + \phi) + A\sin(\omega t).b(t) \end{split}$$

On obtient un signal avec une composante continue  $\frac{A^2G}{2}\cos(\phi)$  .

L'amplitude de la partie réelle du signal est déterminée après filtrage passe bas et division par A/2 :  $Re(Vin) = AG\cos(\phi)$ .

#### Calcul réalisé en multipliant Vint<sub>1</sub> et Vin :

$$\begin{split} &A\sin(\omega t + \frac{\pi}{2}).\left[AB\sin(\omega t + \phi) + b(t)\right] \\ &\frac{A^2B}{2}\left[\cos(\omega t - \omega t + \phi + \frac{\pi}{2}) - \cos(2\omega t + \phi + \frac{\pi}{2})\right] + A\sin(\omega t + \frac{\pi}{2}).b(t) \\ &\frac{A^2B}{2}\cos(\phi + \frac{\pi}{2}) - \frac{A^2B}{2}\cos(2\omega t + \phi + \frac{\pi}{2}) + A\sin(\omega t + \frac{\pi}{2}).b(t) \\ &-\frac{A^2B}{2}\sin(\phi) + \frac{A^2B}{2}\sin(2\omega t + \phi) + A\cos(\omega t).b(t) \end{split}$$

On obtient un signal avec une composante continue -  $\frac{A^2G}{2}\sin(\phi)$  .

L'amplitude de la partie imaginaire du signal est déterminée après filtrage passe bas et division par -A/2 :  $Im(Vin) = AG\cos(\phi)$ .

Figure 25: Equations sur les sinus

#### 54506 VANDOEUVRE LES NANCY

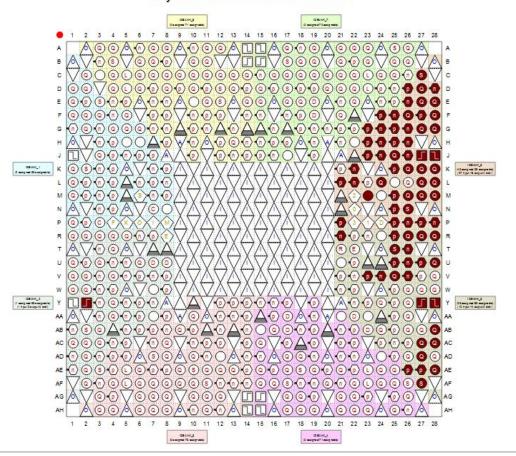

Top View - Wire Bond Cyclone IV E - EP4CE115F29C8

sw2

clk

sw3

Location

Location

Location

PIN\_AC27

PIN AD27

PIN\_Y2

Figure 26:Pin planer et le tableau associé

|                                  |                    |                                                                                                                  | HSMC                   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (1)                              | FPGA Pin           |                                                                                                                  | Connector              | i ai la licuc cimal             | WILL COMPANY OF THE PROPERTY O |

| gnal Name<br>SMC_RX_D_N[07]      |                    | Description LVDS RX bit 07n or CMOS I/O                                                                          | Pin Number Schem 92    | atic Signal HSMC Signal AD SCLK | Description2 Serial Port Interface Clock (Serial Port Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SMC_RX_D_N[07]                   | PIN_W26            | LVDS TX bit 07n or CMOS I/O                                                                                      | 91                     | AD_SCLK<br>AD_SDIO              | Serial Port Interface Clock (Serial Port Mod<br>Serial Port Interface (SPI) Data Input/Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MC_TX_D_N[05]                    | PIN_M28            | LVDS TX bit 05n or CMOS I/O                                                                                      | 79                     | ADA_D00                         | Data Output Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  | PIN_M27            | LVDS TX bit 05 or CMOS I/O                                                                                       | 77                     | ADA_D01                         | Data Output Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SMC_TX_D_N[04]                   |                    | LVDS TX bit 04n or CMOS I/O                                                                                      | 73                     | ADA_D02                         | Data Output Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_P[04]                   | PIN_K27            | LVDS TX bit 04 or CMOS I/O                                                                                       | 71                     | ADA_D03                         | Data Output Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_N[03]                   | PIN_G28            | LVDS TX bit 03n or CMOS I/O                                                                                      | 67                     | ADA_D04                         | Data Output Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_P[03]                   | PIN_G27            | LVDS TX bit 03 or CMOS I/O                                                                                       | 65                     | ADA_D05                         | Data Output Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_N[02]                   | PIN_F28            | LVDS TX bit 02n or CMOS I/O                                                                                      | 61                     | ADA_D06                         | Data Output Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_P[02]                   |                    | LVDS TX bit 02 or CMOS I/O                                                                                       | 59                     | ADA_D07                         | Data Output Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_N[01]                   |                    | LVDS TX bit 01n or CMOS I/O                                                                                      | 55                     | ADA_D08                         | Data Output Bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SMC_TX_D_P[01]                   |                    | LVDS TX bit 01 or CMOS I/O                                                                                       | 53                     | ADA_D09                         | Data Output Bit 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SMC_TX_D_N[00]<br>SMC_TX_D_P[00] | PIN_D28<br>PIN_D27 | LVDS TX bit 00n or CMOS I/O<br>LVDS TX bit 00 or CMOS I/O                                                        | 49<br>47               | ADA_D10<br>ADA_D11              | Data Output Bit 10 Data Output Bit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |