# Modeling and verification of natural language requirements based on states and modes

Yinling Liu, Jean-Michel Bruel

# ▶ To cite this version:

Yinling Liu, Jean-Michel Bruel. Modeling and verification of natural language requirements based on states and modes. Formal Aspects of Computing, inPress, 10.1145/3640822. hal-04446384

# HAL Id: hal-04446384 https://hal.univ-lorraine.fr/hal-04446384

Submitted on 8 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Modeling and Verification of Natural Language Requirements based on States and Modes

YINLING LIU\*, CRAN, CNRS, Université de Lorraine, Nancy, France JEAN-MICHEL BRUEL, IRIT, CNRS, Université de Toulouse, Toulouse, France

The relationship between states (status of a system) and modes (capabilities of a system) used to describe system requirements is often poorly defined. The unclear relationship could make systems of interest out of control because of the out of boundaries of the systems caused by the newly added modes. Formally modeling and verifying requirements can clarify the relationship, making the system safer. To this end, an innovative approach to analyzing requirements is proposed. The MoSt language (a Domain Specific Language implemented on the Xtext framework) is firstly designed for requirements modeling and a model validator is realized to check requirements statically. A code generator is then provided to realize the automatic model transformation from the MoSt model to a NuSMV model, laying the foundation for the dynamic checks of requirements through symbolic model checking. Next, a NuSMV runner is designed to connect the NuSMV with the validator to automate the whole dynamic checks. The grammar, the model validator, the code generator, and the NuSMV runner are finally integrated into a publicly available Eclipse-based tool. Two case studies have been employed to illustrate the feasibility of our approach. For each case study, we injected 14 errors. The results show that the static and dynamic checks can successfully detect all the errors

CCS Concepts: • Software and its engineering  $\rightarrow$  Domain specific languages; • Theory of computation  $\rightarrow$  Verification by model checking.

Additional Key Words and Phrases: states and modes, requirements modeling and verification, domain specific language, model checking

#### 1 INTRODUCTION

The ambiguity between states and modes threatens the safety of complex systems. If there is a problem during the development of the system, the Engineering mindset would possibly be to add one capability to prevent another capability or a scenario from occurring [39]. These capabilities have their limitations and could cause a system to fail because the values of variables exceed the thresholds of the system boundary. Thus, we need to know clearly the capabilities and the boundaries of the system. People tend to describe capabilities by using modes and states. For example, they could say that the aircraft is either in mode *taxi* or in state *taxi*. Here we argue *modes* and *states* represent the capabilities and the boundaries of the system, respectively. Indeed, it works well most of the time. However, if the system is becoming more and more complex, the described capabilities and boundaries should be more precise. The ambiguity between capabilities and boundaries has a negative impact on commanding, controlling, and monitoring the system, which finally may lead to catastrophe in reality.

For instance, the recent Boeing 737 MAX crashes caused many deaths. The summary report from the U.S. Federal Aviation Administration shows that one of the problems was that the control system read the wrong

Authors' addresses: Yinling LIU, yinling.liu@univ-lorraine.fr, CRAN, CNRS, Université de Lorraine, Campus Sciences BP 70239 54506, Vandœuvre-lès-Nancy, Nancy, France, 54506; Jean-Michel BRUEL, jean-michel.bruel@irit.fr, IRIT, CNRS, Université de Toulouse, Cr Rose Dieng-Kuntz, Toulouse, France, 31400.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2024 Copyright held by the owner/author(s). Publication rights licensed to ACM. ACM 0934-5043/2024/2-ART https://doi.org/10.1145/3640822

angle of attack (AOA, which refers to the angle between the aircraft forward direction and the wing chord)<sup>1</sup>. The plane was supposed to ascend while, in fact, it was descending. The pilot could not take back the control of the plane, which finally gave rise to these catastrophes. To solve the problem, Boeing changed flight control laws to include a limit for MCAS (Maneuvering Characteristics Augmentation System) commands so that the MCAS will stop commanding stabilizer movement at a point that preserves enough elevator movement for sufficient pilot control of aircraft pitch attitude for current operation conditions. Boeing also added the second AOA sensor to be capable of alerting pilots that there is a problem for AOA sensors. If we analyze this example from the viewpoint of states and modes, the problem could be that when the plane is in mode *automated* and state *descending*, and we change the mode into *manual*, the plane cannot leave *descending* state to *ascending* state. If the states and modes of the plane were sufficiently addressed, the impact of modes on system behaviors would have been investigated. These catastrophes may have been avoided. This example illustrates that the boundaries, capabilities, and their relationships should be as precise as possible to keep the system safe. Therefore, the distinction of modes and states clarifies the capabilities and boundaries of the system, which helps improve the safety of complex systems.

The terms *states* and *modes* are widely used in expressing systems requirements [15–17, 34]. However, little guidance has been proposed to distinguish states and modes. As Wasson said, "System modes and states are perhaps one of the most controversial topics in Engineering and SE. Every industry, profession, Enterprise, and Engineer has their own view as to what a mode and a state are." [39]. That is the reason why we are so motivated to model and verify the natural requirements based on states and modes.

Various aspects have been emphasized to analyze requirements, including context [1, 2], the failures and successes of other requirements [37], and requirements evolution [40]. However, to the best of our knowledge, no one performs the modeling and verification of requirements based on states and modes. The requirement analysis benefits a lot from the proper usage of states and modes. They enable us to describe requirements that exist outside the normal operating environment [34]. They also aid in translating the user's version into the physical realization of the system [38]. They can be used as a medium to reduce misunderstandings between stakeholders such as users, acquirers, and developers as well [18].

Domain Specific Languages (DSLs) are programming languages or specification languages that target a specific problem domain [6]. When the domain of a problem is covered by a particular DSL, we will solve that problem in an easier and faster way via using that DSL rather than a general-purpose language like Java or C, etc. In our case, we aim to create a new DSL to assist users to write requirements in a controlled natural language. In this way, requirements can be better organized, expressed, and understood. On the other hand, writing requirements in natural languages is easier and more acceptable for stakeholders.

Proper DSLs are helpful in writing "correct" requirements. They are just the requirements that satisfy syntactic and validator rules. Validator rules are user-defined. For example, naming rules of the elements in requirements can be defined in the validator then the requirements can be checked by the defined naming rules. However, several problems remain unsolved. For instance, how to check the internal logic between requirements? How to verify the satisfiability of property specifications regarding systems? To solve these problems, the symbolic model checking technique can further improve the quality of the written requirements. This technique is capable of demonstrating the correctness of system behaviors. The problem of model checking is formally expressed by  $M \models \varphi$ , where M represents the system model,  $\varphi$  is a property, and  $\models$  is the satisfiability symbol to check whether the model M satisfies the property  $\varphi$ . If the property is not satisfied by the system, a counterexample is produced. NuSVM² is a symbolic model checker designed to allow for the description of Finite State Machine (FSM), which ranges from completely synchronous to completely asynchronous, and from the detailed to the abstract on [11]. The primary purpose of the NuSMV input language is to describe the transition relation of the

$<sup>^{1}</sup> https://www.faa.gov/foia/electronic\_reading\_room/boeing\_reading\_room/media/737\_RTS\_Summary.pdf \ (accessed in July 2022) \\ - (1.5) a constant of the property of the pr$

<sup>&</sup>lt;sup>2</sup>https://nusmv.fbk.eu/ (accessed in April 2023)

FSM, which is quite suitable for describing the state information in requirements. Therefore, in this paper, we choose NuSMV as the model checker.

This work is based on our previous work [30]. Our previous work mainly focuses on the design of MoST modeling language and static checks of MoST models. The present work significantly extends our previous work

- Proposing an innovative framework fully supporting the modeling and verification of requirements based on states and modes;

- Accomplishing algorithms to automatically perform the model transformation from MoST models to NuSVM models:

- Developing a NuSMV runner to realize a seamless connection between the NuSMV model checker and validator, automating the dynamic checks including the traceability, reachability, and validation analysis;

- Developing another case study to illustrate the feasibility of our approach;

- Implementing an Eclipse-based tool to enable us to write the MoST model, generate the NuSMV model, and conduct the static and dynamic requirement analyses.

Based on the tool, requirements engineers can use MoST modeling language to formalize requirements, so as to better organize, accurately express, and effectively manage requirements. The extracted information on states and modes can serve as "standard" terms when team members communicate with each other. Note that we suppose states and modes have already been underlined in requirements documents. So, conflicts on the system description can be reduced. In addition, clients can be encouraged to expect the most suitable performance of the future systems since the MoST language supports the description of the property specifications in CTL and LTL logics, and these specifications can be automatically verified.

The remainder of this paper is structured as follows. Section 2 reviews the main related work. Section 3 introduces the framework for requirements analysis and presents all the elements about how to design the MoST modeling language. Section 4 realizes the algorithms to perform the model transformation from the MoSτ model to the NuSMV model. Section 5 provides an approach to verifying requirements. Section 6 gives a systematic evaluation of our approach to illustrate its feasibility. Section 7 concludes the paper with future perspectives.

#### 2 LITERATURE REVIEW

In this section, we will first review the existing definitions of states and modes. Then, we will provide important insights into the work on requirements modeling and verification.

#### 2.1 States and Modes

This section provides a literature review on the definition of states and modes. As one of our purposes is to differentiate states and modes, we exclude the references [13, 16-18] which are self-inconsistent in terms of the description of states and modes. For example, DI-IPSC-81431A (2000) [16] offers the following guidance: The distinction between states and modes is arbitrary. A system may be described in terms of states only, modes only, states within modes, modes within states, or any other scheme that is useful. Edwards (2003) [18] shares similar ideas about the relationship between states and modes. Obviously, this guidance creates more conflicts in differentiating states and modes. On the other hand, DMO (2011) [17] provides an example of a state transition diagram that does not depict any states at all. The synthesis analysis of the reviewed references is concluded in Table 1. A set of aspects have been proposed to analyze the definitions of states and modes, including state (information, abstraction level, conditions, capabilities, dynamics, constraints) and mode (abstract concept, abstraction level, conditions, capabilities, dynamics, objectives). It should be noted that abstract concept and abstraction level are different. The former implies denoting an idea of a thing rather than a concrete object; the latter implies the different levels in analyzing the system of interest, for example, system/subsystem/component. The aspect capabilities means a set of functions the

system can perform. The aspect *conditions* addresses the conditions that have an impact on system behaviors, for example, physical/environmental conditions. Furthermore, "involved" means the term has been just mentioned without any other details.

According to this table, the concepts of states and modes had been widely used from 2000 to 2010. However, it seems that researchers didn't pay enough attention to the difference between them. For example, Andrey (2002); Feiler, Lewis, and Vestal (2006) [3, 20] have simply emphasized states and modes respectively. Since 2010, the issue of the difference between states and modes has been gradually addressed, but opinions on states and modes still vary from person to person. In terms of states, researchers principally concentrate on the aspects of *conditions*, *dynamics* and *constraints*. They focus less on *information* and *abstraction level*. The aspect of *capabilities* is seldom addressed. When comparing states with modes, *capabilities*, on the contrary, is the most important aspect in defining modes. Researchers are also concerned with *abstraction level*, *conditions*, *dynamics* and *objectives* for modes. It seems that they do not care whether "mode" is an abstract concept or not. This analysis aids us in gaining important insights into the meaning of states and modes, which lays the foundation for designing a DSL containing these two concepts.

Table 1. An Overview of the Definitions of States and Modes where "-" and "NM" means "Not included" and "Not Mentioned", Respectively

| [3]                                | [14]                          | [20]                        | [15].                      | [26]                              | [38]                                  | [27]                            | [8]                   | [7]                          | [5]                            |

|------------------------------------|-------------------------------|-----------------------------|----------------------------|-----------------------------------|---------------------------------------|---------------------------------|-----------------------|------------------------------|--------------------------------|

| State informationan<br>ob-<br>ject | NM                            | -                           | NM                         | variables,<br>system              | system                                | NM                              | involved              | NM                           | type of in<br>formation        |

| abstractionNM<br>level             | system,<br>subsys-<br>tem     | -                           | system,<br>subsys-<br>tem. | NM                                | element,<br>subsys-<br>tem,<br>system | NM                              | NM                    | NM                           | relates to<br>informa-<br>tion |

| conditions NM                      | system<br>condi-<br>tions     | -                           | system<br>condi-<br>tions  | a condi-<br>tion to a<br>behavior | performan<br>physical                 | c <b>o</b> perating             | a set of<br>metrics   | operating,<br>physical       | involved                       |

| capabilitiesNM                     | involved                      | -                           | NM.                        | multiple<br>functions             | involved                              | NM                              | involved              | NM                           | NM                             |

| dynamics NM                        | NM                            | -                           | involved                   | NM                                | involved                              | state tran-<br>sition           | state tran-<br>sition | state tran-<br>sition        | involved                       |

| constraintstime,                   |                               |                             | time                       | NM                                | involved                              | NM                              | time                  | environment                  | time                           |

| Mode abstract -<br>concept         | NM                            | detailed                    | involved                   | NM                                | abstract<br>label                     | NM                              | NM                    | NM                           | abstract                       |

| abstraction-<br>level              | NM                            | system,<br>subsys-<br>tem   | sub-<br>mode               | NM                                | system,<br>product,<br>service        | top,<br>lower                   | NM                    | NM                           | link to ca<br>pabilities       |

| conditions -                       | system<br>condi-<br>tions     | specific<br>condi-<br>tions | NM                         | NM                                | triggering<br>events                  | a condi-<br>tion of a<br>system | NM                    | specific<br>condi-<br>tions  | invariant<br>condi-<br>tions   |

| capabilities                       | multiple<br>capabili-<br>ties | NM                          | operation                  | s multiple<br>capabili-<br>ties   | use case                              | multiple<br>capabili-<br>ties   | operations            | specific<br>function-<br>ing | multiple<br>capabili-<br>ties  |

| dynamics -                         | NM                            | mode<br>transi-<br>tion     | mode<br>transi-<br>tion    | NM                                | mode<br>transi-<br>tion               | NM                              | NM                    | mode tran-<br>sition         | mode tran                      |

| objectives -                       | function                      | NM                          | NM                         | NM                                | mission                               | NM                              | function              | expected<br>behavior         | expected<br>behavior           |

### 2.2 Requirements Modeling and Verification

The requirements analysis has been recognized as the first phase of the system development process [36]. The later errors in the requirements are discovered, the higher the system development costs. Hence, the importance of requirements modeling and verification has been well addressed in systems and software engineering. A considerable amount of work on how to model and verify requirements has been performed. Numerous approaches have been proposed to improve the quality of requirements, including designing a new language, using a goalbased model, manipulating and implementing tools, etc. In the following, we report on a comprehensive analysis of the literature in a chronological way.

Leveson et al. (1994) [29] develop a Requirements State Machine Language (RSML) to describe requirements of real-time process control systems via a combination of graphical and tabular notations. The graphical notation of RSML is principally derived from Statecharts [23]. A number of definitions have been mentioned in RSML, including Interface, Input, Output, Transition, Macro and Function. The tables in RSML describe the conditions under which the corresponding state transitions can happen. Indeed, they analyze requirements from the viewpoint of states but their way of expressing requirements complicates requirements analysis. Specifications in RSML include graphical, symbolic, tabular, and textual notations. Even though more aspects of the systems can be addressed via its notations, it seems that it is impossible to verify requirements (static and dynamic verification) in an automatic way.

Heitmeyer, Jeffords, and Labaw (1996) [24] demonstrate the feasibility of formal methods for requirements modeling and analysis via three case studies. They choose different formal methods for the requirements of different case studies. They have successfully detected errors in requirements, thanks to requirements modeling, testing, verification, and initial human reading. Even though a number of errors have been identified, this work is done by experts in formal methods. Their approach requires a lot of knowledge in formal methods, which limits its use. In addition, they suggest "A system state is a function that maps each entity name r in RF to a value" and "RF is a set of entity names. RF is partitioned into four subsets: MR, the set of mode class names; IR, the set of input variable names; GR, the set of term names; and OR, the set of output variable names". It seems that system states include modes. The relationship between states and modes is not mentioned. The principles of SCR and our DSL are different. We think modes in [24] are just one aspect statically describing system states. While modes in our paper actively influence system states by changing values of attributes.

Goldsby et al. (2008) [22] analyze requirements from the viewpoint of four types of developers: the system developer, the adaptation scenario developer, the adaptation infrastructure developer, and the dynamically adaptive system. They use i\* goal models [41] to describe the requirements of different types of developers. They detail the viewpoint of the developer for requirements analysis, but the graphic representation of requirements is not easy to be formally verified. The graphic representation of requirements is informal. Transforming informal models into formal ones usually necessitates a lot of effort to ensure that the core information is captured in the formal models.

Mavin et al. (2009) [31] focus on the problem of how to design a structured natural language to improve the quality of requirements written by stakeholders. For this purpose, they develop five specific Easy Approach Requirements Syntax (EARS) templates to facilitate requirements expression. The results of their case study show qualitative and quantitative improvements compared with a conventional textual requirements specification. However, they only focus on how to express requirements in a better way. The requirements analysis concerning conflicting requirements and traceability links, etc., is missing.

Silva Souza et al. (2011) [37] present a new type of requirements called AW (Awareness Requirements). The requirements are associated with other requirements and their success/failures, constituting requirements for such feedback loops. They formalize AW by a variant of OCL (Object Constraint Language) called  $OCL_{TM}$  and validate them using a monitoring framework. Since the modeling process with  $OCL_{TM}$  is not a trivial task, they provide AW patterns and graphic representation to facilitate the elicitation and analysis of AW. However, in our case, we consider the facility of eliciting requirements by creating our own modeling language directly.

Requirements uncertainty has been studied in certain works. Some focus on uncertainty, assuming all the uncertain conditions are unknown and enumerated at design time [22, 28]. Some address that some uncertain conditions are still unanticipated [40]. Whittle et al. (2009) [40] design a new requirements specification language called RELAX to explicitly emphasize uncertainty without knowing all the uncertain conditions. RELAX is based on FBTL (Fuzzy Branching Temporal Logic), which can describe a branching temporal model with uncertain temporal and logical information. So, its expressive power on uncertainty is stronger than in some other languages. The idea of designing a DSL to write certain requirements is similar to ours, but we are not specifically concentrated on requirements uncertainty.

Badger, Throop, and Claunch (2014) [4] argue that a simple way to improve the quality of requirements written at various levels by different groups of people would be to standardize the design process using a set of tools and widely accepted requirements design constraints. They make full use of appropriate tools to realize the automatic requirements elicitation, formalization, analysis, and verification. However, they do provide us with a concrete case study. The limits of used tools have not been discussed.

Ahmad, Belloir, and Bruel (2015) [1] propose a model-based requirement modeling and verification process for addressing uncertainty in the requirements of self-adaptive systems. They combine the proposed language RELAX with the concepts of Goal-oriented Requirements Engineering for requirements eliciting and modeling. Since various tools have been used like RELAX editor, SysML/KAOS, and OMEGA2, requirements traceability is not sufficiently emphasized.

Carvalho et al. (2016) [9] investigate how to generate SCR specifications from controlled natural language requirements. We would argue that the concept "mode" is different from ours. It seems that they just mix the concepts of "state" and "mode". For example, the vending machine example in their paper says "After a coin is inserted, the system switches from *idle* to *choice* states.". This change is represented by changing the value of the signal mode from 1 to 0. It seems that 0 and 1 modes are the aliases for idle and choice states. However, in our paper, the modes show the capabilities of the system instead of representing the states of the system.

Moitra et al. (2019) [32] implement a tool ASSERT<sup>TM</sup> to perform requirements modeling and verification. The requirements are captured by a structured natural language and formal analysis is based on an automated theorem prover. They conduct a set of formal requirements analyses, including completeness analysis. The completeness analysis of ASSERT<sup>TM</sup> is simply involved with values of monitored variables and all pairs of values for controlled variables. They do not consider the reachability of all states of a system. On the other hand, their viewpoint of analyzing requirements is dependent on data instead of states and modes.

Recently, Nalchigar, Yu, and Keshavjee (2021) [33] are interested in machine learning requirements (the processes for requirements elicitation, design, and development involve machine learning). They analyze these requirements from the viewpoint of businesspeople, data scientists, and data engineers. They use the case study method to perform requirements modeling. This method consists of providing an overview of the framework, constructing and revising business, analytic design and data preparation view models, and post-modeling interviews and interpretation. Their approach is suitable for testing theories and artifacts in complex settings, however, it is principally a manual approach, which is difficult to be sufficiently validated.

Giannakopoulou et al. (2021) [21] present a compositional approach to generating and verifying the formalization of structured natural language. They develop a Formal Requirements Elicitation Tool (FRET) to write, understand, formalize and analyze requirements. They also develop an automated verification framework for the fmLTL (future-time LTL) and pmLTL (past-time LTL) formulas. Their work seems to be very close to our work. We both use the controlled natural language to describe requirements. We both use NuSMV to verify requirements. However, our work is quite different from their work. First, they do not focus on modes and states. They are particularly interested in defining the temporal logic of requirements. Secondly, the purpose of using NuSMV

for them is to check the satisfiability of a single requirement against the temporal properties. They also use EQUIVALENCE CHECKER to check the consistency between different formalizations of the same template key. They basically check the truth of every single requirement. In our case, we check the satisfiability of every single requirement by static checking. We check not only the formats of requirements but the context of requirements (static relationship between requirements, for example, when a variable of a requirement has not been defined, the suggestion of defining this variable-related requirement will be proposed.); Thirdly, their verification does not involve dynamic checking. We check the internal logic between requirements by the NuSMV simulation.

Clearly, a majority of work focuses on how to design a new language to facilitate requirements analysis. The new languages proposed include RSML, EARS,  $OCL_{TM}$ , RELAX, FRET, etc. Most of the languages are dedicated to better requirements eliciting and verification. Different viewpoints of analyzing requirements have been considered, including developers [22], uncertainty [1, 40], awareness requirements [37], machine learning requirements [33], etc. Some other researchers are also concentrated on data warehouse requirements [19, 42]. To the best of our knowledge, none of the work analyzes requirements from both users and developers. In other words, the viewpoint of states and modes has not been sufficiently addressed in analyzing requirements. This may lead to misunderstandings between users and developers, which can cause conflicts in systems validation. Inconsistency could happen in development teams as well, which gives rise to conflicts in system design. As a result, we are so motivated to conduct requirements analysis from the viewpoint of states and modes.

#### THE MOST MODELING LANGUAGE

In this section, we will first present the framework for modeling and verifying natural language requirements based on states and modes. Then, we will discuss our proper definitions of states and modes and their relationship in detail. Next, the meta-model of MoST will be provided to explain the key concepts in the language. Finally, the MoST grammar will be given.

#### Our Analysis Framework

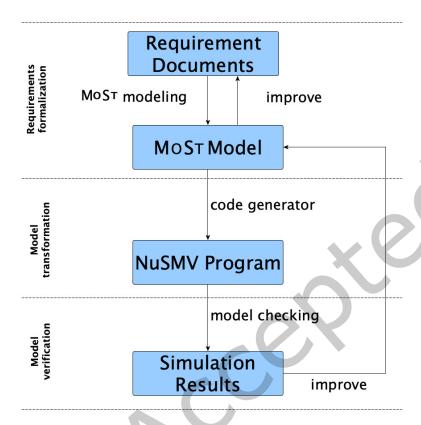

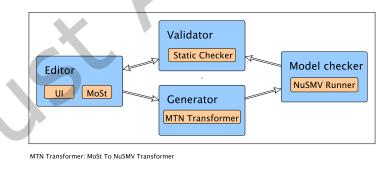

This framework (Fig. 1) aims to explain our approach to modeling and verifying requirements. Three steps are involved, including requirements formalization, model transformation, and model verification. In the first step, we will design a DSL called MoST to formalize requirements from requirements documents. Meanwhile, a code validator is implemented to impose static rules on this language so that requirements can be statically checked in the MoST editor. In the second step, a code generator will be accomplished to automatically realize the model transformation from the MoST model into the NuSMV model. This step provides the foundation for dynamically checking requirements. The last step is to conduct model verification. The errors or counter-examples proposed by the model checker will be traced back to the MoST model. Thus, we can improve the quality of requirements with the information proposed by the model checker.

Our framework for requirements modeling and verification clarifies the value of our work. Firstly, it offers a general approach to integrating states and modes into requirement modeling and verification in the early phase of system design. System designers who are accustomed to using terms like states and modes will benefit from this work because the relationship between states and modes will be precisely explained. Secondly, system designers who are intended for getting a sense of what the future system will look like will profit from this work because it enables the investigation of how modes will influence the system behaviors. Finally, it allows system designers to better communicate with clients since "mode" is a common term that is easier to be accepted by clients when discussing specific needs.

As mentioned in Section 1, the requirements of designing a car are analyzed as a case study. They are inspired from Dusan Rodina<sup>3</sup>. Since few engineers analyze requirements from our perspective, it is not easy to find the

<sup>&</sup>lt;sup>3</sup>https://www.softwareideas.net/a/1539/Car-States--UML-State-Machine-Diagram- (accessed in April 2023)

Fig. 1. Framework for Modeling and Verifying Natural Language Requirements based on States and Modes

existing requirements without reformulating them. We think this will not hinder the applicability of the proposed strategy for requirements verification. The proposed strategy can be used to describe requirements as generally as possible. It requires that users need to pay attention to the concepts of states and modes. Indeed, it will constrain a little the way we express requirements, but it gains more clarity and reduces ambiguity. Additionally, states and modes are sometimes intertwined in requirements, which makes it difficult to use the existing requirements. Thus, we finally choose to design our proper requirements that are based on the correct logic. These requirements will be considered in the following requirements modeling and verification activities.

#### 3.2 Relationship between States and Modes

The relationship between states and modes has been discussed in the literature. For example, the explanation of Edwards [18] may be confusing, but the example on the relationship between states and modes implies modes control states. In other words, modes can actively influence system states. Modes show capabilities. While states are changed when conditions are satisfied. It seems that Wasson [39] shares the same idea. He argues states are observable and measurable physical attributes of a system or entity. It means states represent the attributes of a system or entity. And he suggests modes enable us to accomplish objectives that produce results you can observe

and measure. The activeness of modes is again recognized. The characteristics of modes and states are the basis for us to propose the relationship between them.

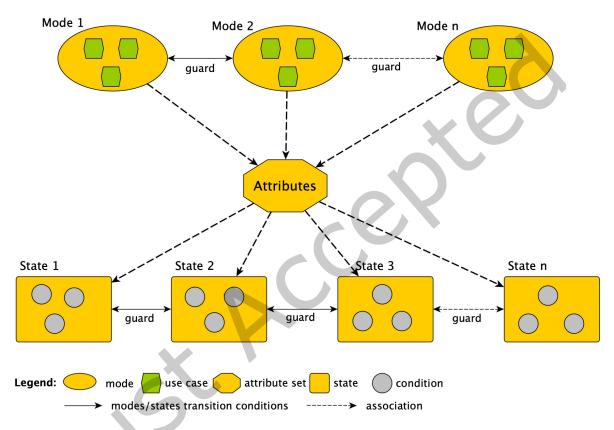

In this paper, we propose our proper definitions of modes and states. We argue modes are the abstraction of use cases as mentioned by [39]. Modes transitions happen when the corresponding signals from the system are received. Modes own capabilities to change the values of certain attributes. The values of these attributes are ones of conditions inside states. States hold certain conditions. States transitions happen when the corresponding conditions are satisfied. Fig. 2 illustrates the relationship between states and modes.

Fig. 2. The Relationship between States and Modes

#### 3.3 MoSт Meta-model

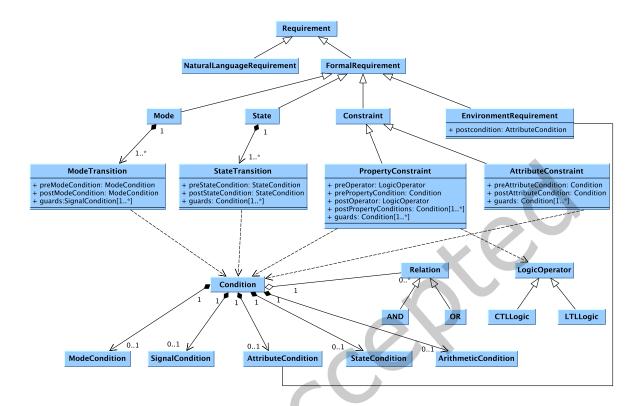

The MoST meta-model highlights the properties of the MoST Modeling Language. As shown in Fig. 3, MoST is capable of describing NLRs and formal requirements. Even though formal requirements are also modelled by the natural language, this natural language should conform to certain rules. The NLRs enable us to capture the important information from the requirement documents as much as possible, in order to serve traceability in case of troubleshooting. Note that extracting important information from free natural languages is out of our scope.

MoST focuses on describing functional requirements non-functional requirements. MoST-based formal requirements consist of concepts *Mode*, *State*, *Constraint* and *EnvironmentRequirement*. The reason why we need to introduce the last two concepts is that the MoST model is supposed to support formal verification. This idea

Fig. 3. The MoST Meta-model

demands that the MoST model must be self-contained to make it verifiable. The concepts of *Mode* and *State* describe functional requirements. The *Constraint* concept describes functional and non-functional requirements. More specifically, the concept *PropertyConstraint* depicts functional and non-functional requirements to be checked. On the other hand, *EnvironmentRequirement* concept initializes values and ranges of system attributes.

Concept *Constraint* aims at constraining attributes mentioned in requirements and providing property specifications to be checked in formal analysis.

Concept Condition is one of the most important concepts in this meta-model, which includes conditions Mode-Condition, StateCondition, AttributeCondition, SignalCondition, ArithmeticCondition, and Relation. Concept Relation is used to enrich the expressive power of MoST, which enables guards to be any combination of conjunctions, disjunctions, and conjunctions and disjunctions of specific conditions. However, concepts of ModeTransition and EnvironmentRequirement are exceptional, which are directly associated with specific conditions. The reasons have been mentioned in Section 3.2.

Concept *LogicOperator* describes two temporal logics: the logics *CTLLogic* (Computational Tree Logic) and *LTLLogic* (Linear Temporal Logic). The introduction of the concept *LogicOperator* lays the foundation for formally verifying requirements based on states and modes.

Additionally, environment requirements include only post-conditions because they are used to state the initial statuses of variables where preconditions are not needed.

Form. Asp. Comput.

#### 3.4 MoSt Grammar

A grammar is a set of rules that describe the form of the elements that are valid according to the language syntax [6]. The MoST grammar defines the rules describing how to write different types of requirements. The complete grammar is shown in the annex (Figs. 23 - 27). Every rule contains a name, a colon, a syntactic form, and a semicolon. The first rule of the grammar defines where the parser starts and the type of the root element of the MoSt model is MoSt. The shape of MoSt elements is expressed in its own rule:

*MoSt:* models+=(Requirement | NLRequirement)\*;

A collection of Requirement or NLRequirement elements are stored in feature models of a MoSt object. Formal requirements are stored in Requirement objects. NLRs are stored in NLRequirement objects. Note that += and \* operators mean it is a collection and the number of elements is arbitrary respectively. Here, the collection is implemented as a list. The star operator \* means that the number of the elements can be any number >=0. The grammar of MoSt is not presented using the classical BNF (or EBNF) notation but using the syntax of Xtext since it is more understandable if interested readers would like to reproduce this work. Interested readers can also get details from [6].

3.4.1 Natural Language Requirements. The natural language requirement rule is illustrated as follows: NLRequirement: nlReqID=ReqID ID (ID)\* '.';

RegID:'['regID+=INT('.'regID+=INT)\*']';

It implies that NLRs begin with the ReqID (the identity of requirements) like "[1.2.3...N]". So this naming rule of RegID signifies there is no limit to the number of NLRs. This rule applies to all the other requirements as well. As for ID, there is no rule defining it because that is one of the rules from the Terminals (mentioned in Xtext). It allows us to write any words as we want. As a result, the rule of NLRs is just to write natural language sentences with identifiers.

3.4.2 Formal Requirements. Formal requirements include ENVIRONMENT, MODE, STATE, ATTRIBUTECON-STRAINT, and PROPERTYCONSTRAINT. The rule of formal requirements is represented as follows: Requirement: ENVIRONMENT | MODE | STATE | ATTRIBUTECONSTRAINT | PROPERTYCONSTRAINT;.

Two generic templates are used including "when ..., then ..." and "... should be ...". The first template applies to mode, state, attribute constraint, and property constraint requirements. The second template applies to environment requirements. The first one implies when pre-conditions of the systems are satisfied, then the system can get the post-conditions satisfied. The idea is basically from Hoare Triple logic [25]. That is why we would like to use different kinds of specific conditions to define pre-conditions, post-conditions. Our template is similar to one of the EARS templates "WHEN <optional preconditions> <trigger> the <system name> shall <system response>" [31]. We argue "when ..., then ..." can express all the templates mentioned in their work in an abstract way because we think pre-conditions can express the characteristics of all their templates including ubiquitousness, events, unwanted behaviors, states, and optional features. A ubiquitous requirement in EARS template has no precondition or trigger. Property constraint requirements can describe ubiquitousness. For example, the CTL formula "AG! engineSpeed > x" represents that the control system shall prevent engine overspeed. Optional features can be simply recognized as conditions. The other characteristics are naturally supported by the first template. The second template declares constraints for variables, which are suitable for describing environment requirements. Besides, this mapping illustrates the expressive power of MoST.

#### 1). Environment Requirements

Environment requirements are dedicated to describing initial statuses of variables, including the initialized values and the ranges of variables. That is why the rules of these requirements involve ATTRIBUTEVALUE, UNIT and *RANGE*. The rule of environment requirements is shown as follows:

#### **ENVIRONMENT:**

envirReqID=ReqID ID envirVariable=ID (ID)\* (('initialised' 'to' envirAttributeValue=ATTRIBUTEVALUE envirUnit=UNIT | range=RANGE)) (ID)\* '.';

In terms of *ATTRIBUTEVALUE*, three common data types are employed, including *INT*, *String* and *Boolean*. As for *UNIT*, the units of weight, time, speed, and accelerate speed are applied. The rule of *RANGE* indicates the lower and upper bounds for the variables. This rule concerns the comparison operators, which limit the bounds and include *GREATER*, *GREATEREQUAL*, *LESS*, and *LESSEQUAL* rules. The details of the rules *ATTRIBUTEVALUE*, *UNIT*, *RANGE*, and *COMPARISONOPERATOR* are shown in Figs 25 and 27. Note that *ID* is predefined in Xtext framework as terminal ID: '^'?('a'..'z'|'A'..'z'|'') ('a'..'z'|'A'..'z'|'''); *ID* and *ID* allow to write only one word and any number of words, respectively.

Table 2 lists the values of the attributes for two environment requirements (Reqs 1 and 2). Req 1 initializes variable "accSpeed". Req 2 provides the scope for this variable. Note that variables must be named as compound nouns (like "accSpeed" instead of "accelerate speed") if they involve several nouns. This rule will apply to other attributes of the MoST grammar.

Table 2. Instances of Two Environment Requirements

| Req 1 | envirReqID = "2.2.1"                  | envirVariable = "accSpeed" |

|-------|---------------------------------------|----------------------------|

|       | envirUnit = "m/s2"                    | envirAttributeValue = "0"  |

| Req 2 | envirReqID = "2.2.2"                  | envirVariable = "accSpeed" |

|       | compOperator1 = "greater or equal to" | bound1 = "0"               |

|       | compOperator2 = "less or equal to"    | bound2 = "10"              |

|       | envirUnit = "m/s2"                    |                            |

The corresponding MoST code can be written as follows

Req 1: [2.2.1] The accSpeed should be initialised to  $0 m/s^2$ .

Req 2: [2.2.2] The accSpeed should be greater or equal to 0 and less or equal to  $10 m/s^2$ .

#### 2). Mode Requirements

Mode requirements explain mode transitions that are associated with mode and signal conditions. Mode conditions indicate which mode the system is in. Signals are the core conditions for triggering mode transitions. The rule of mode requirements is listed as follows:

MODE:

modeReqID=ReqID 'when' preModeCondition = MODECONDITION (relations+=RELATION guards += SIGNALCON-DITION)\* ',' 'then' postModeCondition = MODECONDITION'.';

The details of the syntax are shown in the annex. Table 3 lists the values of the attributes for mode requirement Req 3. This requirement describes the transition between modes Economic and Sportive.

Table 3. Instance of Mode Requirement Req 3

| Req 3 | modeReqID = "6.2" | preModeCondition = "mode = economic"  |

|-------|-------------------|---------------------------------------|

|       | relation = "and"  | guards [1] = "signal = Ac"            |

|       |                   | postModeCondition = "mode = sportive" |

The corresponding MoST code can be written as follows:

Req 3: [6.2] when the car is in mode economic and it receives Ac signal, then it is in mode sportive.

Form. Asp. Comput.

# 3). State Requirements

State requirements describe system functional requirements via state transitions. Three conditions are able to trigger state transitions, including attribute, mode, and signal conditions. The rule of state requirements is illustrated as follows:

#### STATE:

stateReqID=ReqID 'when' preStateCondition+=STATECONDITON (relations+=RELATION guards += (ATTRIBUTE-CONDITION | MODECONDITION | SIGNAL CONDITION))\* ',' 'then' postStateCondition = STATE CONDITION '.';

Table 4 gives the attribute values of the state requirement Req 4. It depicts the transition between states Accelerate and Autonomy.

Table 4. Instance of State Requirement Req 4

```

stateReqID = "1.4"

preStateCondition = "state = accelerate"

relations[1] = "and"

guards[1] = "signal = Auto"

relations[2] = "and"

guards[2] = "accSpeed = 10 m/s2"

postStateCondition = "state = autonomy

```

The corresponding MoST code can be written as follows:

Req 4: [1.4] when the car is in state accelerate and it receives Auto signal and its accSpeed is equal to  $10 \ m/s^2$ , then it will be in state autonomy.

#### 4). Attribute Constraint Requirements

Attribute constraint requirements aim at determining the values of attributes under different conditions. The conditions can be any combination of state, mode, signal, and attribute conditions. The value can be an arithmetic equation as well. The rule of attribute constraint requirements is depicted as follows: ATTRIBUTECONSTRAINT:

attributeReqID=ReqID 'when' preAttributeCondition += (STATECONDITON | ATTRIBUTECONTION | SIGNAL-CONDITION) (relations += RELATION guards += (STATECONDITON | ATTRIBUTECONTION | SIGNAL CONDI-TION))\* ',' 'then' postAttributeCondition = (ATTRIBUTECONTION | ARITHMETICCONDITION) '.';

Table 5 shows the values of attributes for attribute constraint requirement Req 5. This requirement explains how the acceleration speed and the speed of a car influence the function of displaying speed.

Table 5. Instance of Attribute Constraint Requirement Req 5

```

attributeReqID = "5.2"

preAttributeCondition = "accSpeed = 5 m/s^2

relations[1] = "and"

guards[1] = "speed > 80 \text{ km/h}"

postAttributeCondition = "displaySpeed = TRUE"

```

The corresponding MoST code can be written as follows:

Req 5: [5.2] when the car accSpeed is equal to 5 m/s2 and its speed is greater than 80 km/h, then its displaySpeed is equal to TRUE.

## 5). Property Constraint Requirements

Property constraint requirements aid in describing functional and non-functional requirements. They will be used as properties that need to be checked. They are often involved with temporal issues. Classic temporal logics are considered in our language. The expressive power of the language is significantly increased by introducing CTL (Computational Temporal Logic) and LTL (Linear Temporal Logic). The rules of property constraint requirements are expressed as follows:

#### PROPERTYCONSTRAINT:

propertyReqID=ReqID 'when' preOperator= (CTLOperator | LTLOperator) prePropertyCondition = (STATECONDITON | ATTRIBUTECONTION | MODECONDITION) (preRelations+=RELATION guards += (STATECONDITON | ATTRIBUTECONTION | MODECONDITION))\* ',' 'then' postOperator = (CTLOperator | LTLOperator) postPropertyConditions = (STATECONDITON | ATTRIBUTECONTION | MODECONDITION) (postRelations+=RELATION postPropertyConditions += (STATECONDITON | ATTRIBUTECONTION | MODECONDITION))\* '.';

Table 6 lists all the values of the property constraint requirement attributes. This requirement provides a CTL specification to check the function of the car. Note that post-property conditions can be an array because multiple post-property conditions can be imposed by property constraint requirements.

Table 6. Instance of Property Constraint Requirement Req 6

```

Req 6

propertyReqID = "7.1"

preOperator = "all globally"

prePropertyCondition = "state = autonomy"

preRelations[1] = "and"

guards [1] = "mode = economic"

postOperator = "all next"

postPropertyConditions [1] = "state != accelerate"

```

The corresponding MoST code can be written as follows:

Req 6: [7.1] when all globally the car is in state autonomy and it is in mode economic, then all next it is not in state accelerate.

Since we plan to transform a MoST model into the corresponding NuSMV model, the semantics of the MoST model will be the semantics of its underlying NuSMV model. NuSMV is the first model checker based on BDDs (Binary Decision Diagrams), which is a reimplementation and extension of SMV [12]. NuSMV has been designed to be an open architecture for model checking, which can be reliably used for the verification of industrial designs, as a core for custom verification tools, as a testbed for formal verification techniques, and applied to other research areas. We choose not to introduce the semantics to avoid repetition. The details of NuSMV semantics can be seen in NuSMV 2.6 User Manual<sup>4</sup>.

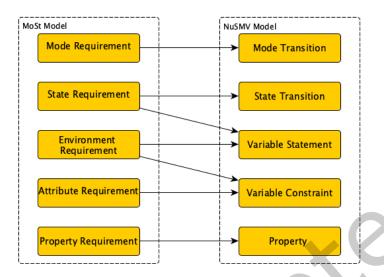

#### 4 MODEL TRANSFORMATION

The NuSMV model checker enables us to write the NuSMV code in different ways. It is essential to identify one of the most appropriate forms of NuSMV models, which corresponds to the MoST model. Therefore, the mapping between modules of the MoST model and the NuSMV model is provided, as shown in Fig. 4. The implementation of the process for the automatic model transformation is based on this mapping. The process is realized in Algorithms 1 - 5, which will be discussed in the following. The presented algorithms do not cover all details but focus on the main aspects of the mapping process. Note that Fig. 4 may give the wrong impression that the concept of modes exists already in NuSMV. In fact, we define modes as variables in NuSMV. Modules (NuSMV programs) have been designed to implement the functions of modes we defined.

As mentioned in Section 3, the MoST modeling language consists of mode, state, environment, property, and attribute modules. Mode modules are able to actively and passively intervene in the behaviors of the system. The active intervention implies modes can change the values of variables that influence the state transitions. The passive intervention means the mode itself can be regarded as the trigger. At the same time, the mode owns its mode transitions impacted by signals. Therefore, the type of the mode variable can be defined as *enumeration*. The main mode requirement transformation is implemented in Algorithm 1.

<sup>&</sup>lt;sup>4</sup>https://nusmv.fbk.eu/NuSMV/userman/v26/nusmv.pdf (accessed in April 2023)

Fig. 4. Mapping Between Modules of the MoST Model and the NuSMV Model

The NuSMV model naturally approves state modules. The input language of NuSMV supports the description of Finite State Machines (FSMs) which range from completely synchronous to completely asynchronous, and from the detailed to the abstract [10]. Thus, state modules can be transformed into the corresponding NuSMV code. The state requirement transformation is performed in Algorithm 2.

In terms of other elements of the MoST model, Environment and attribute modules are associated with the variable statement and the variable constraint. So, they can also be transformed into the NuSMV model. Since CTL and LTL specifications can be checked in the NuSMV model checker, the transformation of the property module is feasible as well. The processes for the model transformation for environment, and attribute modules are achieved in Algorithms 3-5 respectively. Technically speaking, implementing the model transformation depends on the MoST grammar and the structure of the NuSMV code. The grammar helps identify different kinds of requirements and extract the corresponding condition information. We then need to reorganize this information to make it suitable for the NuSMV parser. The time complexities of Algorithms 1-5 are all  $O(n^2)$  except for Algorithm 3 which is O(n).

In order to make the process clearer, the car requirements have been formalized in Fig. 5. Five kinds of requirements have been elicited to illustrate the transformation process. Note that the complete NuSMV code is shown in Annex B. Requirement [8.1] is a natural language requirement explained in Section 3.4.1, which will not be translated.

#### REQUIREMENTS VERIFICATION

In this section, we first introduce the architecture of the MoST modeling tool. Based on this tool, we discuss how we realize requirements static and dynamic checks.

#### MoST Modeling Tool

The MoST modeling tool is implemented by the Xtext framework in Eclipse. Fig. 6 shows the architecture of the MoST modeling tool. This tool consists of four components: Editor, Validator, Generator, and Model checker. Editor includes a UI and MoST language. UI is an Eclipse UI which aids in writing the MoST model. MoST is

# **Algorithm 1:** Mode Requirement Transformation

```

input :root

output: modeTransitions, modes

// The variable root represents the root of the MoS\tau\ model.

1 ArrayList<String> modeTransitions = new ArrayList<String>();

2 HashMap<String, String> modes = new HashMap<String, String>;

3 String temp="";

4 int indexMode = 0;

5 for modeReq : root.model.filter(MODE) do

indexMode = 0;

temp ="";

for preModeCondition : modeReq.preModeConditions do

temp += preModeCondition.condition;\\

if indexMode <= modeReq.relation.size - 1 then</pre>

10

temp+=modeReq.relation.get(indexMode++).relation ;

11

end

12

end

13

// Post-mode conditions look like "mode = A", the value of the mode is just required, conforming to

NuSMV code rules.

temp += postModeCondition.condition.split ("=").get(1);\\

14

modeTransitions.add(temp);

15

16 end

// Extract modes from mode transitions

17 for modeTransition: modeTransitions.entrySet do

if modeTransition!=null then

18

modes.put(modeTransition.keysplit("&").get(0).split("=").get(1)), "mode");

19

20

end

21 end

```

# Algorithm 2: State Requirement Transformation

```

input :root

output: stateTransitions

1 ArrayList<String> stateTransitions = new ArrayList<String>();

2 String temp="";

3 int indexState = 0;

4 for stateReq: root.model.filter(STATE) do

indexState = 0;

5

temp ="";

\textbf{for} \ \textit{preStateCondition}: \textit{stateReq.preStateConditions} \ \textbf{do}

temp += preState Condition. condition;\\

if indexState <= stateReq.relation.size - 1 then</pre>

temp += state Req. relation. get (index State ++). relation \ ; \\

10

end

11

12

end

// Post-state conditions look like "state = A", the value of the state is just required, conforming to

NuSMV code rules.

temp += postStateCondition.condition.split ("=").get(1);\\

13

stateTransitions.add(temp);

14

15 end

```

# Algorithm 3: Environment Requirement Transformation

```

output: variableConstraints, variables

1 HashMap<String> variableConstraints = new HashMap<String>();

2 HashMap<String,String> variables = new HashMap<String,String>();

String key="";

4 String pre="";

5 double max,min;

6 max=min=0;

for environmentReq : root.model.filter(ENVIRONMENT) do

key = environmentReq.envirVariable;

// initializing variables

if environmentReq.range == null then

pre = variableConstraints.get(key);

10

if pre == null then

11

pre="";

12

end

13

// The initial value of variables is stored in the left part of @ of pre.

pre = environmentReq.envirAttributeValue.attributeValue + "@" + pre;

14

variableConstraints.put(key,pre);

15

16

end

// setting the scope for variables

else

17

if environmentReq.range.bound1.attributeValue <= environmentReq.range.bound2.attributeValue then

18

19

min=environmentReq.range.bound1.attributeValue;

max=environmentReq.range.bound2.attributeValue;

20

21

end

else

22

min=environmentReq.range.bound2.attributeValue;

23

max=environmentReq.range.bound1.attributeValue;

24

end

25

variables.put(key,min+ ".."+max);

26

27

end

```

created based on the Eclipse Modeling Framework and the core of Eclipse. Validator is a static checker written by Xtend language, which checks the MoST model against the static rules. Generator is a MoST-To-NuSMV transformer written by Xtend, which allows us to automatically transform MoST models into NuSMV models. Finally, a NuSMV runner is a dynamic checker written as a Java class, linking the NuSMV model checker with this tool, in order to automate dynamic checks.

The implementation of the NuSMV runner is based on the method "java.lang.ProcessBuilder.ProcessBuilder(List< String> command)". This process builder helps us call the NuSMV model checker with the argument "List<String> command". The argument comprises two constant strings in sequence: "NUSMV\_EXECUTE\_PATH" and "GENERATED\_SMV\_FILE\_PATH". The method "processBuilder.start()" starts the call of the checker, which produces results included in "p.getInputStream()" and "p.getErrorStream()". Input streams store the output of the checker except for the error information which is stored in error streams.

It should be noted that the information of errors implies the NuSMV model is not correct rather than the automatically generated specifications or user-defined specifications are false. The incorrectness of the NuSMV model

# Algorithm 4: Attribute Requirement Transformation

```

output: variableConstraints

1 HashMap<String> variableConstraints = new HashMap<String>();

2 String temp="";

3 String pre, key;

4 int indexAttribute = 0;

5 for attributeReq : root.model.filter(ATTRIBUTE) do

indexAttribute = 0;

temp ="";

\textbf{for} \ \textit{preAttributeCondition}: attributeReq. \textit{preAttributeConditions} \ \textbf{do}

temp += preAttributeCondition.condition;

if indexAttribute <= modeReq.relation.size - 1 then</pre>

10

temp += attribute Req. relation. get (index Attribute ++). relation; \\

11

end

12

end

13

key = attributeReq.postAttributeCondition.condition.split("=").get(0);

14

temp += ":"+attributeReq.postAttributeCondition.condition.split("=").get(1)+";";

15

pre = attributeConstraints.get(key);

16

if pre!=null then

17

temp += pre;

18

19

if pre != temp then

20

21

attributeConstraints.put(key,temp);

22

23 end

```

means this model hides run-time errors. The automatically generated specifications signify the specifications must need to be satisfied. The user-defined specifications signify the expectations of the users which are not necessarily realistic. The NuSMV runner functions with the validator via files such as "\*.smv" and "\*.txt". The executing sequence is illustrated as follows:

- Users write requirements in the editor; the validator dynamically executes static checks with static rules;

- Once the MoST model is ready in the editor and saved, the code generator will be executed to transform the MoST model into the NuSMV model;

- The NuSMV runner is called to simulate the NuSMV model by pressing the space key in any empty place of the editor; the runner then analyzes the results to make them understandable to the Validator;

- Finally, the Validator checks the MoST model by the analyzed results to put them to the relevant requirements

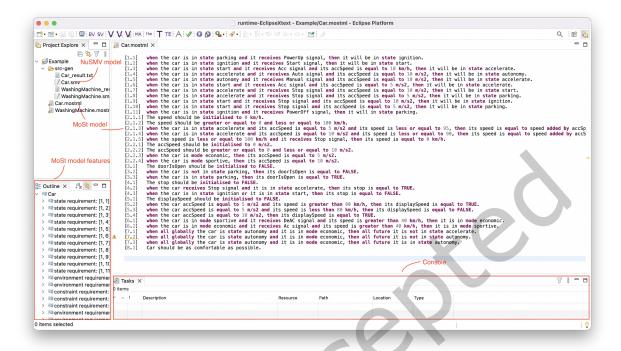

A screenshot of the tool is shown in Fig. 7. This project is publicly available on GitHub<sup>5</sup>. The details of the requirement checking will be discussed in the next sections.

# 5.2 Requirements Static Checking

Requirements static checking aims at verifying the names of the MoST model elements and ensuring the requirement consistency from the static rules. Requirements static checks are triggered while writing the MoST code. If the static rules are violated, errors will pop up in the MoST modeling editor.

<sup>&</sup>lt;sup>5</sup>https://github.com/liuyinling/MoSt-Modeling-Tool.git

#### **Algorithm 5:** Property Requirement Transformation

```

output:propertySpecifications

1 ArraryList<String> propertySpecifications = new ArraryList<String>();

2 String temp="";

3 int indexPreProperty, indexPostProperty;

4 for propertyReq : root.model.filter(PROPERTY) do

indexPreProperty = 0;

indexPostProperty = 0;

temp = propertyReq.preOperator.logicOperator;

for prePropertyCondition: propertyReq.prePropertyConditions do

temp+=prePropertyCondition.condition;

if indexPreProperty <= propertyReq.preRelation.size - 1 then</pre>

10

temp += property Req. pre Relations. get (index Pre Property ++). relation; \\

11

end

12

end

13

temp += propertyReq.postOperator.logicOperator;

14

for postPropertyCondition : propertyReq.postPropertyConditions do

15

temp+=postPropertyCondition.condition;

16

if indexPostProperty <= propertyReq.postRelation.size - 1 then</pre>

17

temp+=propertyReq.postRelations.get(indexPostProperty++).relation;

18

end

19

20

end

21

propertySpecifications.add(temp);

22 end

```

Requirements static checks include naming checks and consistency checks. Naming checks in the MoST model concerning states, modes, and signals are: the names of states and modes should start with a lower case; the name of signals should begin with an upper case. Listing 1 shows the implementation of mode name checks. In the Xtext framework, rules are implemented in the validation package. Each rule starts with @Check. Since class MoStMLValidator (where we implement rules) extends class AbstractMoStMLValidator, we can directly access model objects such as MODECONDITION.

Listing 1. The Implementation of Mode Name Checks

```

1@Check

2 def  void checkModeName(MODECONDITION modeCondition){

3    if (modeCondition.getModeName().charAt(0) <= 'Z'&&modeCondition.getModeName()

4    .charAt(0) >= 'A') {

5        error("Mode name should start with a lower case"+": error

6        '"+modeCondition.getModeName().charAt(0)+"'",

7        MoStMLPackage.Literals.MODECONDITION_MODE_NAME,INVALID_ReqID);

8    }

9}

```

Consistency checks analyze the legality of requirements, regarding static rules. For example, one of our rules is "Variables should only be initialized once". If two requirements are written as "[1.1] The doorIsOpen should be initialized to FALSE." and "[1.2] The doorIsOpen should be initialized to TRUE.", then error "Variables should

```

| 13.23 | when the cor is in state spring and it receives Start signal, then it will be in state start.

| 13.23 | when the cor is in state start and it receives Start signal, then it will be in state start.

| 13.23 | when the cor is in state start and it receives Start signal, then it will be in state start.

| 13.24 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 10 km/h, then it will be in state accordance.

| 13.25 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 30 km/h, then it will be in state accordance.

| 13.25 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 30 km/h, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 30 km/h, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 30 km/h, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal, then it will be in state parking.

| 13.25 | when the cor is in state start and it receives Stard signal and its acciperate is equal to 30 km/h.

| 13.25 | when the cor is in state carbon and its acciperate signal to 30 km/h.

| 13.25 | when the cor is state start and it receives Stard signal to 30 km/h.

| 13.25 | when the cor is state acciderate it is accidered its equal to 30 km/h.

| 13.25 | when the cor is state stard and its acciderate its seal to 30 km/h.

| 13.25 | when the cor is state stard and its acciderate its equal to 30 km/h.

| 13.25 | when the cor is not a state parking.

| 13.25 | when the cor is not a star

```

Fig. 5. An Example of the Model Transformation

Fig. 6. Architecture of the MoSτ Modeling Tool

only be initialized once! 'doorIsOpen" will be shown on these two requirements. CC3 intends to define the value ranges for variables. CC6 is a syntactic check for state requirements. The requirements consistency checks (CC) include, but not limited to:

CC1: Variables should only be initialized once;

Form. Asp. Comput.

Fig. 7. Screenshot of the MoSτ Modeling Tool

- CC2: The variables mentioned in attribute requirements should be initialized;

- CC3: The variable of *Integer* should be given the scope;

- CC4: The repetition of requirement IDs is not allowed;

- CC5: The repetition of requirements is not allowed;

- CC6: Different post-conditions of state requirements cannot have the same preconditions and guards.

- CC7: The variable of attribute conditions must be defined before using it.

Obviously, this list may be not exhaustive. However, adding new rules is possible. The Xtext framework allows us to use Validator to achieve these rules. Since the implementation of the naming and consistency rules is provided in the tool, it illustrates the way how we extract data from the model. Adding new rules simply involves the manipulation of extracted data. Indeed, they are helpful in writing a proper MoST model. However, they cannot guarantee that the generated NuSMV model is correctly executable. In other words, we are not sure that the internal logic of the system is correct. For example, if "division by zero" exists, static checks cannot find this error. Therefore, requirements dynamic checks will be discussed in the following.

# 5.3 Requirements Dynamic Checking

Requirements dynamic checks rely on the model checker NuSMV. Requirements dynamic checking includes the analysis of the generated NuSMV model, the user-defined specifications, and the automatically generated specifications.

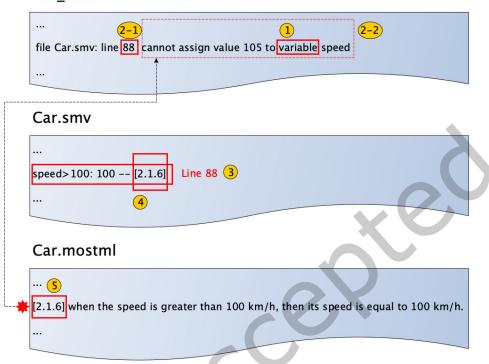

5.3.1 Traceability analysis. Traceability analysis offers a general approach about how to use the results of model checking to improve the quality of the requirements model. This analysis involves three types of errors: program errors, user-defined specification errors, and automatically generated specification errors. Program errors mean the NuSMV model has run-time errors because of bugs such as type errors, division by zero, etc. User-defined specification errors denote property requirements that are false. The last errors indicate the automatically generated properties which are false. Three types of errors require three specific analysis methods, respectively. The method for the first type needs to extract information from simulation results, including IDs or names of variables. If the line number does not relate to the code commented by the requirement ID, we should extract the names of the relevant variables. The way of extracting the names of variables depends on the contents of the errors identified by NuSMV. If errors explicitly indicate the names of variables, we extract the names directly. If not, we should infer the relevant variables from the simulation results. The inference comes from the manual analysis of the outputs of NuSMV against the errors of the same type. Currently, we found the lines "line number -1" always show variable names. The relevant constraint requirements can be matched via variable names.

Fig. 8 shows an example of the traceability analysis for program errors. The traceability analysis involves three files: "Car\_result.txt", "Car.smv", and "Car.mostml". The indexes indicate the sequence of analysis. In this example, we first found the keyword "variable" existed (step 1). Then, we found the line number was 88 (step 2-1). At the same time, the error information "cannot assign value 105 to variable speed" was stored (step 2-2). Next, we searched line 88 in the file "Car.smv" (step 3) and extracted requirement ID [2.1.6] (step 4). With the ID, we finally attached the error information to the corresponding requirement in the file "Car.mostml" (step 5). How to attach errors to the requirements can be seen in Listing 1. It should be noted that the list of errors of different output forms may not be exhaustive, which means if the NuSMV outputs another new type of error, our tool will not immediately be able to deal with it. However, we provide an interface printing "this tool is not able to handle this error - XXX, please report it to the developers" when a new type of errors appears.

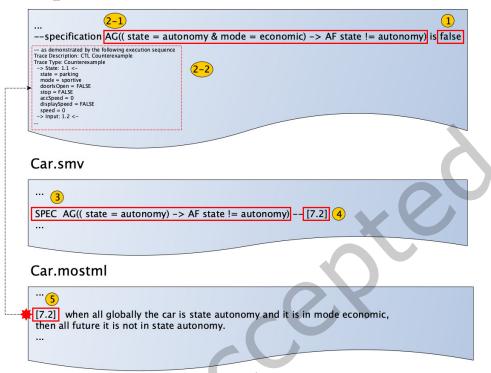

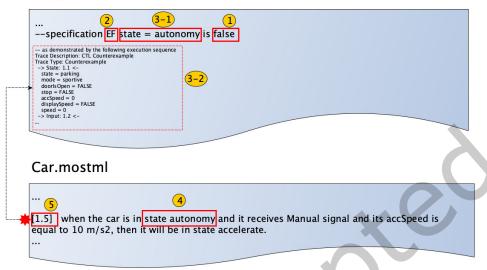

The second method finds IDs by comparing property specifications. They are specifications of user-defined and re-assembled. We should re-assemble properties because the presentation of specifications is a little bit different from that of the NuSMV model. The extracted IDs serve as one of the links to ensure traceability between requirements and the NuSMV code since the code commented by requirements IDs corresponds to requirements. Fig. 9 gives an example of the traceability analysis for user-defined specification errors. This analysis also necessitates the three files mentioned above. In this example, we first found the keyword "false" (step 1). Then we extracted the property specification formula (step 2-1) and the counter-example (step 2-2). Based on the formula, we found the same formula in the file "Car.smv" (step 3) and extracted the corresponding requirement ID [7.2] (step 4). With the ID, we finally attached the counter-example to the corresponding requirement in the file "Car.mostml" (step 5).

The last method is simply to extract state conditions from the specifications because they are automatically generated. The third kind of errors is only concerned with state requirements. The reason can be seen in Section 5.3.2. We can also use state conditions to locate requirements with errors because they are used to match state requirements with the same post-condition. Fig. 10 presents an example of the traceability analysis for automatically generated specification errors. This analysis is only related to two files: "Car\_result.txt" and "Car.mostml". In this example, we first identified the keyword "false" (step 1). We then noticed the keyword "EF" existed as well (step 2). Next, we extracted "state = autonomy" and the counter-example. In the following, we only identified requirement [1.5] where reaching state *autonomy* was one of the conditions (step 4). So, we finally attached the counter-example to the corresponding requirement in the file "Car.mostml" (step 5).

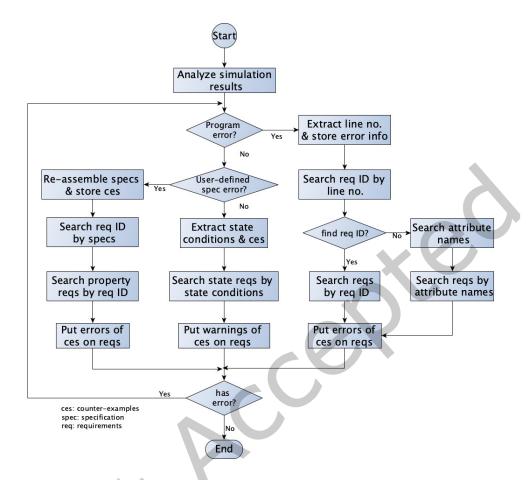

Fig. 11 shows the diagram for processing simulation results regarding different types of errors. The three analysis methods are implemented in the NuSMV runner. It should be noted that the NuSMV model checker produces program errors one by one and generates all the results of specifications checks at one time. If there are

# Car\_result.txt

Fig. 8. Traceability Analysis for Program Errors

more than one program error, we should correct one, save the model, and press the space key, iteratively until they are all solved.

Since we have built the links between simulation results and requirements, we will continue to take advantage of model checking to help us verify the correctness of the requirements model. As the successfully compiled NuSMV code does not necessarily mean the states in the requirements are all reachable, therefore, we would like to check the reachability of the requirements.

- 5.3.2 Reachability analysis. Reachability analysis concerns the checking of the automatically generated property specifications, which provides the possibility to check the reachability of states. This analysis is performed by proposing additional CTL specifications. The specification is conformed to the form  $\phi = EF$  (state = X) to check the reachability of each state. So, the reachability analysis only relates to the state requirements. To facilitate the analysis process, additional property specifications for the reachability of each state are generated automatically from the previous model transformation.

- 5.3.3 Validation analysis. Validation analysis checks the satisfiability of property requirements. Property requirements are transformed into the CLT/LTL specifications in the NuSMV model. Thus, validation analysis checks the satisfiability of CTL/LTL specifications regarding the generated NuSMV model. This analysis enables customers to gain a global understanding of how the system will work. Requirements engineers should conduct validation analysis from the requirements level. Because the requirements that will never be satisfied should be

# Car\_result.txt

Fig. 9. Traceability Analysis for User-defined Specification Errors

modified or deleted as early as possible. This can avoid conflicts between developers and customers when the system is delivered.

Most importantly, as mentioned at the beginning of Section 1, when the system of interest is becoming more and more complex and intelligent, we need to check whether the conflicts between modes and states exist. In other words, the newly added capabilities to make the system more intelligent may cause the system out of boundary. This out-of-boundary may lead to catastrophes in safety-critical areas. To check whether the system has conflicts, we propose to use property specifications conforming to  $SPEC\ AG((state = X\ \&\ mode = M) - > AF\ state = Y$ . The specifications of this form imply when the system is in state X and we change the mode to M, which state the system will eventually be in. If we do want to change its state with the activation of mode M, the future state should change. So, the specification should be true in this case. If the property specification turns out to be false, requirements designers should either make it true via the analysis of counter-examples or ensure that this situation is allowed in the system.

#### 6 EVALUATION

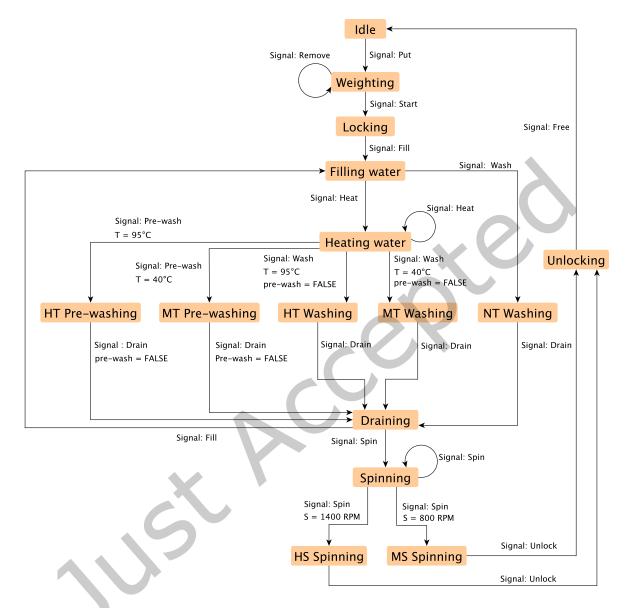

In order to illustrate the feasibility of our approach, we gave systematic evaluations of a car example and a washing machine example. We discussed the first case study (the car example) in detail. In the second case, only necessary explanations were provided to prevent redundancy.

Form. Asp. Comput.

# Car\_result.txt

Fig. 10. Traceability Analysis for Automatically Generated Specification Errors

### 6.1 A Car Example

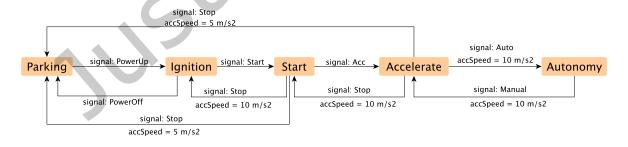

- 6.1.1 System description. This example is based on a UML state machine diagram for a car<sup>6</sup>. The car has five states including *Parking, Ignition, Start, Accelerate*, and *Autonomy*. We assume that this car has the function of autonomous driving. The details of the car's state transitions are shown in Fig. 12. Signals and attributes constitute the conditions for state transitions. Modes influence the system behaviour via changing the value of attributes. Here, we provide this car with two modes *economic* and *sportive*. They are related to variables *accSpeed* and *displaySpeed*. For example, if the car is in mode *economic* and mode *sportive*, it changes the acceleration speed to 5 m/s2 and 10 m/s2, respectively. Note that we avoid discussing all the details of the system. Interested readers can see the details of the impact of modes on variables in Annex A.