# Architecture reconfigurable de système embarqué auto-organisé

Slavisa Jovanovic

#### ▶ To cite this version:

Slavisa Jovanovic. Architecture reconfigurable de système embarqué auto-organisé. Autre [cs.OH]. Université Henri Poincaré - Nancy 1, 2009. Français. NNT: 2009NAN10099. tel-01748306

### HAL Id: tel-01748306 https://hal.univ-lorraine.fr/tel-01748306

Submitted on 29 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

U.F.R. Sciences et Techniques, Mathématiques, Informatique, Automatique École doctorale Informatique Automatique Électronique Électrotechnique Mathématiques Département de formation doctorale Électronique Électrotechnique

# Architecture reconfigurable de système embarqué auto-organisé

### **THÈSE**

présentée et soutenue publiquement le 6 novembre 2009

pour l'obtention du

### Doctorat de l'université Henri Poincaré – Nancy 1

(spécialité Instrumentation et Microélectronique)

par

### Slaviša JOVANOVIĆ

#### Composition du jury

Président: M. Michel PAINDAVOINE, Professeur, Université de Bourgogne, Dijon

Rapporteurs: M. Ian O'CONNOR, Professeur, INL - Ecole Centrale de Lyon, Lyon

M. Olivier SENTIEYS, Professeur, ENSSAT, Lannion

Examinateurs: M. Christophe BOBDA, Professeur, Université de Potsdam, Allemagne

M. Camel TANOUGAST, Maître de Conférences, Université Paul Verlaine, Metz

M. Serge WEBER, Professeur, UHP, Nancy 1

### Remerciements

J'adresse mes sincères remerciements à Monsieur Ian O'CONNOR, Professeur à l'École Centrale de Lyon ainsi qu'à Monsieur Olivier SENTIEYS, Professeur à l'École Nationale Supérieure des Sciences Appliquées et de Technologie de Lannion, qui m'ont fait l'honneur de juger cette thèse en qualité de rapporteurs.

Je tiens également à remercier Monsieur Christophe BOBDA, Professeur à l'Université de Potsdam et Monsieur Michel PAINDAVOINE, Professeur à l'Université de Bourgogne d'avoir accepté d'examiner ce travail et de participer à ce jury.

J'adresse mes remerciements à Monsieur Serge WEBER, Professeur à l'Université Henri Poincaré de Nancy et directeur du Laboratoire LIEN, de m'avoir accueilli au sein du Laboratoire LIEN et de m'avoir accordé sa confiance au sein de l'équipe « Architecture » qu'il dirige. Je tiens également à le remercier d'avoir accepté d'être mon directeur de thèse.

Je souhaite particulièrement remercier Monsieur Camel TANOUGAST, Maître de Conférences à l'université de Paul Verlaine de Metz, de m'avoir encadré durant cette thèse, pour ses qualités et sa rigueur scientifique, sa disponibilité et son soutien permanent qui m'ont beaucoup aidé tout au long de ce travail.

Je remercie tous mes collègues et membres du LIEN pour leur aide ou les conseils qu'ils ont pu m'apporter à un moment ou un autre. Sans oublier Patrice, pour son sens de l'humour, ses blagues et son café, rendant nos pauses café des moments détendus et conviviaux.

Je tiens à remercier mes parents et tous mes amis pour leur soutien et leurs questions « répétitives » concernant mon sujet de travail et son utilité finale.

Enfin, je souhaite terminer ces remerciements par une attention particulière à Jasna, mon épouse, pour son soutien permanent, sa patience et sa compréhension tout au long de ces trois années de thèse.

Slaviša JOVANOVIĆ septembre 2009

« Un voyage de mille kilomètres commence toujours par un premier pas » Lao Tseu

Je dédie ce travail à mes parents : Stanka et Velizar

# Table des matières

| Table u  | es ngur   | es es                                                       | XIII  |

|----------|-----------|-------------------------------------------------------------|-------|

| Liste de | es tablea | aux                                                         | xix   |

| Résumé   | 5         |                                                             | xxi   |

| Abstrac  | et        |                                                             | xxiii |

| Glossai  | re        |                                                             | XXV   |

| Introdu  | ction ge  | énérale                                                     |       |

| 1        | Contex    | xte général                                                 | 1     |

| 2        | Motiva    | ation                                                       | 2     |

| 3        | Contri    | bution                                                      | 4     |

| 4        | Plan d    | u manuscrit                                                 | 4     |

| 1        |           |                                                             |       |

| Les syst | tèmes a   | uto-organisés et / ou émergents                             |       |

| 1.1      | Introd    | uction                                                      | 7     |

| 1.2      | Auto-o    | organisation                                                | 8     |

|          | 1.2.1     | Définitions courantes                                       | 8     |

|          | 1.2.2     | Premiers principes d'auto-organisation : genèse             | 10    |

|          |           | 1.2.2.1 Le principe d'auto-organisation par Ashby           | 10    |

|          |           | 1.2.2.2 Le principe d'auto-organisation par <i>Lendaris</i> | 11    |

|          | 1.2.3     | Notion d'auto-organisation des systèmes                     | 12    |

|          |           | 1.2.3.1 Définition d'un système auto-organisé               | 12    |

|          |           | 1.2.3.2 Propriétés des systèmes auto-organisés              | 14    |

|          | 1.2.4     | Notion d'émergence dans les systèmes auto-organisés         | 18    |

|    |      |           | 1.2.4.1     | L'émergence - définition                                         | 19 |

|----|------|-----------|-------------|------------------------------------------------------------------|----|

|    |      |           | 1.2.4.2     | Propriétés propres à l'émergence                                 | 21 |

|    |      | 1.2.5     | L'auto-o    | rganisation et l'émergence des systèmes                          | 23 |

|    | 1.3  | Mise e    | n œuvre d   | e l'auto-organisation et / ou émergence                          | 25 |

|    |      | 1.3.1     | Systèmes    | s de calcul autonome - Autonomic computing                       | 25 |

|    |      | 1.3.2     | Systèmes    | s de calcul inspirés organique - Organic computing               | 27 |

|    |      | 1.3.3     | Systèmes    | s multi-agents (Multi-agents Systems - MAS)                      | 28 |

|    | 1.4  | Nouve     | lle approc  | he à base de technologie reconfigurable                          | 29 |

|    | 1.5  | Conclu    | ision       |                                                                  | 30 |

| 2  |      |           |             |                                                                  |    |

| Co | ncep | ts de l'a | uto-orgar   | nisation matérielle à base de technologie reconfigurable         |    |

|    | 2.1  | Introdu   | action      |                                                                  | 33 |

|    | 2.2  | Systèn    | nes reconfi | gurables à base de <i>FPGA</i>                                   | 35 |

|    |      | 2.2.1     | Introduct   | tion                                                             | 35 |

|    |      | 2.2.2     | Les circu   | nits FPGA                                                        | 36 |

|    |      | 2.2.3     | Modes d     | e reconfiguration                                                | 37 |

|    | 2.3  | Systèn    | nes reconfi | gurables auto-organisés                                          | 39 |

|    |      | 2.3.1     | Introduct   | tion                                                             | 39 |

|    |      | 2.3.2     | Définitio   | on d'un système auto-organisé reconfigurable                     | 40 |

|    |      | 2.3.3     | Modélisa    | ation et formalisation d'un système auto-organisé reconfigurable | 42 |

|    |      | 2.3.4     | Propriété   | és d'un système auto-organisé reconfigurable                     | 44 |

|    |      |           | 2.3.4.1     | Adaptabilité des systèmes reconfigurables                        | 45 |

|    |      |           | 2.3.4.2     | Robustesse et flexibilité des systèmes reconfigurables           | 46 |

|    |      |           | 2.3.4.3     | « Augmentation de l'ordre » des systèmes reconfigurables         | 48 |

|    |      |           | 2.3.4.4     | Anticipabilité des systèmes reconfigurables                      | 49 |

|    |      |           | 2.3.4.5     | Autonomie des systèmes reconfigurables                           | 51 |

|    |      |           | 2.3.4.6     | Contrôle décentralisé pour systèmes reconfigurables              | 52 |

|    |      |           | 2.3.4.7     | Interactivité et autres propriétés émergentes des systèmes re-   |    |

|    |      |           |             | configurables                                                    | 53 |

|    | 2.4  | Un sys    | tème reco   | nfigurable auto-organisé : besoins                               | 54 |

|    | 2.5  | Conclu    | ision       |                                                                  | 55 |

| 3   |      |          |             |                                                               |     |

|-----|------|----------|-------------|---------------------------------------------------------------|-----|

| Pro | posi | tion arc | hitectural  | le d'un système auto-organisé reconfigurable                  |     |

| 3   | 3.1  | Introdu  | action      |                                                               | 57  |

| 3   | 3.2  | Une ap   | proche are  | chitecturale matérielle pour les systèmes auto-organisés      | 59  |

|     |      | 3.2.1    | Formulat    | tion du principe d'auto-organisation matérielle               | 59  |

|     |      | 3.2.2    | Concept     | d'une structure informationnelle de perception environnemen-  |     |

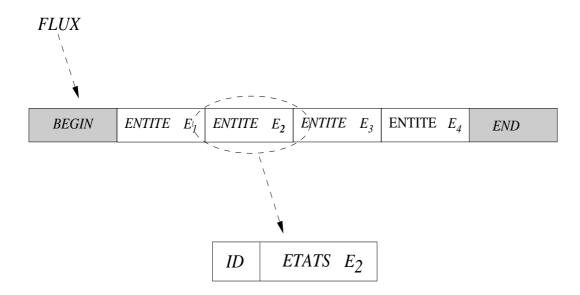

|     |      |          | tale : not  | ion de « flux »                                               | 61  |

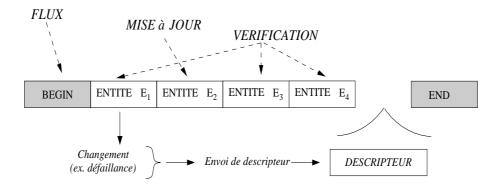

|     |      | 3.2.3    | La struct   | ure du <i>flux local</i>                                      | 64  |

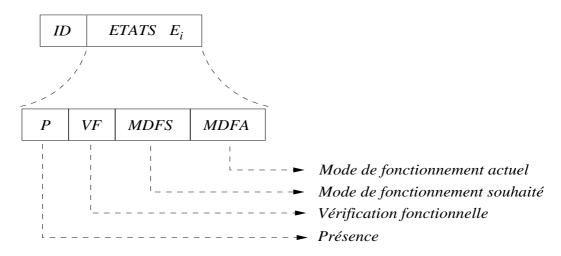

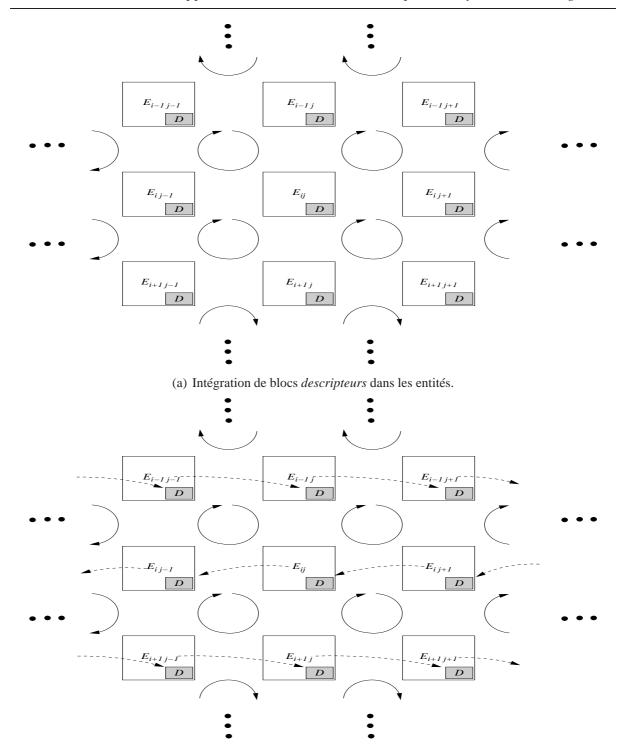

|     |      | 3.2.4    | Descript    | eur d'une entité système                                      | 67  |

|     |      | 3.2.5    | Mise en     | œuvre du concept d'auto-organisation par vérification de flux |     |

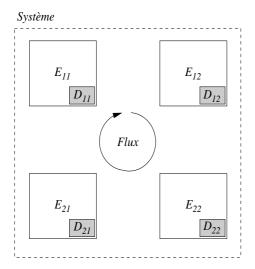

|     |      |          | informat    | ionnel                                                        | 71  |

| 3   | 3.3  | Conclu   | ision       |                                                               | 74  |

| 4   |      |          |             |                                                               |     |

| Rés | eau  | de comi  | municatio   | n sur puce pour un système reconfigurable auto-organisé       |     |

| ۷   | 4.1  | Introdu  | action      |                                                               | 77  |

| 2   | 4.2  | Réseau   | ıx sur puce | e                                                             | 80  |

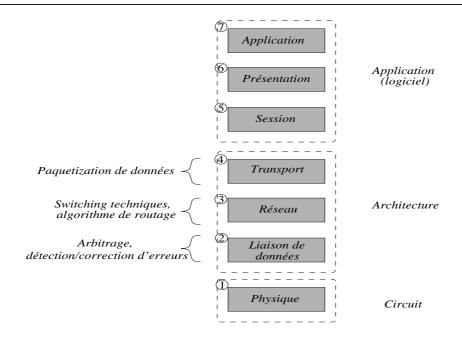

|     |      | 4.2.1    | Réseau s    | ur puce selon le modèle de référence OSI                      | 81  |

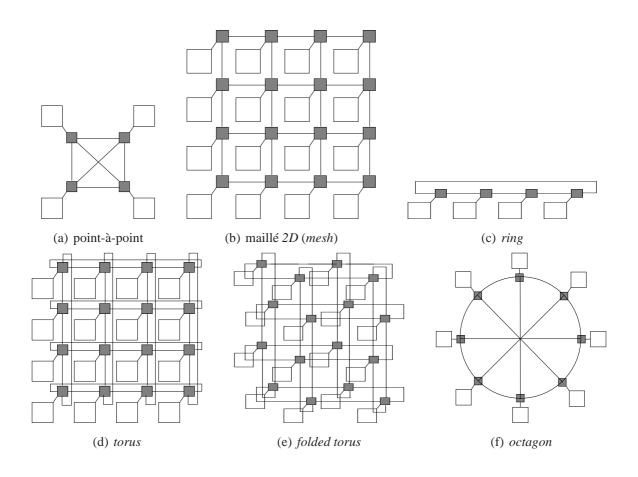

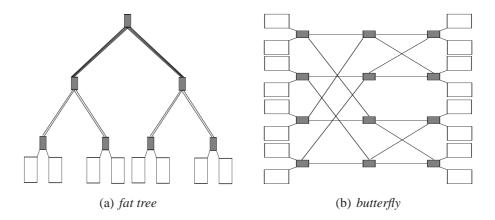

|     |      | 4.2.2    | Topologi    | es des réseaux sur puce                                       | 84  |

|     |      | 4.2.3    | Techniqu    | ues d'aiguillage - Switching techniques                       | 85  |

|     |      | 4.2.4    | Algorith    | me de routage                                                 | 88  |

| 4   | 4.3  | Réseau   | ıx sur puce | e reconfigurables                                             | 90  |

|     |      | 4.3.1    | Introduct   | ion                                                           | 90  |

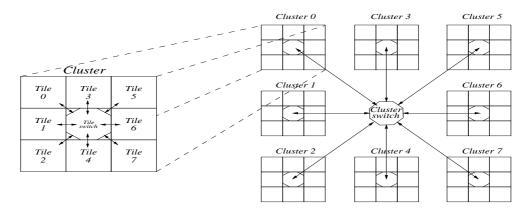

|     |      | 4.3.2    | Architect   | ture CuNoC                                                    | 96  |

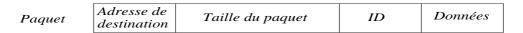

|     |      |          | 4.3.2.1     | Structure de message dans le <i>CuNoC</i>                     | 97  |

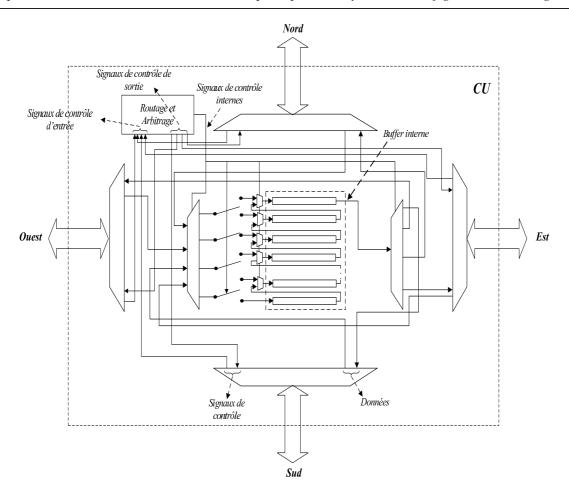

|     |      |          | 4.3.2.2     | Le routeur Unité de communication (CU - Communication         |     |

|     |      |          |             | Unit)                                                         | 97  |

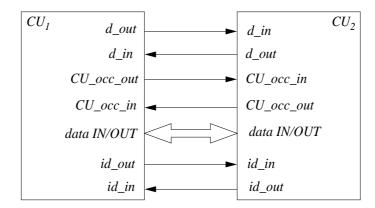

|     |      |          | 4.3.2.3     | Interconnexions entre $CU$                                    | 101 |

|     |      |          | 4.3.2.4     | Types d'Unité de communication                                | 103 |

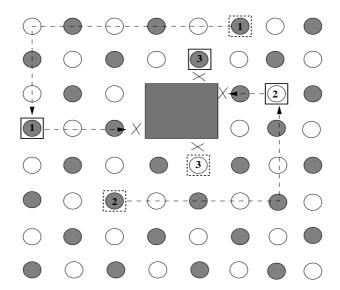

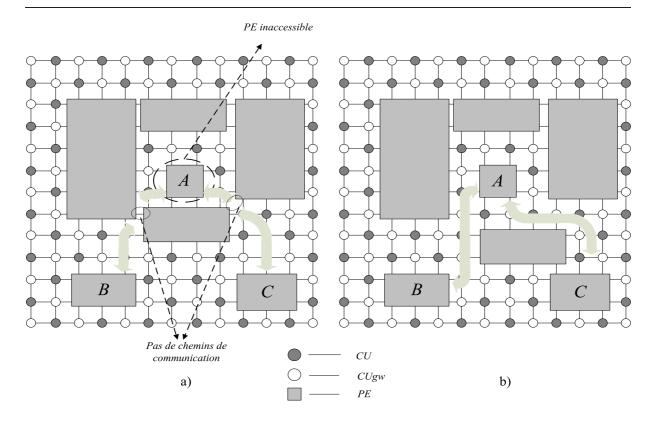

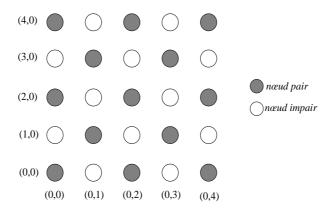

|     |      |          | 4.3.2.5     | Placement et conditions de placement des modules dynamiques   | 3   |

|     |      |          |             | dans un réseau CuNoC à topologie maillée (mesh)               | 106 |

|     |      |          | 4.3.2.6     | Placement dynamique des modules dans un CuNoC                 | 109 |

|     |      |          | 4.3.2.7     | Résultats de simulation                                       | 111 |

|     |      |          | 4.3.2.8     | Résultats d'implantation d'un réseau CuNoC                    | 115 |

|    |        |          | 4.3.2.9       | Évaluations des performances du <i>CuNoC</i>                    | 115 |

|----|--------|----------|---------------|-----------------------------------------------------------------|-----|

|    |        | 4.3.3    | QNoC .        |                                                                 | 125 |

|    |        |          | 4.3.3.1       | Introduction                                                    | 125 |

|    |        |          | 4.3.3.2       | Architecture d'un routeur du réseau QNoC - Q-switch             | 126 |

|    |        |          | 4.3.3.3       | Architecture structurelle d'un bloc « Logique de sortie »       | 128 |

|    |        |          | 4.3.3.4       | Logique de contrôle centrale                                    | 129 |

|    |        |          | 4.3.3.5       | Algorithme de routage                                           | 130 |

|    |        |          | 4.3.3.6       | Conditions de placement des modules dynamiques de calcul        |     |

|    |        |          |               | dans un réseau <i>QNoC</i>                                      | 131 |

|    |        |          | 4.3.3.7       | Implantation et résultats de synthèse d'un réseau $QNoC$        | 131 |

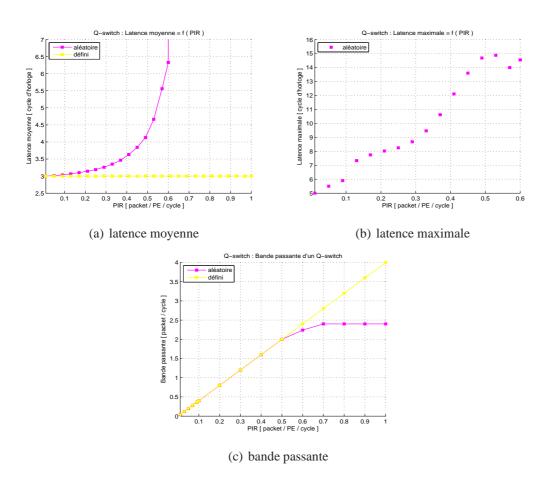

|    |        |          | 4.3.3.8       | Évaluation des performances d'un réseau QNoC                    | 133 |

|    |        | 4.3.4    | Analyse       | comparative entre un réseau CuNoC et un réseau QNoC             | 144 |

|    |        | 4.3.5    | Algorith      | me de routage des réseaux <i>CuNoC</i> et <i>QNoC</i>           | 148 |

|    |        |          | 4.3.5.1       | Introduction                                                    | 148 |

|    |        |          | 4.3.5.2       | Les algorithmes de routage tolérants aux fautes : Etat de l'art | 148 |

|    |        |          | 4.3.5.3       | L'algorithme de routage MPA des réseaux CuNoC et QNoC.          | 149 |

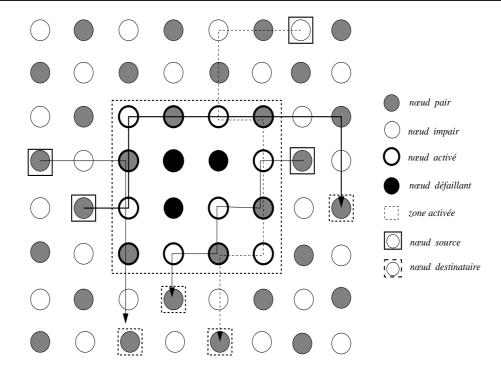

|    |        |          | 4.3.5.4       | Routage des paquets dans un réseau utilisant l'algorithme MPA   | 153 |

|    |        |          | 4.3.5.5       | Absence de blocage de paquets dans un réseau basé sur le        |     |

|    |        |          |               | routage MPA (Deadlock freeness)                                 | 155 |

|    |        |          | 4.3.5.6       | Résultats de simulation                                         | 156 |

|    | 4.4    | Conclu   | usion         |                                                                 | 158 |

| 5  |        |          |               |                                                                 |     |

| Va | lidati | ion expé | érimentale    | e du concept d'auto-organisation architectural proposé          |     |

|    | 5.1    | Introd   | uction        |                                                                 | 161 |

|    | 5.2    | Applic   | cation traite | ée : Détection temps réel de contours d'images                  | 161 |

|    |        | 5.2.1    | Introduct     | tion                                                            | 161 |

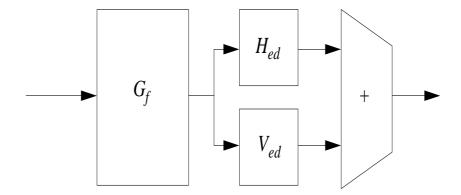

|    |        | 5.2.2    | Propositi     | ion d'un système auto-organisé pour détection temps réel de     |     |

|    |        |          | contours      | d'images                                                        | 163 |

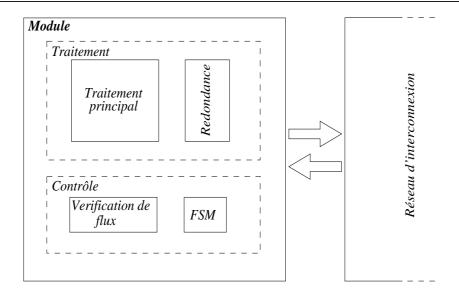

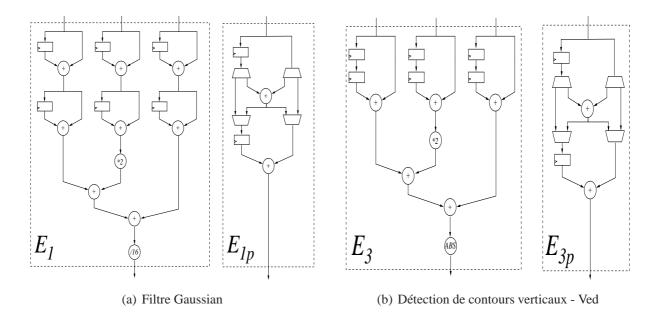

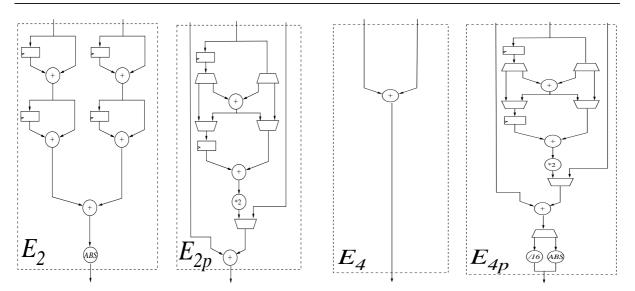

|    |        |          | 5.2.2.1       | Architecture structurelle                                       | 163 |

|    |        |          | 5.2.2.2       | Réseau de communication inter-modules et format de paquets      |     |

|    |        |          |               | de données                                                      | 165 |

|    |        |          | 5.2.2.3       | Bloc de « vérification de flux »                                | 167 |

|    |        |          | 5.2.2.4       | Bloc de contrôle de module <i>FSM</i>                           | 170 |

|    |        |          | 5.2.2.5       | Cas applicatif d'étude                                          | 174 |

|    |        |          |               |                                                                 |     |

|                  | 5.2.3    | Implantation FPGA et résultats de synthèse | 176 |  |

|------------------|----------|--------------------------------------------|-----|--|

|                  | 5.2.4    | Validation expérimentale                   | 181 |  |

|                  | 5.2.5    | Évaluation des performances                | 182 |  |

| 5.3              | Conclu   | ision                                      | 183 |  |

| Conclus          | sion gén | érale et perspectives                      |     |  |

| Bibliographie 19 |          |                                            |     |  |

| Liste de         | publica  | ntions                                     |     |  |

# Table des figures

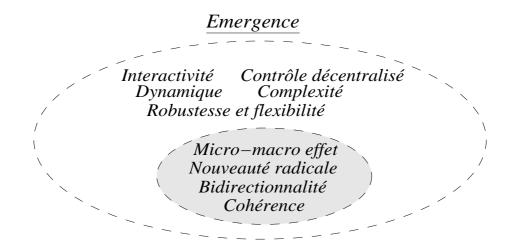

| 1.1  | Propriétés partagées entre l'auto-organisation et l'émergence                     | 19 |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Propriétés d'un système émergent                                                  | 20 |

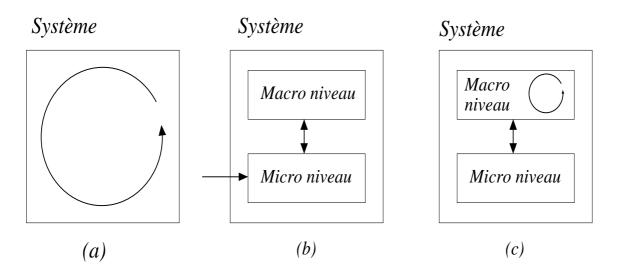

| 1.3  | Illustrations des systèmes auto-organisés et/ou émergents                         | 24 |

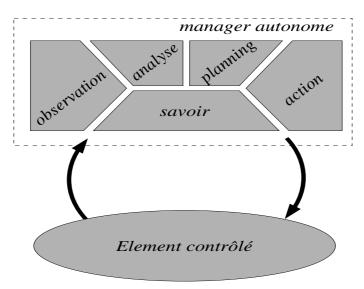

| 1.4  | Élément de base d'un système de calcul autonome - (autonomic element)             | 26 |

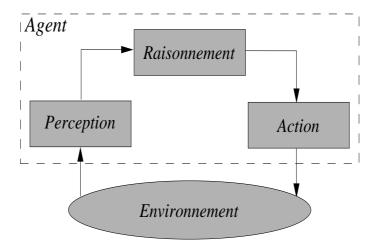

| 1.5  | Le schéma synoptique d'un « agent » d'un système MAS                              | 29 |

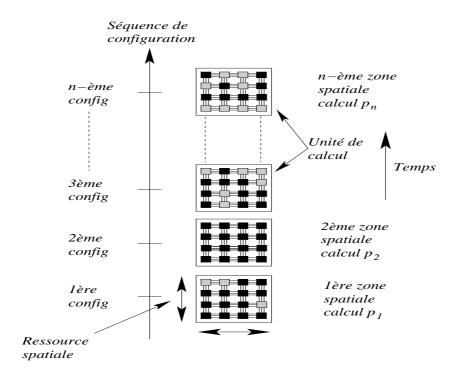

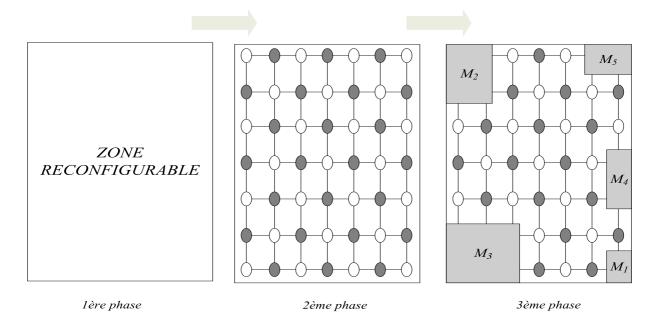

| 2.1  | Illustration de l'évolution spatio-temporelle d'une structure matérielle reconfi- |    |

|      | gurable dynamiquement de type FPGA                                                | 34 |

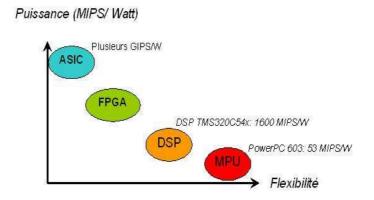

| 2.2  | Rapport performances / flexibilité pour les principales technologies              | 35 |

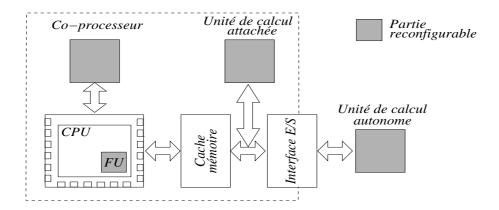

| 2.3  | Système reconfigurable à différents niveaux de couplage                           | 36 |

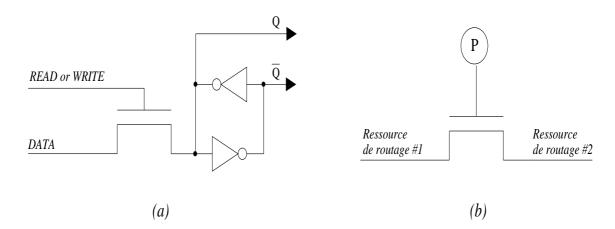

| 2.4  | a) Bit de programmation d'un FPGA à mémoire statique SRAM [Xil94] b)              |    |

|      | Connexion de routage programmable                                                 | 37 |

| 2.5  | a) Architecture globale d'un circuit <i>FPGA</i> , b) d'un bloc logique           | 37 |

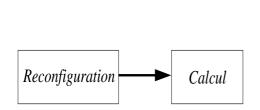

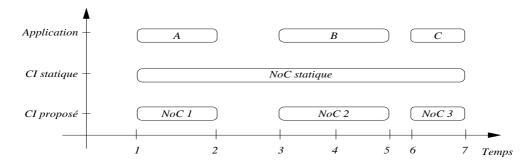

| 2.6  | Reconfiguration statique d'un circuit <i>FPGA</i>                                 | 38 |

| 2.7  | Mode de reconfiguration dynamique d'un circuit <i>FPGA</i>                        | 38 |

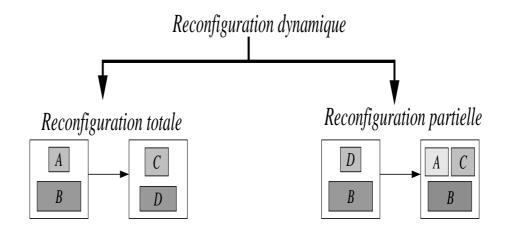

| 2.8  | Mode de reconfiguration dynamique d'un circuit <i>FPGA</i>                        | 39 |

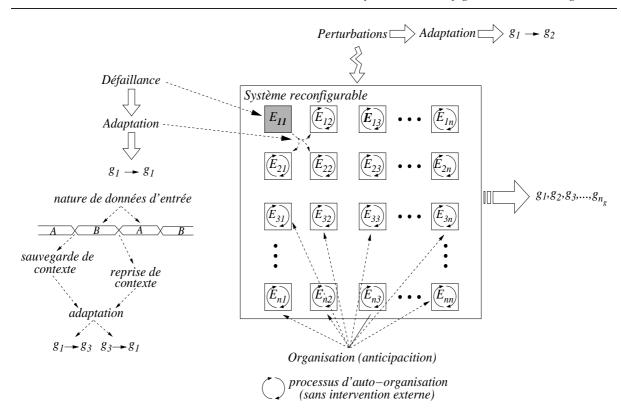

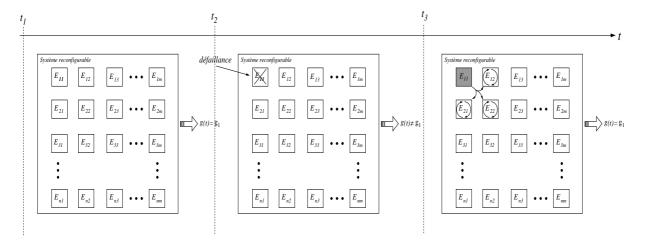

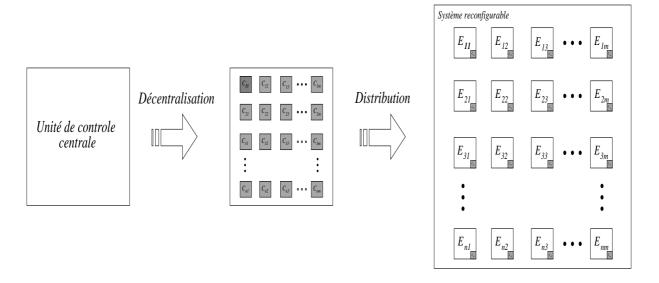

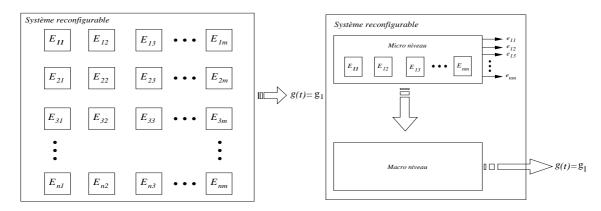

| 2.9  | Illustration des critères d'auto-organisation d'un système reconfigurable         | 41 |

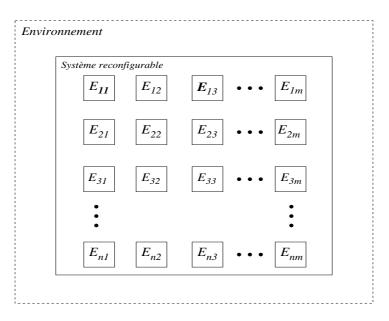

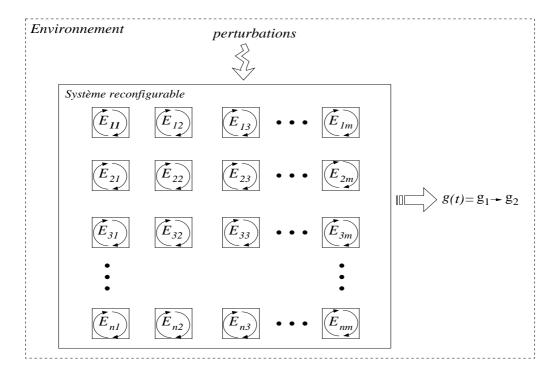

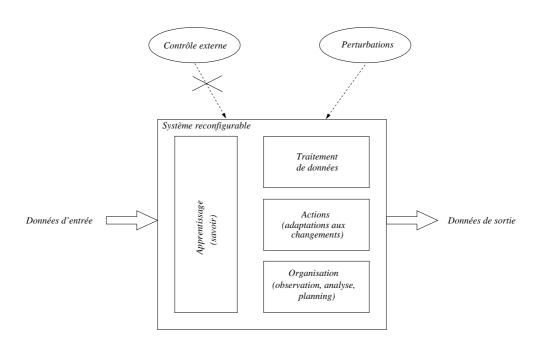

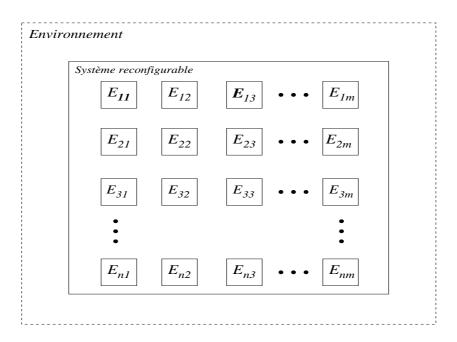

| 2.10 | Schéma synoptique global d'un système reconfigurable modulaire                    | 42 |

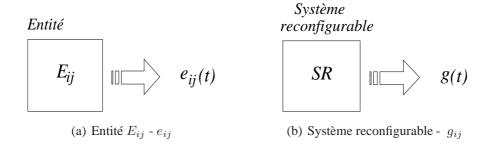

| 2.11 | Modélisation d'une Entité / fonction associée et d'un système auto-organisé /     |    |

|      | fonction principale associé                                                       | 42 |

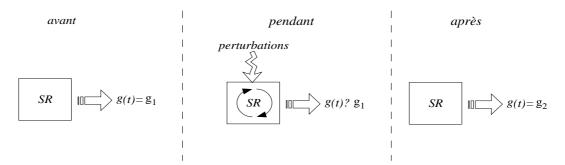

| 2.12 | Illustration de la propriété d'adaptabilité d'un système reconfigurable           | 45 |

| 2.13 | L'adaptation d'un système reconfigurable aux changements d'environnement          | 46 |

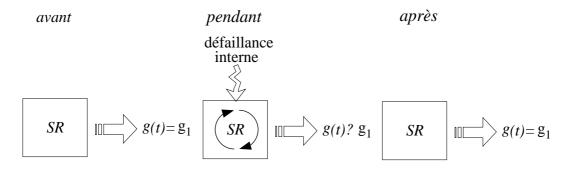

| 2.14 | Robustesse d'un système reconfigurable : une forme d'adaptabilité                 | 47 |

| 2.15 | Illustration de la propriété de robustesse d'un système auto-reconfigurable       | 48 |

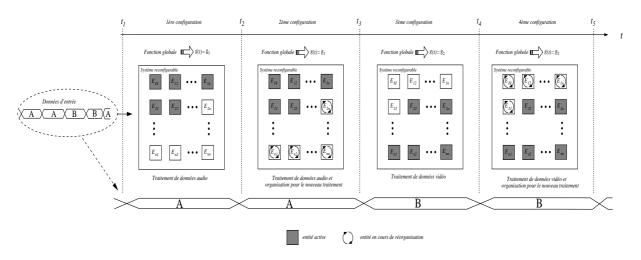

| 2.16 | L'anticipabilité d'un système reconfigurable à l'exemple d'un traitement audio    |    |

|      | / vidéo                                                                           | 50 |

| 2.17 | Illustration de la propriété d'autonomie d'un système reconfigurable              | 51 |

| 2.18 | Décentralisation de contrôle d'un système reconfigurable                          | 52 |

| 2.19 | Illustration de l'émergence d'un système reconfigurable                           | 53 |

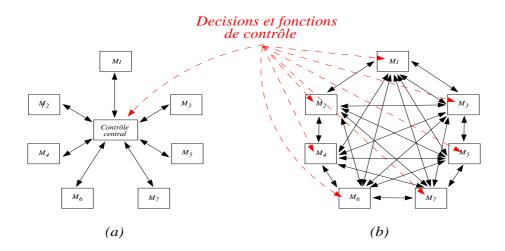

| 3.1  | Types de contrôle : a) centralisé et b) décentralisé                                        | 58 |

|------|---------------------------------------------------------------------------------------------|----|

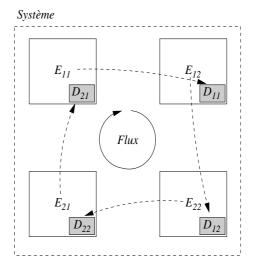

| 3.2  | Schéma synoptique global d'un système auto-organisé                                         | 59 |

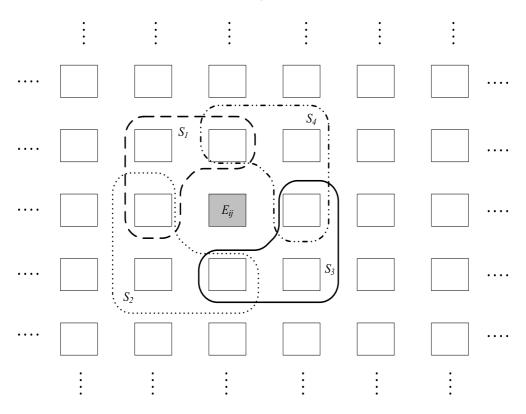

| 3.3  | Règle locale de substitution d'une entité $E_{ij}$ par les entités avoisinantes directes.   | 60 |

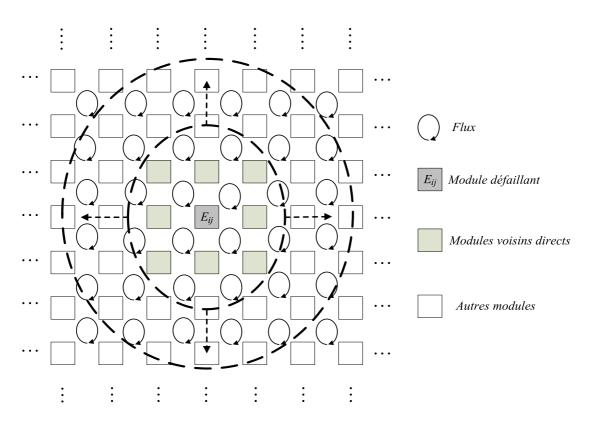

| 3.4  | Propagation d'une information de défaillance d'une entité locale $E_{ij}$ par un mé-        |    |

|      | canisme de flux informationnel local au sein d'un système auto-organisé proposé.            | 62 |

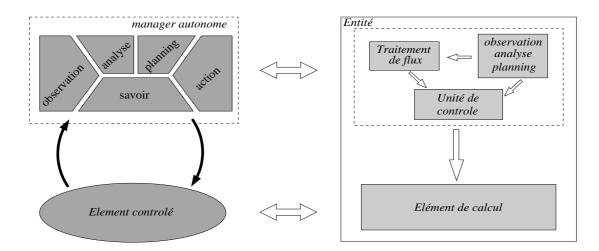

| 3.5  | Similitude d'un système autonome et d'un système auto-organisé proposé contrôlé             |    |

|      | par le mécanisme de <i>flux informationnel</i>                                              | 63 |

| 3.6  | Structuration en champs d'un flux informationnel couvrant un groupement de                  |    |

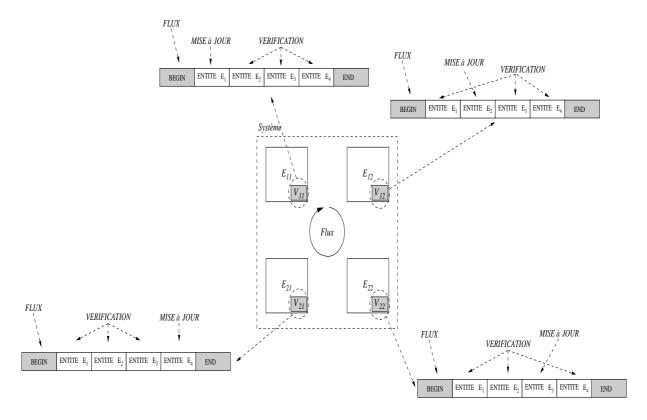

|      | quatre entités d'un système auto-organisé proposé                                           | 64 |

| 3.7  | Structuration en sous-champs d'un flux informationnel couvrant un groupement                |    |

|      | de quatre entités d'un système auto-organisé proposé                                        | 65 |

| 3.8  | Un extrait du graphe de contrôle du <i>flux informationnel</i> relatif aux requêtes         |    |

|      | de changement de modes de fonctionnement d'une entité d'un système auto-                    |    |

|      | organisé proposé                                                                            | 66 |

| 3.9  | Exemple de structure d'un descripteur d'une entité $E_{ij}$                                 | 68 |

| 3.10 | Mode d'intégration de blocs descripteurs dans les entités d'un système auto-                |    |

|      | organisé proposé                                                                            | 69 |

| 3.11 | Exemple de règle d'intégration de descripteurs dans un système auto-organisé                |    |

|      | à quatre modules                                                                            | 70 |

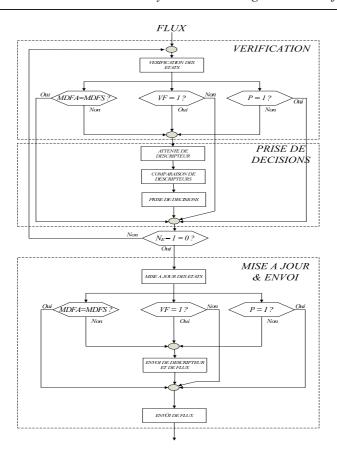

| 3.12 | Vérification de <i>flux informationnel</i> dans un système composé de quatre modules.       | 71 |

| 3.13 | Graphe flot de contrôle de module de vérification de <i>flux</i>                            | 72 |

| 3.14 | Illustration d'insertion d'une partie d'un descripteur dans un flux informationnel.         | 73 |

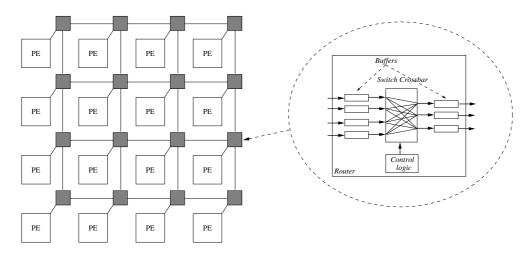

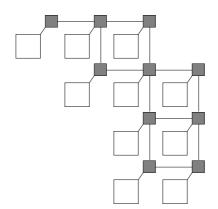

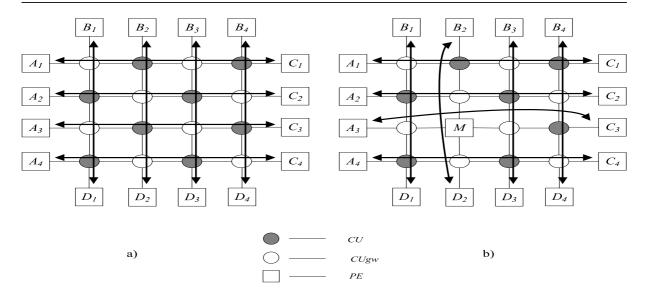

| 4.1  | Exemple d'une structure de <i>NoC</i> de type mesh                                          | 80 |

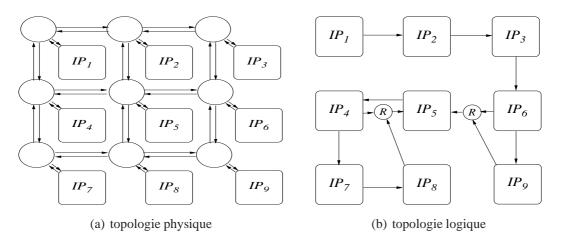

| 4.2  | Réseau sur puce dans le contexte de modèle de référence OSI                                 | 82 |

| 4.3  | Exemples de topologies des réseaux sur puce de type direct                                  | 83 |

| 4.4  | Exemples de topologies des réseaux sur puce de type indirect                                | 85 |

| 4.5  | Exemples d'une topologie <i>irrégulière</i> des réseaux sur puce basée sur la structure     |    |

|      | de type <i>mesh 2D</i>                                                                      | 86 |

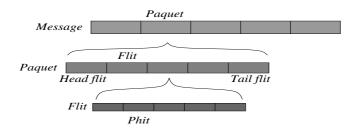

| 4.6  | Structure de message, paquets, flits et phits                                               | 86 |

| 4.7  | Illustration de reconfiguration de topologie dans un réseau ReNoC                           | 92 |

| 4.8  | Structure d'un réseau <i>NoC</i> de type <i>NOVA</i>                                        | 93 |

| 4.9  | Illustration de changement de topologie de <i>NoC</i> dans l'approche [RAS <sup>+</sup> 08] |    |

|      | pour différentes applications                                                               | 94 |

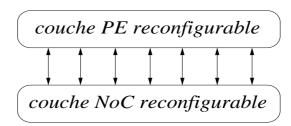

| 4.10 | Illustration de deux couches distinctes (NoC et PE) dans les approches NoC                  |    |

|      | reconfigurables                                                                             | 95 |

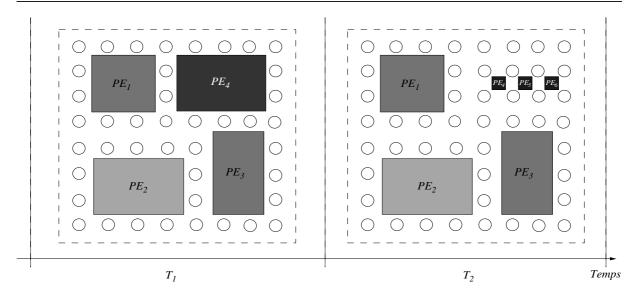

| 4.11 | L'approche DyNoC [BAM+05] : Illustration de l'évolution d'un réseau dyna-                   |    |

|      | mique reconfigurable dans le temps                                                          | 96 |

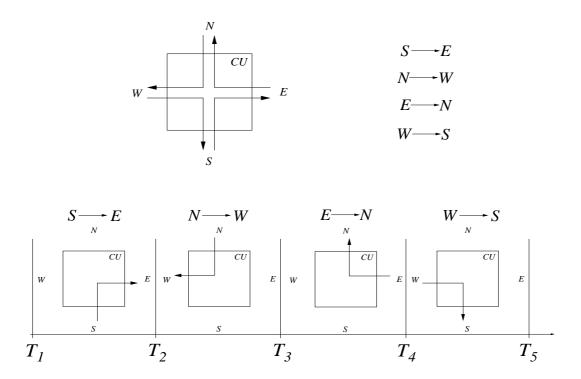

| 4.12 | Le format d'un paquet utilisé dans le <i>CuNoC</i>                                    | 97  |

|------|---------------------------------------------------------------------------------------|-----|

| 4.13 | L'architecture d'une unité de communication CU                                        | 98  |

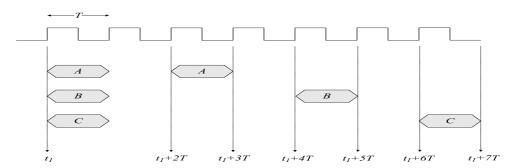

| 4.14 | Illustration de transfert de 3 paquets à travers un $CU$ et de la latence introduite. | 99  |

| 4.15 | Illustration de l'inadaptation des algorithmes de routage classiques tel que XY       |     |

|      | pour le <i>CuNoC</i>                                                                  | 100 |

| 4.16 | Interface physique entre deux <i>Unités de Communication (CU)</i>                     | 101 |

| 4.17 | Exemple d'établissement de connexion entre des modules à travers une $CU$ via         |     |

|      | les ports de données bidirectionnels partagés dans le temps                           | 102 |

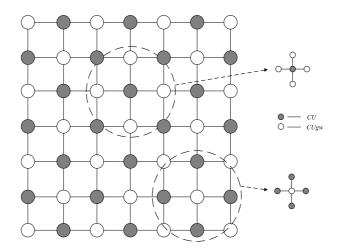

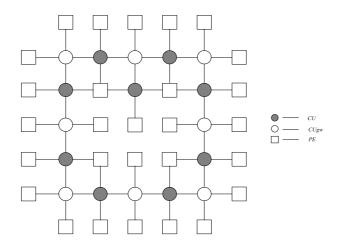

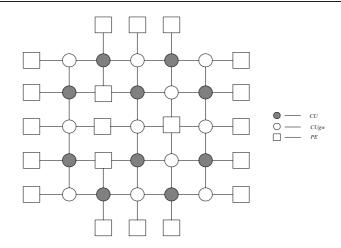

| 4.18 | Placement valide d'unités de communication $CU$ dans le $CuNoC$                       | 103 |

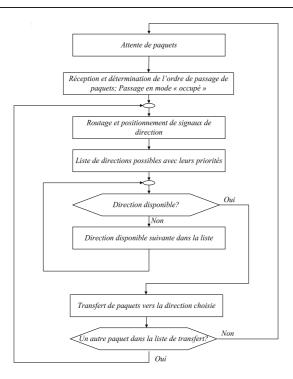

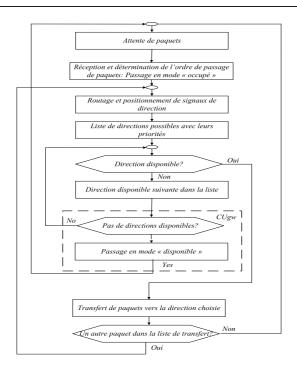

| 4.19 | Graphe flot de contrôle d'un $CU$ classique                                           | 104 |

| 4.20 | Graphe flot de contrôle d'un $CU$ « qui-cède-le-passage »                             | 105 |

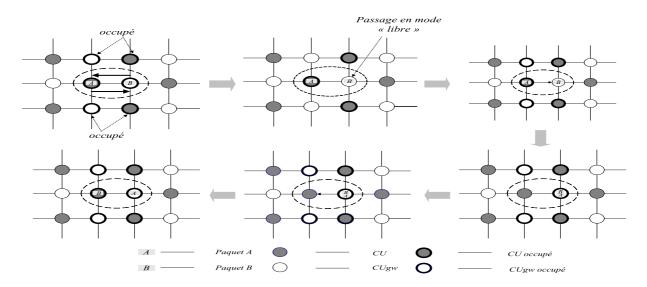

| 4.21 | Illustration d'une situation d'embouteillage dans un réseau CuNoC et sa réso-         |     |

|      | lution sur l'exemple d'échange de 2 paquets                                           | 105 |

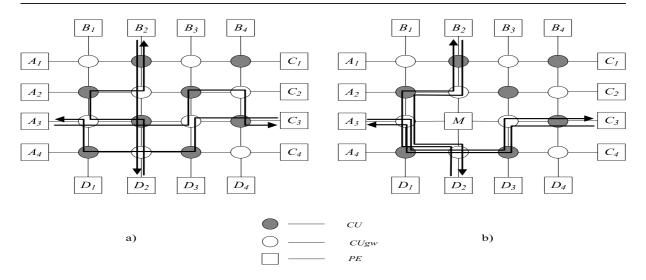

| 4.22 | Placement de modules dans le réseau CuNoC: a) invalide b) valide                      | 107 |

| 4.23 | Illustration de placement d'un nombre maximum de modules pour un réseau               |     |

|      | CuNoC m×n                                                                             | 108 |

| 4.24 | Placement préférable de modules dans le réseau CuNoC                                  | 109 |

| 4.25 | Trois phases de construction d'un réseau <i>CuNoC</i>                                 | 110 |

| 4.26 | Placement dynamique des modules dans un réseau CuNoC                                  | 110 |

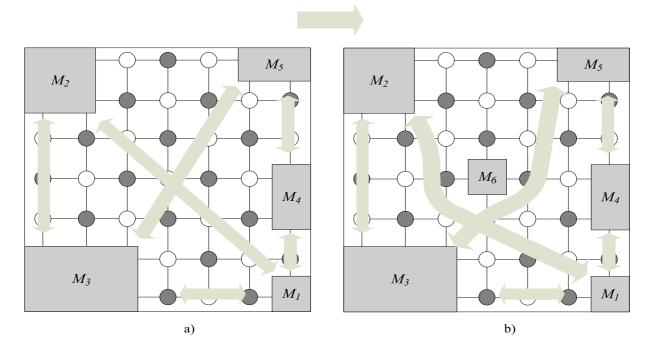

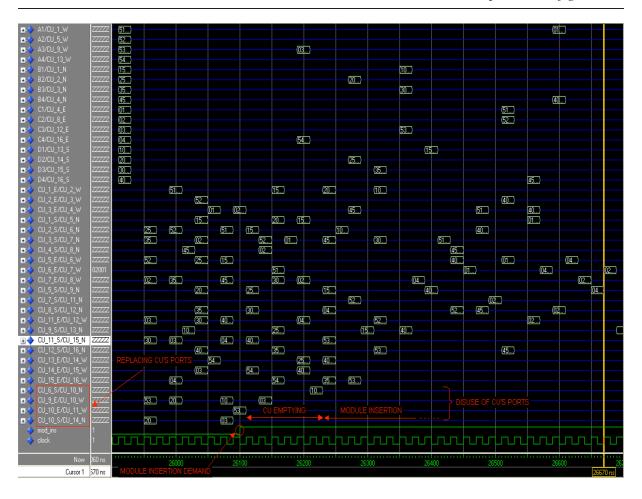

| 4.27 | Cas de simulation : a) Communication entre 16 modules via un $CuNoC$ 4×4              |     |

|      | b) Insertion d'un module de calcul dans un réseau $CuNoC$ de dimension $4\times4$     |     |

|      | reliant 16 modules de calcul                                                          | 112 |

| 4.28 | Le premier cas de simulation : communication entre 16 modules de calcul via           |     |

|      | un réseau $4\times4$                                                                  | 112 |

| 4.29 | Le deuxième cas de simulation : l'insertion d'un module de calcul dans le réseau      |     |

|      | $4\times4$ reliant 16 autres modules de calcul                                        | 113 |

| 4.30 | a) Illustration de communication entre 4 modules de calcul dans un réseau <i>Cu</i> - |     |

|      | NoC 4×4 utilisé pour la communication de 16 modules de calcul avant b) et             |     |

|      | après l'insertion du module de calcul                                                 | 114 |

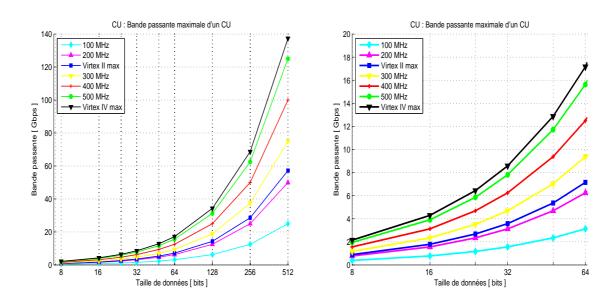

| 4.31 | Bande passante d'un $CU$ pour différents formats de données : a) de 4 à 512 bits      |     |

|      | (gauche) b) de 4 à 64 bit (droite)                                                    |     |

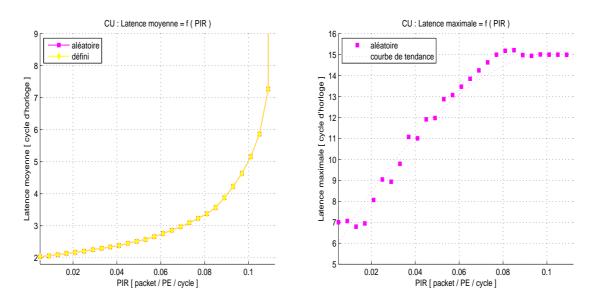

| 4.32 | Latences moyenne et maximale d'un routeur $CU$                                        | 117 |

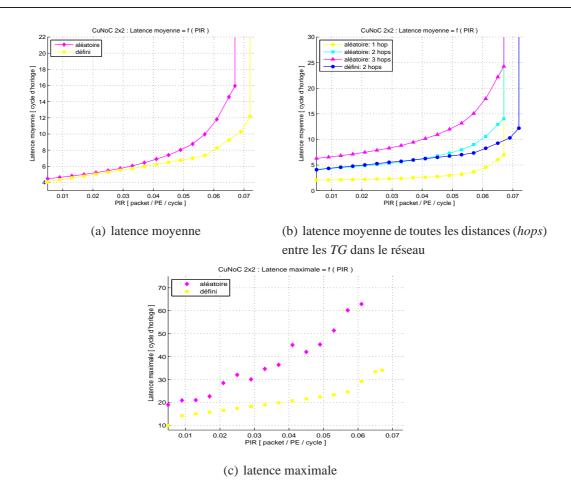

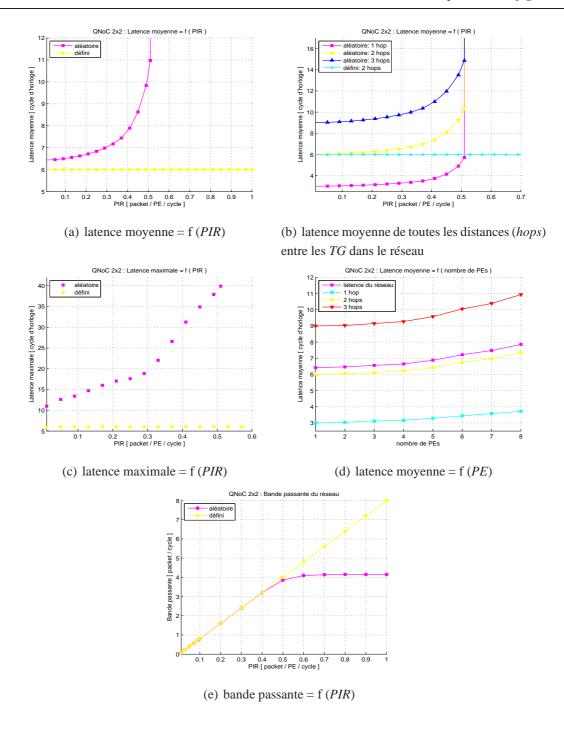

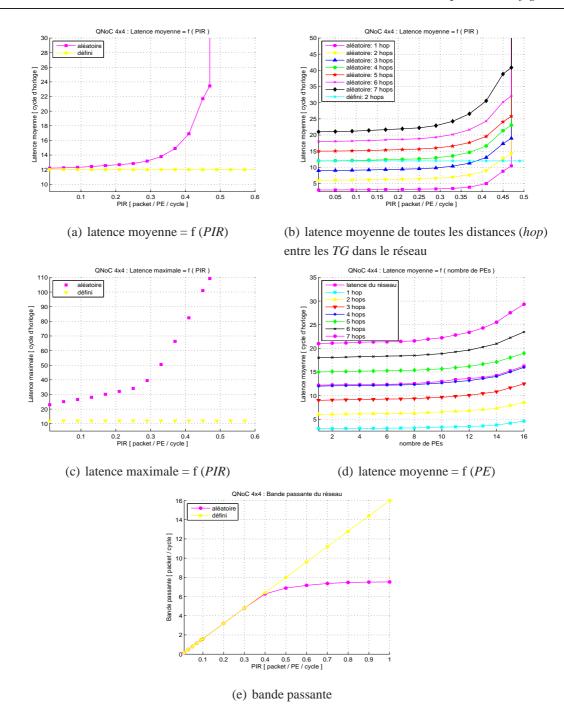

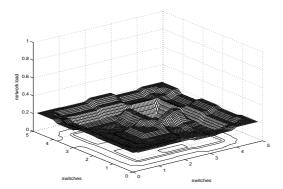

| 4.33 | Résultats d'évaluation de performances d'un réseau <i>CuNoC</i> 2x2                   | 119 |

| 4.34 | Résultats d'évaluation de performances d'un réseau $CuNoC$ $3 \times 3$               | 120 |

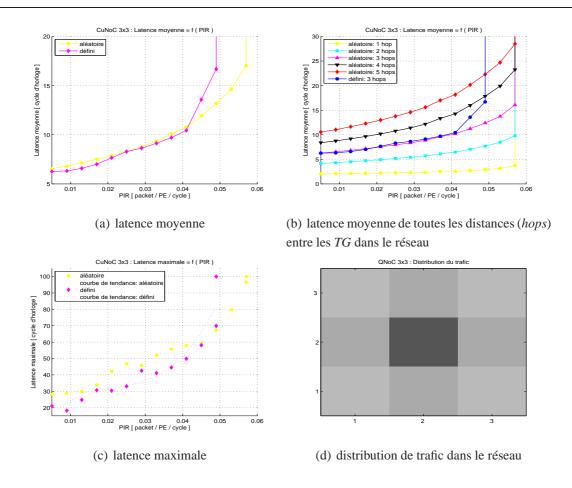

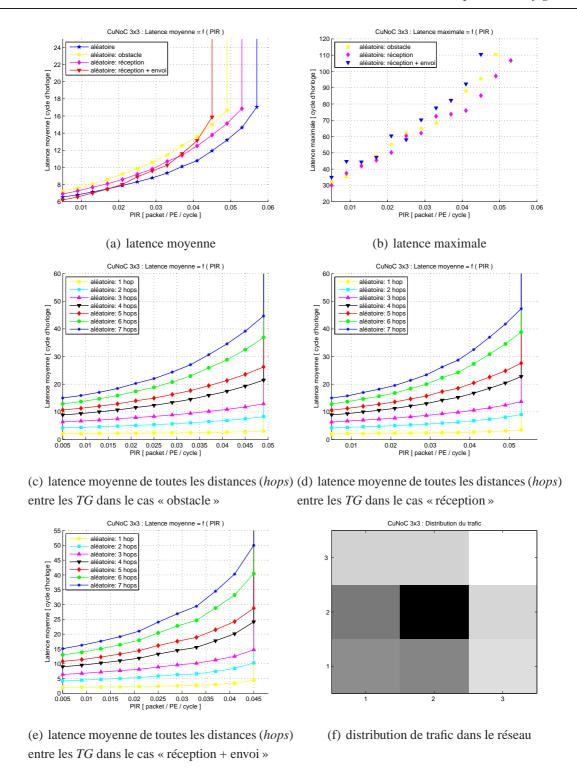

| 4.35 | Résultats d'évaluation de performances d'un réseau $CuNoC$ $3\times3$ et distribution |     |

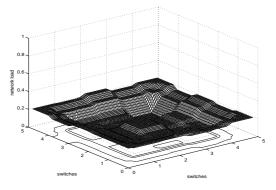

|      | du trafic dans le cas d'un $TG$ dynamique à la position $(2,2)$                       | 121 |

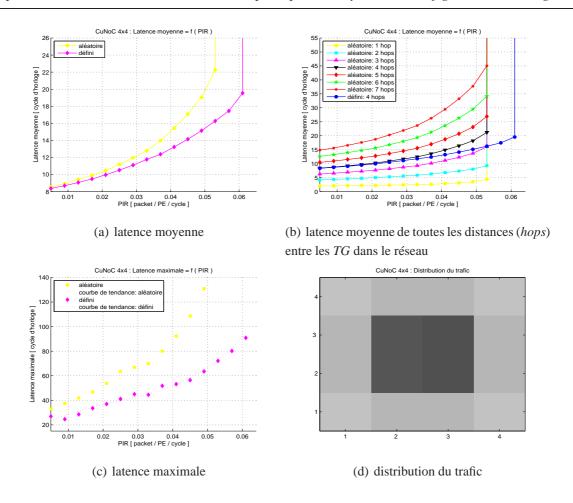

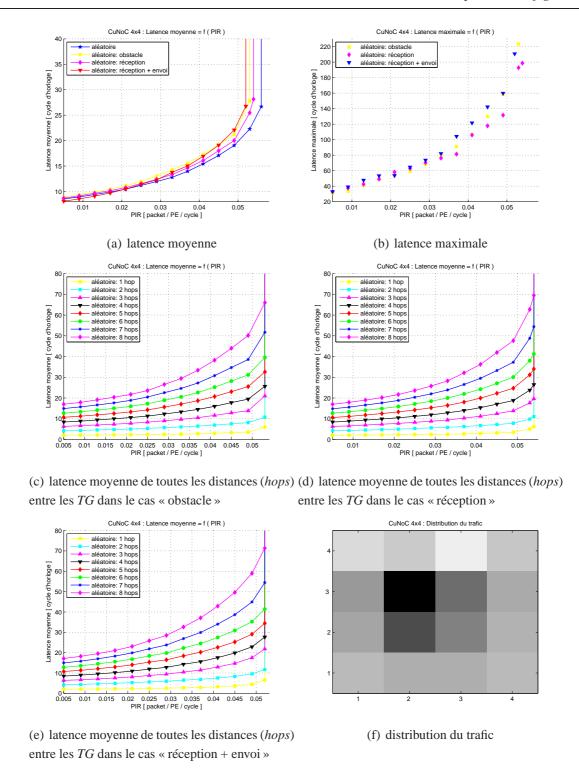

| 4.36 | Résultats d'évaluation de performances d'un réseau $CuNoC$ $4 \times 4$               | 122 |

| 4.37 | Résultats d'évaluation de performances d'un réseau <i>CuNoC</i> 4x4 et distribution du trafic dans le cas d'un <i>TG</i> dynamique | 123 |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

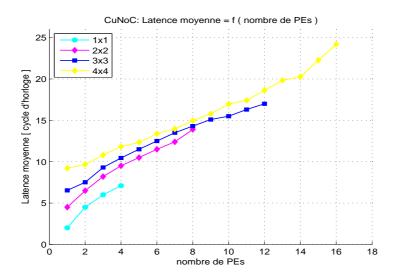

| 4.38 | Latence moyenne en fonction du nombre de modules de calcul ( <i>TG</i> ) connectés                                                 |     |

|      | au réseau et de sa taille                                                                                                          | 124 |

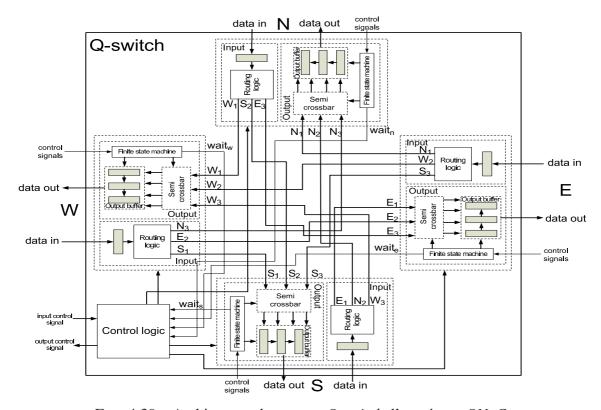

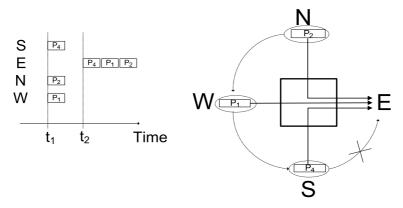

| 4.39 | Architecture du routeur <i>Q-switch</i> d'un réseau <i>QNoC</i>                                                                    | 126 |

|      | Politique d'arbitrage basée sur la règle de priorité à droite                                                                      |     |

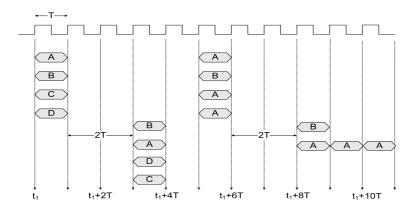

| 4.41 | Illustration de la latence introduite par un routeur <i>Q-switch</i>                                                               | 128 |

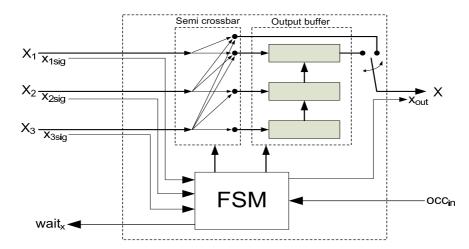

| 4.42 | Bloc « Logique de sortie » d'un routeur <i>Q-switch</i>                                                                            | 129 |

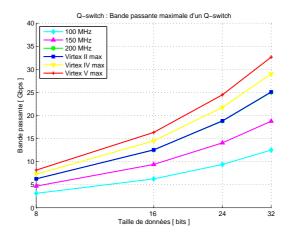

| 4.43 | Bande passante d'un routeur <i>Q-switch</i> pour différents formats de données de 4                                                |     |

|      | à 32 bits                                                                                                                          | 133 |

| 4.44 | Performances d'un routeur <i>Q-switch</i>                                                                                          | 134 |

| 4.45 | Résultats de l'évaluation de performances d'un réseau QNoC 2x2                                                                     | 135 |

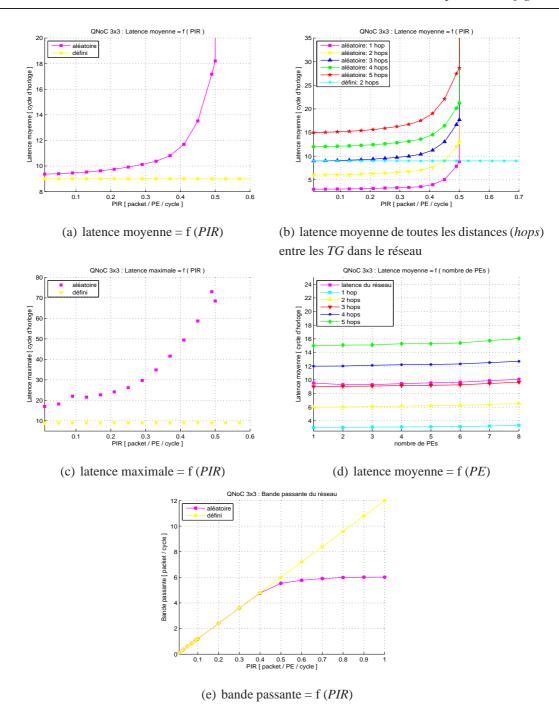

| 4.46 | Résultats de l'évaluation de performances d'un réseau <i>QNoC</i> 3x3                                                              | 137 |

| 4.47 | Résultats de l'évaluation de performances d'un réseau hétérogène QNoC 3x3 et                                                       |     |

|      | distributions de trafic avec ou sans module dynamique $TG$ placé                                                                   | 138 |

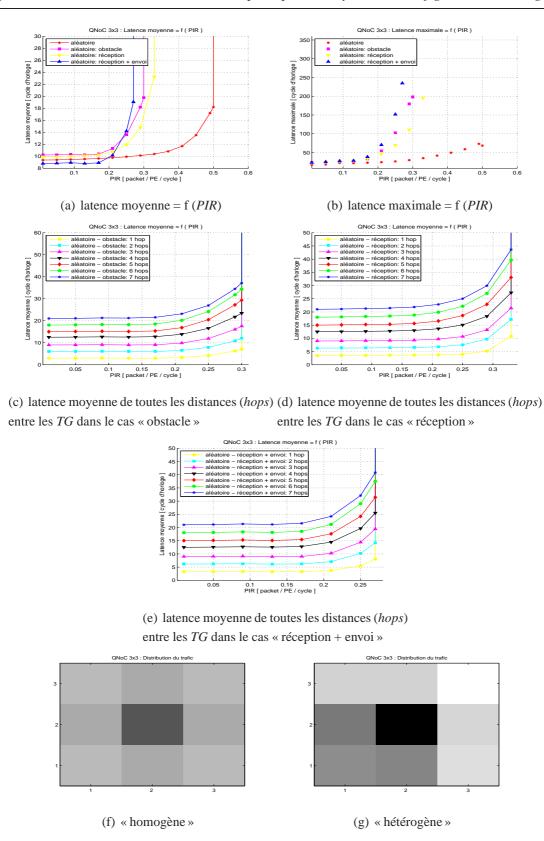

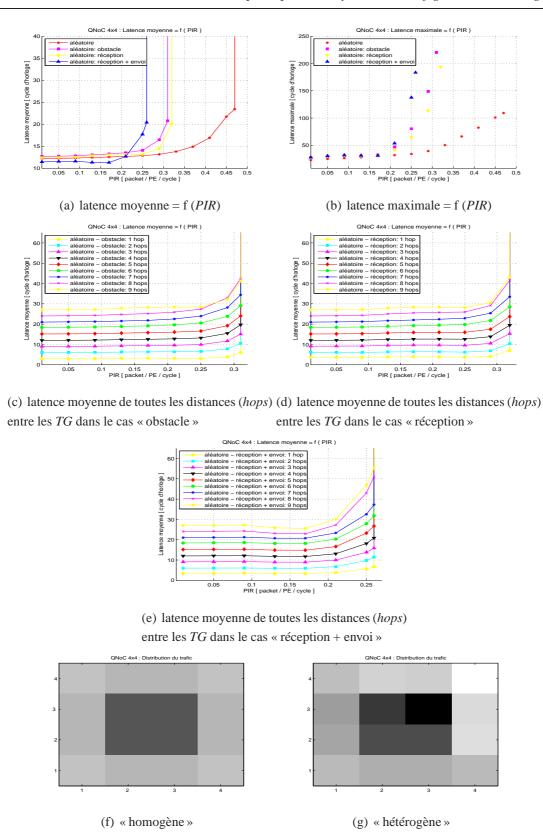

| 4.48 | Résultats de l'évaluation de performances d'un réseau <i>QNoC</i> 4x4                                                              | 139 |

| 4.49 | Résultats de l'évaluation de performances d'un réseau hétérogène QNoC 4x4 et                                                       |     |

|      | distributions de trafic avec ou sans module dynamique TG placé                                                                     | 140 |

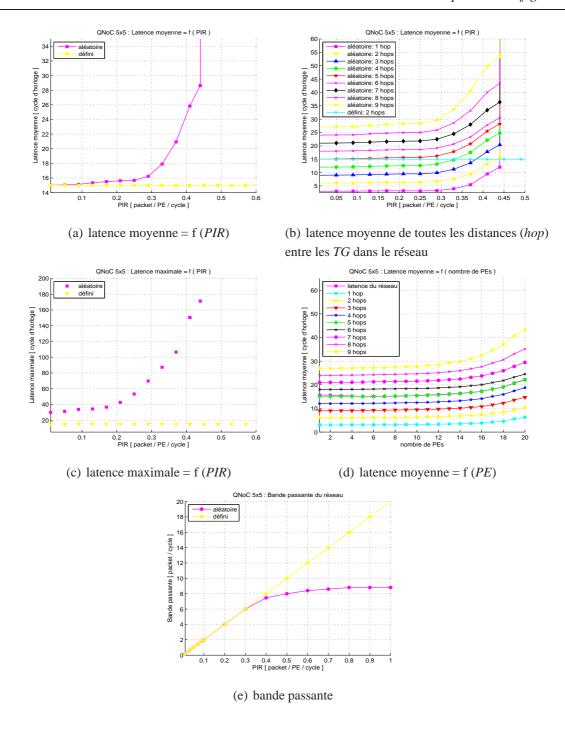

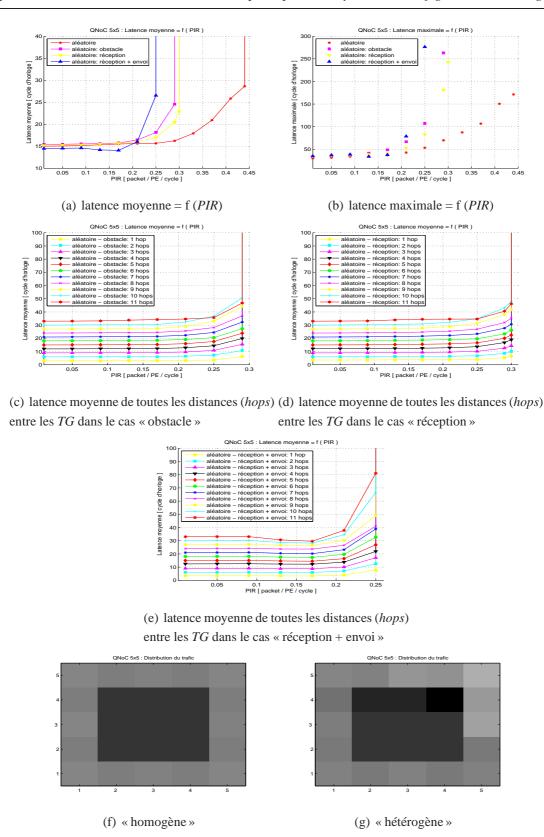

| 4.50 | Résultats de l'évaluation de performances d'un réseau <i>QNoC</i> 5x5                                                              | 141 |

| 4.51 | Résultats de l'évaluation de performances d'un réseau <i>hétérogène QNoC</i> 5x5 et                                                |     |

|      | distributions de trafic avec ou sans module dynamique TG placé                                                                     |     |

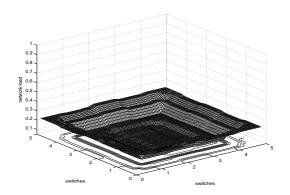

| 4.52 | Distribution du trafic d'un réseau $QNoC$ 5×5                                                                                      | 143 |

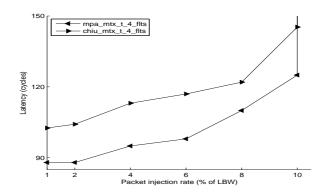

| 4.53 | Analyse comparative entre un réseau CuNoC et un réseau QNoC en terme de                                                            |     |

|      | performances                                                                                                                       |     |

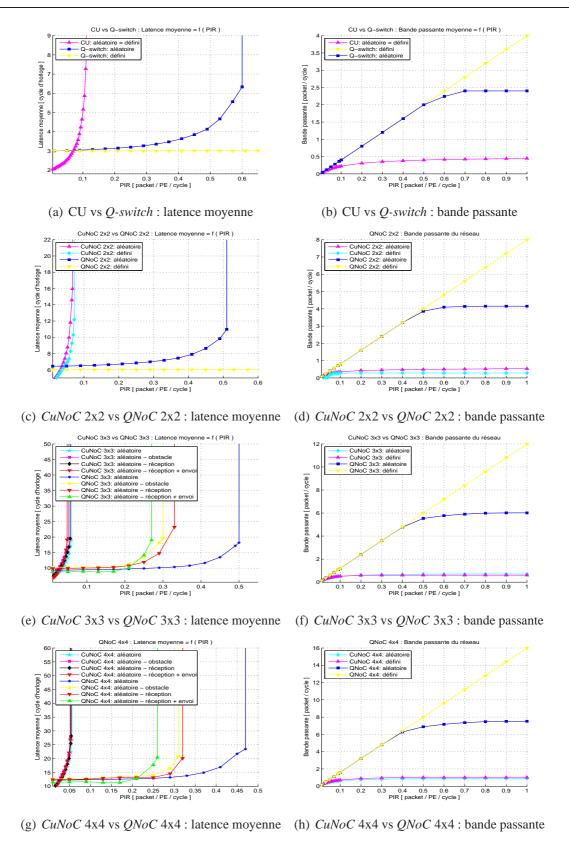

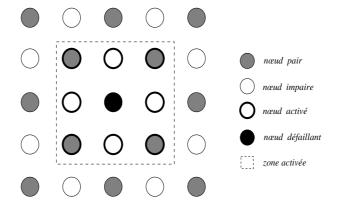

|      | Placement valide des nœuds de routage pairs et impairs dans un réseau                                                              |     |

|      | Exemple d'une zone activée                                                                                                         |     |

|      | Procédure utilisée pour former une zone activée                                                                                    | 152 |

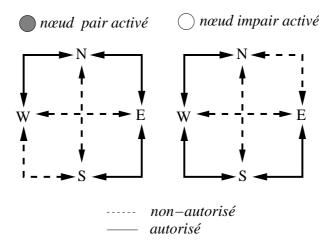

| 4.57 | Les directions d'acheminement de paquets non-autorisés par défaut dans les                                                         |     |

|      | nœuds de routage <i>activés</i>                                                                                                    |     |

|      | Pseudo-code de l'algorithme de routage MPA                                                                                         | 154 |

| 4.59 | Le routage dans un réseau utilisant l'algorithme MPA dans le cas de 3 nœuds                                                        | 155 |

| 4 60 | défaillants.                                                                                                                       |     |

|      | Channel dependency graph d'une zone activée de dimension 4 × 4                                                                     | 156 |

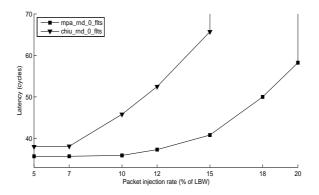

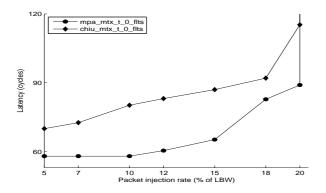

| 4.61 | Résultats de simulation pour un trafic <i>aléatoire</i> sans nœuds de routage dé-                                                  | 157 |

|      | faillants des réseaux basés respectivement sur les algorithmes MPA et MR                                                           | 15/ |

| 4.62 | Résultats de simulation pour un trafic à <i>matrice transposée</i> sans nœuds de routage défaillants des réseaux basés respectivement sur les algorithmes <i>MPA</i> et | 1.50 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

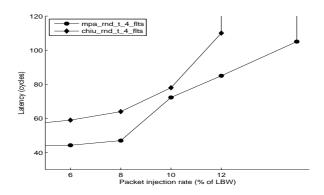

| 4.63 | MR                                                                                                                                                                      | 158  |

|      | rithmes MPA et MR                                                                                                                                                       | 158  |

| 4.64 | Résultats de simulation pour un trafic à <i>matrice transposée</i> dans des réseaux hétérogènes possédant 4 nœuds de routage défaillants basés respectivement sur       |      |

|      | les algorithmes MPA et MR                                                                                                                                               | 159  |

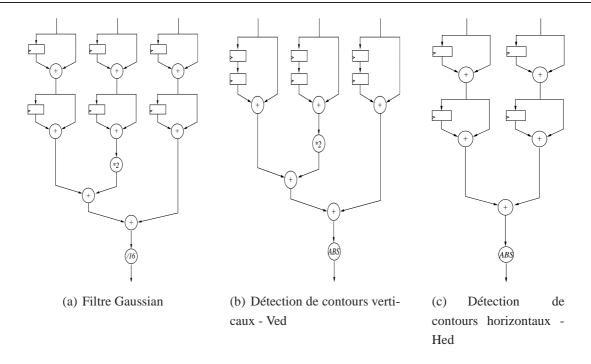

| 5.1  | Schéma synoptique d'un détecteur de contours de Sobel                                                                                                                   | 162  |

| 5.2  | Structure binomiale de détection de contours à base de l'opérateur de <i>Sobel</i>                                                                                      |      |

| 5.3  | Schéma synoptique d'un module                                                                                                                                           |      |

| 5.4  | Blocs des traitement principaux et de redondance des modules $M_1$ et $M_3$ - I                                                                                         |      |

| 5.5  | Blocs des traitements principaux et de redondance des modules $M_2$ et $M_4$ - II                                                                                       | 166  |

| 5.6  | Format de paquets de donnée du système auto-organisé applicatif proposé                                                                                                 | 166  |

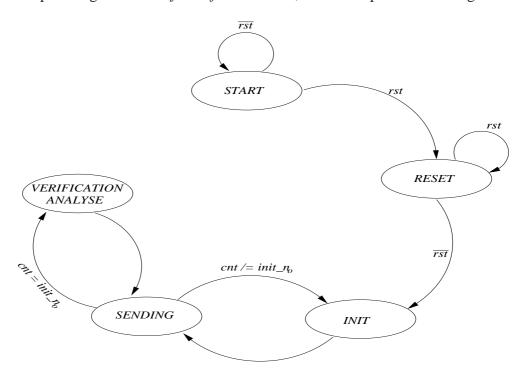

| 5.7  | Diagramme de transition du bloc de « vérification de flux »                                                                                                             | 167  |

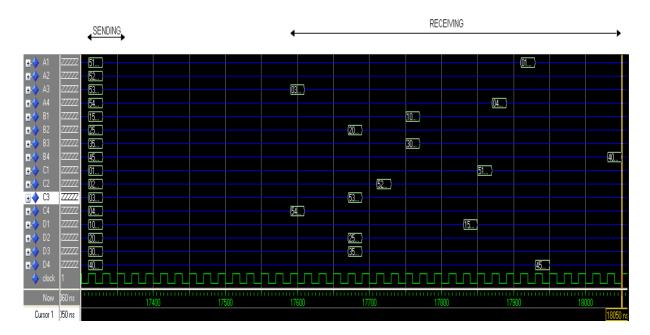

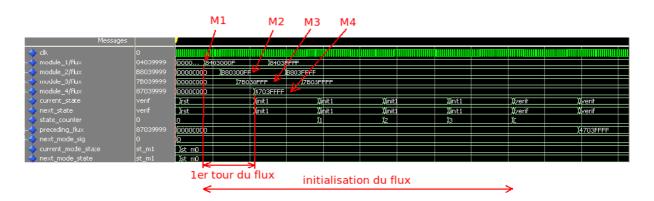

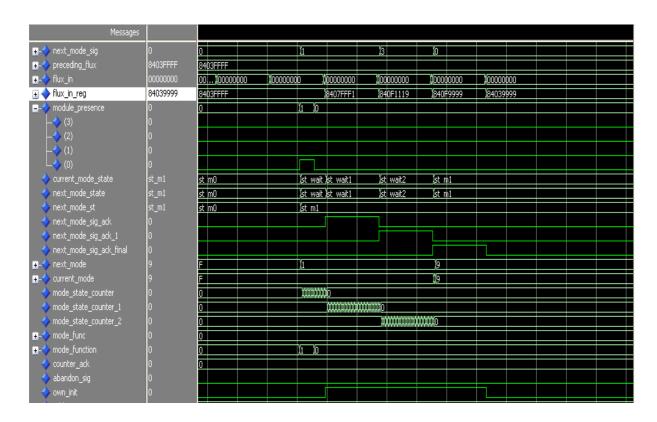

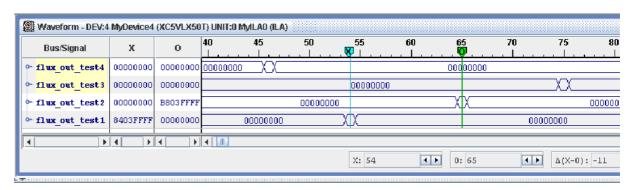

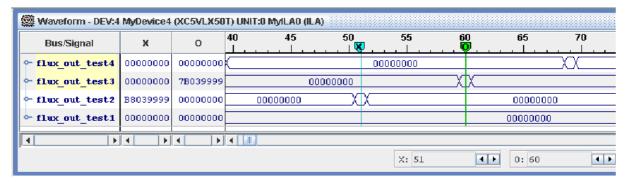

| 5.8  | Extrait de simulation de la phase d'initialisation et de création du <i>flux informa-</i>                                                                               |      |

|      | tionnel sous environnement Modelsim                                                                                                                                     | 169  |

| 5.9  | Extrait de simulation de la fin d'étape d'initialisation du flux informationnel                                                                                         | 169  |

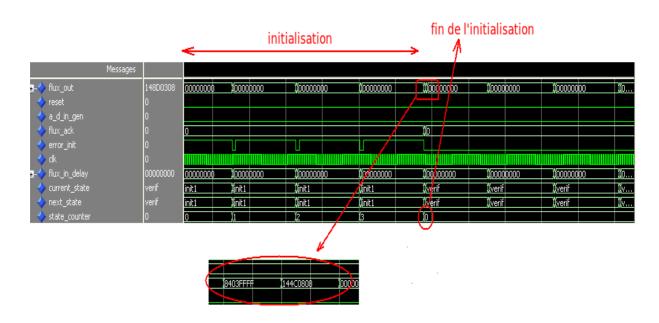

| 5.10 | Extrait du diagramme de transition du bloc FSM d'un module                                                                                                              | 171  |

| 5.11 | Extrait de résultats de simulation d'un passage d'un mode de fonctionnement à                                                                                           |      |

|      | un autre du système auto-organisé proposé                                                                                                                               | 173  |

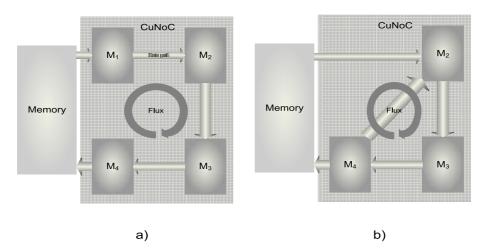

|      | Cas de simulation considéré (a) avant (b) et après la défaillance du module $M_1$ .                                                                                     | 174  |

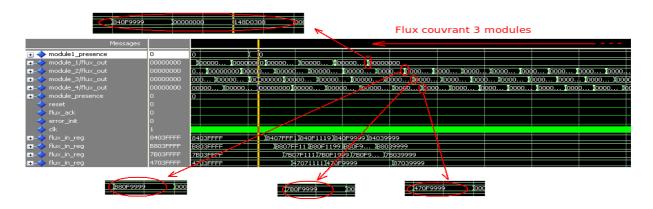

| 5.13 | Changements dans le flux informationnel en cours de négociations entre les                                                                                              |      |

|      | modules du système dans le cas d'une défaillance du module $M_1$                                                                                                        | 175  |

| 5.14 | Flux informationnel desservant uniquement les modules $M_2$ , $M_3$ et $M_4$ après                                                                                      |      |

|      | défaillance du module $M_1$                                                                                                                                             |      |

|      | •                                                                                                                                                                       | 177  |

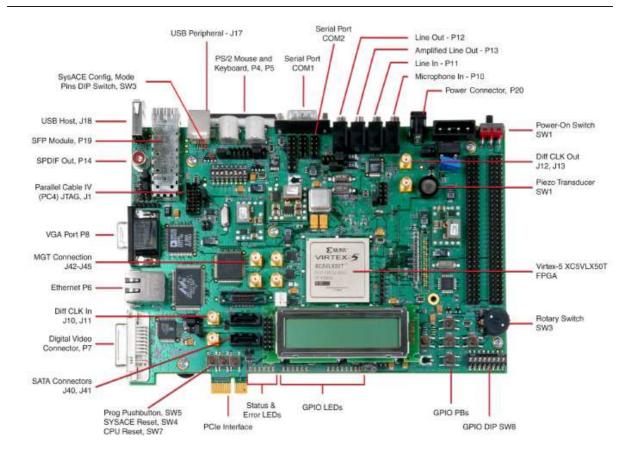

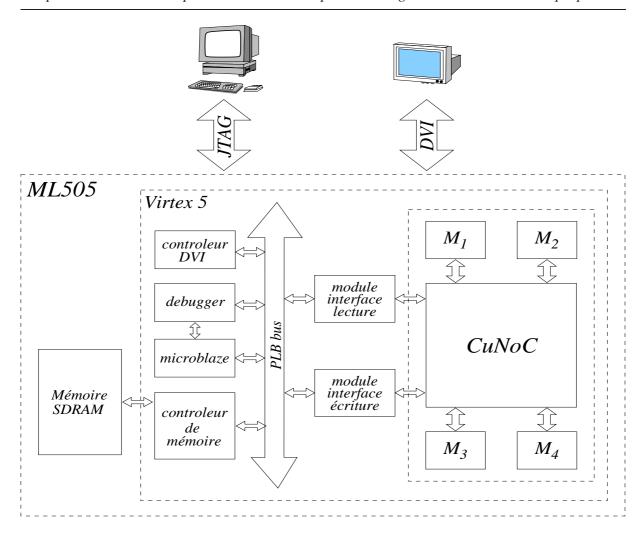

| 5.16 | Architecture globale du système auto-organisé de détection de contours d'images                                                                                         | 4.50 |

| c 15 | implantée dans la plateforme d'évaluation <i>ML505</i>                                                                                                                  | 178  |

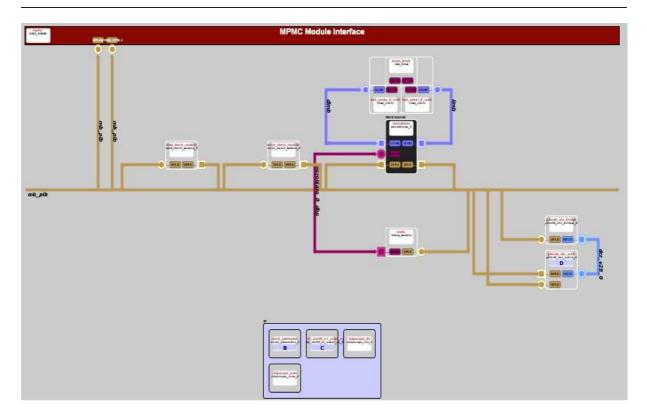

|      | Vue globale du système de détection de contours dans l'outil <i>EDK</i> de <i>Xilinx</i>                                                                                | 1/9  |

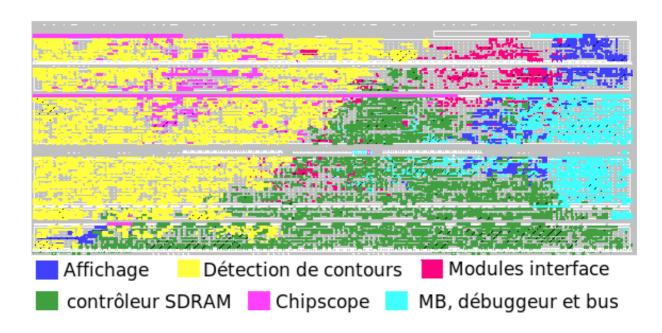

| 5.18 | Visualisation du <i>plan d'implantation</i> ( <i>floorplan</i> ) du système de détection de                                                                             | 100  |

| 5 10 | contours sur le circuit <i>FPGA</i> de la plateforme <i>ML-505</i>                                                                                                      | 180  |

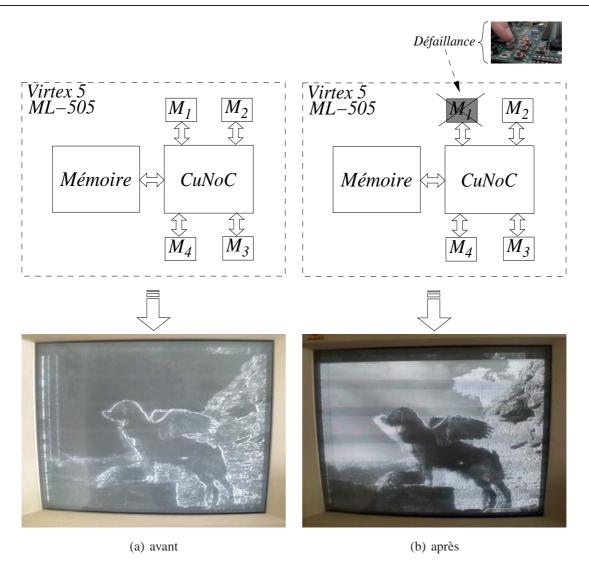

| 5.19 | Résultats expérimentaux de l'implantation du système auto-organisé de détection de contours et de sa robustesse face à une défaillance sous-système                     | 192  |

| 5 20 | Acquisition des valeurs réelles du <i>flux informationnel</i> par de l'outil <i>ChipScope</i>                                                                           | 102  |

| J.2U | Analyzer de Xilinx                                                                                                                                                      | 183  |

|      | THUM YOU GO THUMA                                                                                                                                                       | 100  |

# Liste des tableaux

| 3.1 | Comparaison des deux types de contrôle                                          | 58  |

|-----|---------------------------------------------------------------------------------|-----|

| 4.1 | Comparaison des interconnexions                                                 | 79  |

| 4.2 | Résultats de synthèse de routeurs $CU$ de différents formats de données sur     |     |

|     | FPGA Xilinx Virtex II et Virtex IV                                              | 115 |

| 4.3 | Résultats de synthèse sur les FPGA Xilinx Virtex II et Virtex IV, de réseaux    |     |

|     | CuNoC pour différentes dimensions et différents formats de données              | 116 |

| 4.4 | Évaluation de la latence de 125 000 paquets envoyés de manière aléatoire par    |     |

|     | un TG pour 4 différentes taille d'un réseau CuNoC                               | 125 |

| 4.5 | Résultats de synthèse de routeurs Q-switch de formats de données différents sur |     |

|     | les technologies FPGA Xilinx Virtex II, Virtex IV et Virtex V                   | 132 |

| 4.6 | Résultats de synthèse de réseaux QNoC de taille et de formats de données dif-   |     |

|     | férents sur les technologies FPGA Xilinx Virtex II, Virtex IV et Virtex V       | 132 |

| 4.7 | Évaluation des latences moyenne, minimale et maximale pour un trafic total de   |     |

|     | 125 000 paquets envoyés de manière aléatoire par un TG pour différentes tailles |     |

|     | d'un réseau <i>QNoC</i>                                                         | 145 |

| 4.8 | Résultats de comparaison en terme de ressources nécessaires pour l'implanta-    |     |

|     | tion des routeurs CU et Q-switch de différents formats de données sur FPGA      |     |

|     | Xilinx Virtex IV                                                                | 146 |

| 4.9 | Résultats de comparaison en terme de ressources nécessaires pour l'implanta-    |     |

|     | tion des réseaux CuNoC et QNoC de différente taille et pour différents formats  |     |

|     | de données sur FPGA Xilinx Virtex IV                                            | 146 |

| 5.1 | Modes de fonctionnement des modules du système auto-organisé                    | 172 |

| 5.2 | Résultats d'implantation sur la plateforme <i>ML-505</i>                        | 180 |

| 5.3 | Évaluation des performances du système global de détection de contours d'images |     |

|     | vidéo                                                                           | 184 |

### Résumé

Afin de répondre à une complexité croissante des systèmes de calcul, due notamment aux progrès rapides et permanents des technologies de l'information, de nouveaux paradigmes et solutions architecturales basées sur des structures auto-adaptatives, auto-organisées sont à élaborer. Ces dernières doivent permettre d'une part la mise à disposition d'une puissance de calcul suffisante répondant à des contraintes de temps sévères (traitement temps réel). D'autre part, de disposer d'une grande flexibilité et adaptabilité dans le but de répondre aux évolutions des traitements ou des défaillances non prévues caractérisant un contexte d'environnement évolutif de fonctionnement du système. C'est dans ce cadre que s'insèrent les travaux de recherche présentés dans cette thèse qui consistent à développer une architecture auto-organisée de type *Reconfigurable MPSoC (Multi processor System on Chip)* à base de technologie FPGA.

La stratégie de recherche proposée consiste à développer une approche architecturale mettant en œuvre le concept d'auto-adaptativité, d'auto-organisation par l'exploitation de la reconfiguration dynamique (RD) des circuits FPGA tout en recherchant à satisfaire la notion d'Adéquation Algorithme - Architecture. L'objectif de ces travaux est d'élaborer le principe d'une auto-organisation (AO) matérielle en vue d'aboutir à des architectures de calcul embarqué capables de s'auto-restructurer par reconfiguration, s'auto-gérer de manière autonome et sans contrôle externe tout en répondant à des contraintes multiples de conception ou de traitement (contrainte de temps ou puissance de calcul, flexibilité, tolérance aux fautes, etc.). L'approche architecturale de calcul embarqué auto-organisée proposée repose à la fois sur une structure de communication reconfigurable de type NoC (Network on Chip) adaptée à la technologie FPGA et sur des structures originales de communications informationnelles contribuant à mettre en œuvre les principes d'auto-adaptation, d'auto-organisation.

Le manuscrit de cette thèse est organisé de la manière suivante :

- Une première partie présente et identifie les principales caractéristiques du concept d'autoorganisation et sa transposition dans le domaine de la conception matérielle des systèmes embarqués à base de technologies reconfigurables. Plus précisément, dans un premier temps, nous

proposons une définition d'un système auto-organisé et ses principales propriétés associées

(adaptabilité, autonomie, robustesse, flexibilité, anticipabilité, contrôle décentralisé). Ensuite,

nous montrons l'intérêt de l'utilisation de la technologie reconfigurable dynamique des circuits

FPGA pour la mise en œuvre matérielle de systèmes possédant de telles propriétés. Nous recensons alors les principaux besoins pour leurs réalisations et nous montrons la nécessité d'élaborer d'une part de nouveaux concepts architecturaux basés sur des structures de communication

adaptées à la technologie reconfigurable FPGA. D'autre part, de développer des mécanismes d'apprentissage au cours du fonctionnement de tels systèmes.

- Ensuite, un nouveau concept architectural associé aux propriétés d'auto-organisation définies dans cette première partie est proposé. Cette approche architecturale est caractérisée par la mise en œuvre du principe d'auto-organisation à travers le développement matériel de nouvelles structures de communications informationnelles internes, circulaires localement et globalement au système auto-organisé proposé (notion de *flux* et de *descripteur*). Ce concept original permet des échanges d'informations entre les modules constituant le système, sans un contrôle centralisé et tout en générant une « conscience » interne parmi l'ensemble des entités le constituant, dans le but de répondre à tout changement ou évolution du système. Ce concept est également détaillé à travers un exemple concret du fonctionnement auto-organisé du système proposé, lors d'une défaillance temporaire ou permanente d'entités le constituant, par changement ou substitution fonctionnelle de ses modes de fonctionnement.

- La deuxième partie présente et détaille la conception d'une structure adaptée de communication sur puce (*Network on Chip NoC*) pour les systèmes reconfigurables auto-organisés à base de technologie FPGA. Après avoir rappelé les principales caractéristiques des réseaux sur puce et justifié les raisons pour lesquelles les NoC « classiques » actuels ne sont pas adaptés à des systèmes reconfigurables auto-organisés, nous proposons deux nouvelles architectures de routeur sur puce (*CuNoC* et *QNoC*) correspondant à une évolution pour architecture NoC adaptée aux systèmes reconfigurables. Une analyse et une comparaison détaillées de leurs principaux avantanges et inconvénients sont également présentées. Un algorithme de routage spécifiquement développé pour une architecture reconfigurable NoC associée à ces routeurs est également détaillé.

- En vue de valider l'approche architecturale globale du système auto-organisé proposé et associé aux concepts, mécanismes et structures de communication sur puce adoptés, nous présentons les résultats de l'exécution d'une auto-organisation de notre architecture dans le cas d'un traitement d'images temps réel défaillant au cours du temps tout en maintenant une *Adéquation Algorithme Architecture*. L'objectif principal de cette partie est une validation expérimentale de l'ensemble des aspects conceptuels abordés au cours de ces travaux de recherche.

- Enfin, nous discutons et dressons le bilan de nos travaux en présentant les apports des concepts architecturaux proposés et en dégageant les perspectives de ce travail ainsi que les amélioration à apporter.

**Mots-clés:** Auto-adaptation et Auto-organisation matérielles, Calcul embarqué, Systèmes reconfigurables, Réseaux sur puce reconfigurables (RNoC), Algorithme de routage tolérant aux fautes, FPGA.

### **Abstract**

The growing complexity of computing systems, mostly due to the rapid progress in Information Technology (IT) in the last decade, imposes on system designers to orient their traditional design concepts towards the new ones based on self-organizing and self-adaptive architectural solutions. On the one hand, these new architectural solutions should provide a system with a sufficient computing power, and on the other hand, a great flexibility and adaptivity in order to cope with all non-deterministic changes and events that may occur in the environnement in which it evolves. Within this framework, a reconfigurable MPSoC self-organizing architecture on the FPGA reconfigurable technology is studied and developed during this PhD.

The proposed research methodology is there to develop a hardware architectural approach based on the concepts of self-adaptivity and self-organization by exploiting the property of dynamic reconfiguration of the FPGA circuits and by seeking to satisfy the *Algorithm / Architecture* matching. The objective of this work is to integrate the main properties of the self-organization principle in the FPGA reconfigurable computing architectures. These architectures should be capable of self-restructuring through reconfiguration and self-managing in an independent manner and without any external controls while satisfying multiple design and processing constraints (real-time constraints, computing power, flexibility, fault tolerance, etc.). The proposed self-organizing hardware architecture is based on a reconfigurable *Network-on-Chip* (*NoC*) structure adapted to the FPGA technology and on a hardware design approach allowing integration of self-managing properties into the hardware architecture.

This manuscript is organized as follows:

- In the first part, we first of all identify and detail the main properties of the self-organization. After that, these properties are transposed to the domain of reconfigurable hardware architectures. Here, we propose definitions of a self-organizing system and its main properties (adaptability, autonomy, robustess, flexibility, anticipation, decentralized control). Then, we show the interest of using the dynamically reconfigurable FPGA technology for a hardware implementation of self-organizing properties. We also list the main needs for these implementations: a new hardware design approach based on self-organizing properties, a reconfigurable communication structure adapted to the FPGA circuits of type NoC and a learning mechanism allowing the systems to learn from their experiences.

- Then in the second part, we propose a new hardware design approach based on the self-organizing properties (defined and detailed in the first part). This approach is characterized by two structures: a dynamic circular structure called *flux* and a static descriptive structure called *descriptor*. The use of this hardware design approach in hardware systems allows an exchange of information between the systems' modules without any external control and also allows handling and responding to all environnemental changes and events firstly at the local level,

and secondly, if necessary, at the system's level. This design approach is detailed in the case of a permanent or transient fault of a system's module where the faulty module is functionnally replaced by its direct neighbouring modules.

- A communication structure adapted to the FPGA circuits of type NoC is presented and detailed in the third part of this manuscript. Fistly, we give an overview of basic NoC approaches and their main characteristics as well as the main reasons why these classic NoCs are not very suited for the use in the FPGA circuits. Then, we propose two new router architectures (*CuNoC* and *QNoC*) for the FPGA reconfigurable systems. The main advantages and drawbacks of these two architectures and their comparison are detailed and given in this part. In the final section of this part, a routing algorithm used for both architectures is presented and discussed.

- In order to validate experimentally all the aspects proposed in the previous parts, we applied them to an image processing application which was implemented and executed on an FPGA platform. We present the main steps and details of the implementation of the proposed hardware design approach into the given application. The experimental results are also discussed as well as some performance evaluations of the given application.

- In the last part, we discuss a summary of this work and we present its main contributions. Some perspectives and future work based on this research are also given in this part.

**Keywords:** Self-organization and self-managing in hardware, Embedded computing, Reconfigurable systems, Reconfigurable Network-on-chips, Fault-tolerant routing algorithm, FPGA

### Glossaire

AO: Auto-Organisation

**ASIC**: Application Specific Integrated Circuit,

CoNoChi: Configurable Network-on-Chip

**CPU**: Central Processing Unit

CS: Circuit Switching

**DyNoC**: Dynamic Network on Chip

**FPGA**: Field Programmable Gate Array,

**ICAP**: Internal Configuration Access Port

**LUT**: Look Up Table

**MPSoC**: Multiprocessor System-on-Chip

NI: Network Interface

**OSI**: The Open Systems Interconnection Reference Model

**PE**: Processing Element **PIR**: Packet Injection Rate

**PS**: Packet Switching

**QoS**: Quality of Service

**RD**: Reconfiguration Dynamique,

ReNoC: Reconfigurable NoC

**SAF**: Store-and-Forward

SAR: Système Auto-organisé Reconfigurable

**SNS**: Smart Network Stack

**SoC**: System on Chip,

**SRAM**: Static Random Acces Memory

ST: Switching Technique

**VCT**: Virtual Cut Through

**WS**: Wormhole Switching

## Introduction générale

### 1 Contexte général

Grâce aux progrès de la microélectronique, les technologies de l'information ont pénétré tous les aspects de notre vie quotidienne. En effet, l'avènement des circuits intégrés, permettant de réaliser des fonctions de plus en plus complexes, des traitements de plus en plus rapides tout en consommant de moins en moins d'énergie et ainsi permettre une portabilité, a profondement changé nos modes de vie. De nos jours, nous disposons de nouveaux dispositifs dits « concentré de technologie » regroupant sur quelques centimètres carrés une variété de fonctions complexes (codeur-décodeur *GSM*, décodeur *MP3*, *MPEG4*, *GPS* etc.), d'utilité quotidienne et présentés sous forme de matériel de poche. Ainsi, avec la miniaturisation à outrance et l'ère du développement de la nanoélectronique où la dimension caractéristique devient de l'ordre de dizaine nanomètres, les tendances actuelles dans la production et la consommation massive de ces « bijoux technologiques » ne cessent de croître et d'occuper une place de plus en plus importante dans nos modes de vie sociétale dite « moderne ».

Afin de répondre à cette demande massive, les concepteurs des circuits intégrés ont recours à la conception et à la fabrication de circuits spécifiques *ASIC*, qui permettent une solution d'intégration maximale par rapport au progrès technologique du moment. Cependant, généralement ce type de conception et de fabrication s'effectue au détriment de coûts fixes, de temps et de coûts de développement élevés et d'un degré de flexibilité très faible. En effet, la solution *ASIC* n'est viable que pour un nombre restreint d'utilisations. Une autre solution disposant d'une plus grande flexibilité, des performances acceptables et d'un coût nettement moins élevé par rapport aux *ASIC*, est présentée par la technologie reconfigurable de type *FPGA*. Grâce à la versatilité de ces circuits *FPGA*, les systèmes microélectroniques à base de ces technologies apportent une plus grande flexibilité. De plus, ils résolvent les principaux inconvénients des *ASIC* grâce à leurs facilités d'utilisation et leur rapidité de mise en œuvre (prototypage) qui ont fortement contribué à leur large succès ces dernières décennies au point de remplacer les *ASIC* de densité en termes de portes logiques d'environ un million et pour des fabrications de petites et moyennes séries. Toutefois l'utilisation de ces systèmes est limitée par leur taille et par leurs performances équivalentes à environ un tiers de celles des circuits *ASIC*.

Actuellement, la technologie reconfigurable dynamiquement de type FPGA est considérée comme une nouvelle alternative pour la réalisation d'architectures de traitement numérique de l'information [SW01]. En effet, elle permet de mettre en œuvre le paradigme du concept de « calcul reconfigurable ». Bien que ce concept soit déjà relativement ancien [EV62], la démocratisation de la technologie FPGA a conduit à un regain d'intérêt pour l'exécution d'une stratégie de calcul reconfigurable. En pratique, cela s'est traduit initialement par l'association de ces technologies à un processeur pour évoluer de nos jours vers un couplage plus étroit se traduisant par l'intégration d'une matrice FPGA et de processeurs sur une même puce [BRM<sup>+</sup>99, Tan01]. L'objectif est de profiter simultanément des performances d'une technologie permettant une logique câblée tout en gardant une forte flexibilité à travers la disposition d'une structure microprogrammée [CH02]. Avec l'évolution actuelle des systèmes complets intégrant des modules de nature différente sur une même puce (SoC - System on a chip), les technologies reconfigurables deviennent primordiales. En effet, les SoC ayant à l'origine une flexibilité matérielle limitée (structure de type ASIC) ont besoin à la fois de gérer leurs fonctionnements de manière autonome et de s'adapter à des modifications de l'environnement dans lequel ils évoluent. C'est dans ce contexte que la technologie FPGA permet une flexibilité à travers des phases de reconfiguration dynamique (globales ou partielles) tout en conservant un minimum de performances. Cette flexibilité s'exprime à travers des changements spatio / temporels de la structure du circuit permettant ainsi une grande souplesse matérielle [Tan01].

### 2 Motivation

Les systèmes de traitement d'information, étant de plus en plus complexes et hétérogènes, deviennent difficilement appréhendable. Ceci est dû notamment au progrès rapide en technologie de l'information au cours de ces dernières années. En effet, les besoins en terme de puissance de calcul et de traitement ne cessent d'augmenter. Afin de faire face aux nouveaux besoins et aux nouvelles exigences, de nouveaux paradigmes et solutions architecturales basées sur des structures auto-adaptatives, auto-organisées sont à élaborer. Ces nouvelles approches doivent permettre aux systèmes de faire face de manière plus autonome et plus flexible à tous les changements dynamiques prévus et imprévus. Des approches architecturales basées sur des mécanismes d'auto-organisation et inspirées du milieu naturel caractérisé par une organisation spontanée, s'imposent comme des solutions logiques à ces nouveaux challenges. Ces nouvelles approches doivent permettre d'une part la mise à disposition d'une puissance de calcul suffisante répondant à des contraintes de temps sévères (traitement temps réel); d'autre part, de disposer d'une grande flexibilité et adaptabilité dans le but de répondre aux évolutions des traitements ou des défaillances non prévues caractérisant un contexte d'environnement évolutif de fonctionnement du système.

Les technologies reconfigurables de type FPGA ont permis de répondre dans une certaine mesure à l'optimisation des ressources matérielles tout en garantissant une puissance de calcul suffisante pour des applications temps réel. L'atout principal d'une telle solution technologique est l'apport d'une flexibilité permettant des traitements adaptés. Cependant, il ne demeure pas moins déterministe dans la mesure où la conception basée sur cette technologie doit planifier les calculs successifs à mettre en œuvre. Or, dans le cas d'un traitement de flot de données non déterministe où une évolution non précise et non connue des traitements existants, une simple solution architecturale reconfigurable ne permet pas une réponse adaptée à ces traitements évolutifs. Néanmoins, la reconfigurabilité dynamique des technologies FPGA est sans doute l'aspect le plus prospectif des travaux autour des systèmes adaptatifs et auto organisés. Afin que le concept d'auto-organisation soit utilisé et appliqué dans un système sur puce reconfigurable, des adaptations du concept d'auto-organisation doivent être menées en prenant en compte les propriétés des technologies reconfigurables.

Actuellement, la plupart des travaux portant sur la conception d'architectures reconfigurables dynamiquement sont destinés à une gamme d'application et de traitements spécifiques. En effet, aucune approche proposée ne prend en considération les aspects d'auto-organisation possibles d'un système et plus particulièrement dans la conception des systèmes reconfigurables. Considérant les environnements, dans lesquels les architectures de calcul évoluent, de plus en plus « changeables » et non-déterministes et que chaque changement exige une réponse adéquate et efficace. Des solutions architecturales doivent être développées afin de permettre d'associer au sein d'une même architecture de traitement à la fois :

- la versatilité structurelle de la technologie microélectronique (reconfiguration dynamique des circuits FPGA) permettant d'assurer une adaptabilité structurelle des architectures de traitement tout en maintenant des performances de traitement élevées;

- l'introduction des concepts relatifs au principe d'auto-organisation permettant une réponse du système la plus appropriée à tous changements environnementaux du système à travers une auto-adaptabilité.

C'est dans ce contexte que se situent ces travaux de recherche. Les travaux menés et présentés dans ce manuscrit ont été initiés dans le cadre du Collège Doctoral Franco-Allemand intitulé « Système de Calcul Reconfigurable, Adaptable, Autonomique et Organique » (« Autonomische, Organische und Reconfigurable Rechensysteme ») débuté en octobre 2006 et en collaboration entre le groupe « Computer Engineering » dirigé par le Prof. Christophe BOBDA de l'Institut für Informatik (IFI)¹ de l'université de Potsdam, le laboratoire LIEN² de la faculté des sciences et techniques de Nancy 1 et le laboratoire LICM³ de l'université Paul Verlaine de Metz. L'objec-

<sup>&</sup>lt;sup>1</sup>Institut für Informatik - Universität Potsdam, http://www.cs.uni-potsdam.de

<sup>&</sup>lt;sup>2</sup>Laboratoire d'Instrumentation Électronique de Nancy, http://www.lien.uhp-nancy.fr

<sup>&</sup>lt;sup>3</sup>Laboratoire Interface Capteurs Microélectronique de Metz, http://www.licm.sciences.univ-metz.fr

tif principal de ces travaux de recherche est de développer une nouvelle approche architecturale pour la conception de systèmes auto-organisés à base de technologies reconfigurables.

### 3 Contribution

Le but de ce travaux de recherche est d'apporter des solutions architecturales innovantes basées principalement sur le principe d'auto-organisation et permettant la mise en œuvre d'une architecture embarquée auto-organisée adaptée à la technologie reconfigurable. Plus précisément, ces travaux de thèse consistent à développer une architecture auto-organisée de type reconfigurable MPSoC (Multi Processor System on Chip) à base de technologie reconfigurable FPGA. Pour ce faire, les caractéristiques principales du principe d'auto-organisation ont été identifiées et transposées dans le domaine de la conception de systèmes reconfigurables. Ainsi, un système reconfigurable auto-organisé a été défini et les principaux besoins pour sa réalisation ont été recensés.

La stratégie de recherche proposée dans ces travaux de thèse consiste à développer une approche architecturale mettant en œuvre les concepts d'auto-adaptativité, d'auto-organisation par l'exploitation de la reconfiguration dynamique (RD) des circuits FPGA tout en recherchant à satisfaire la notion d'Adéquation Algorithme - Architecture. L'objectif de ces travaux est d'élaborer le principe d'une auto-organisation (AO) matérielle en vue d'aboutir à des architectures de calcul embarqué capables de s'auto-restructurer dynamiquement, s'auto-gérer de manière autonome et sans contrôle externe tout en répondant à des contraintes multiples de conception ou de traitement (contrainte de temps ou puissance de calcul, flexibilité, tolérance aux fautes, etc). L'approche architecturale de calcul embarqué auto-organisée proposée repose à la fois sur une structure de communication reconfigurable de type NoC (Network on Chip) adaptée à la technologie FPGA et sur des structures originales de communications informationnelles contribuant à mettre en œuvre les principes d'auto-adaptation, d'auto-organisation. L'ensemble de ces points ont été validés non seulement au niveau de simulations mais également au niveau expérimental sur un exemple concret d'application de traitement d'images temps réel. Les travaux menés pendant cette thèse sont originaux en plusieurs points. D'abord, parce qu'ils portent sur la transposition matérielle des aspects du principe d'auto-organisation des systèmes. Ensuite, parce que les travaux effectués prennent en compte les spécificités de la technologie reconfigurable FPGA afin d'aboutir à un prototype opérationnel.

### 4 Plan du manuscrit

Le manuscrit de cette thèse est structuré de la manière suivante :

Dans **le premier chapitre** nous recensons de manière non-exhaustive la notion d'autoorganisation, d'émergence et les principales propriétés associées (*adaptabilité*, *autonomie*, *robustesse*, *flexibilité*, *anticipabilité*, *contrôle décentralisé*). Nous proposons une définition d'un système auto-organisé et / ou émergent. Nous présentons quelques mises en oeuvre pratiques de tels systèmes. Ensuite, nous montrons l'intérêt de l'utilisation de la reconfiguration dynamique des circuits *FPGA* pour la mise en œuvre matérielle de systèmes possédant de telles propriétés. Enfin, nous concluons ce chapitre d'introduction sur l'intérêt d'exploiter les technologies *FPGA* pour la conception de systèmes embarqués auto-organisés.

Dans **le deuxième chapitre** nous rappelons les principales caractéristiques de la reconfiguration dynamique à base de technologie *FPGA*. Ensuite, nous proposons une définition d'un système reconfigurable auto-organisé. Puis, une transposition des caractéristiques et des propriétés d'auto-organisation est menée dans le cadre d'une mise en œuvre dans un système reconfigurable à base de circuits *FPGA*. Enfin, nous concluons par un recensement des principaux besoins pour la conception de systèmes reconfigurables auto-organisés et nous montrons la nécessité d'élaborer d'une part de nouveaux concepts architecturaux basés sur des structures de communication adaptées à la technologie *FPGA*. D'autre part, de développer des mécanismes d'apprentissage au cours du fonctionnement de tels systèmes.

Le troisième chapitre présente l'approche architecturale adoptée permettant une solution matérielle de mise en œuvre des propriétés d'auto-organisation dans les systèmes sur puce reconfigurables (RSoC ou reconfigurable MPSoC). Dans un premier temps, un rappel des principaux types de répartition de contrôle généralement utilisés dans la conception des systèmes est présenté. Quelques exemples sont cités. Ensuite, nous proposons une approche architecturale caractérisée par la mise en œuvre du principe d'auto-organisation à travers le développement matériel de nouvelles structures de communications informationnelles internes, circulaires localement et globalement au système auto-organisé proposé (notion de flux et de descripteur). Ce concept original permet des échanges d'informations entre les modules constituant le système, sans un contrôle centralisé et tout en générant une « conscience » interne parmi l'ensemble des entités le constituant, dans le but de répondre à tout changement ou évolution du système. Ce concept est également détaillé à travers un exemple concret du fonctionnement auto-organisé du système proposé au cours d'une défaillance temporaire ou permanente d'entités le constituant, par changement ou substitution fonctionnelle de ses modes de fonctionnement.

Dans le **quatrième chapitre** nous présentons et détaillons la conception d'une structure adaptée de communication sur puce (*Network on Chip - NoC*) pour les systèmes reconfigurables auto-organisés à base de technologie *FPGA*. Après avoir rappelé les principales caractéristiques des réseaux sur puce et justifié les raisons pour lesquelles les *NoC* « classiques » actuels ne sont pas adaptés à des systèmes reconfigurables auto-organisés, nous proposons deux nouvelles architectures de routeur sur puce (*CuNoC* et *QNoC*) correspondant à une évolution

pour architecture *NoC* adaptée aux systèmes reconfigurables. Une analyse et une comparaison détaillées de leurs principaux avantages et inconvénients sont également présentées. Un algorithme de routage spécifiquement développé pour une architecture reconfigurable *NoC* associée à ces routeurs est également détaillé. Nous concluons ce chapitre en résumant quelques travaux en perspective à effectuer sur les *NoC* reconfigurables.

En vue de valider l'approche architecturale globale du système auto-organisé proposé et associée aux concepts, mécanismes et structures de communication sur puce adoptés (et présentés dans les chapitres précédents), le **cinquième et dernier chapitre** présente les résultats de l'exécution d'une auto-organisation de notre architecture dans le cas d'un traitement d'images temps réel défaillant au cours du temps tout en maintenant une *Adéquation Algorithme - Architecture*. Nous détaillons les démarches que nous avons effectuées pour appliquer les structures principales de notre approche architecturale. L'objectif principal de ce chapitre est une validation expérimentale de l'ensemble des aspects conceptuels abordés au cours de ces travaux de recherche dans le but de rendre un système capable de gérer de manière autonome et intelligente les éventuelles perturbations provenant de l'environnement dans lequel il évolue.

Enfin, une **conclusion générale** discute et dresse le bilan de ces travaux de recherche en présentant les apports des concepts architecturaux proposés et en dégageant des perspectives.

### Chapitre 1

# Les systèmes auto-organisés et / ou émergents

#### 1.1 Introduction

D'innombrables exemples de systèmes naturels montrant une organisation de « haut niveau » sont présents autour de nous : des oiseaux qui volent en escadrille, le développement de colonnies de bactéries, la variation périodique des populations dans un système « prédateur proie », le déplacement cohérent d'un banc de poisson, les fourmilières, etc.

La notion de ces comportements n'est pas spécifique au vivant, elle s'observe également dans certains systèmes chimiques alimentés en continu, à la formation des dunes, des rivages, des galaxies, des systèmes planétaires, des sociétés, etc. Au niveau microscopique, les éléments constituant ces systèmes obéissent à des règles spécifiques à première vue relativement simples. Au niveau macroscopique, leurs comportements globaux dépassent le simple ensemble de règles de leurs parties. En effet, les comportements de ces systèmes émergent d'un ensemble de comportements individuels et d'interactions entre les parties constitutives du système. C'est la raison pour laquelle tous ces systèmes donnent l'impression d'avoir des comportements spontanés, irrationnels, machinaux, d'avoir une structure décentralisée et d'être caractérisés par une organisation dissimulée. C'est pourquoi, on définit ces spécificités et particularités comme une « émergence » et / ou une « auto-organisation ». En effet, soit l'interaction des éléments du système est considérée comme une émergence en vue d'une adaptation définie comme une auto-organisation; soit l'interaction est une auto-organisation synonyme d'une émergence.

D'une manière générale et malgré la variété des caractérisations de ces systèmes, on remarque un ensemble d'attributs les spécifiant tels que : « organisation », « émergence », « adaptation », « dynamique », et ils sont souvent associés et précédés du préfixe « auto ». Cependant, on constate que les termes les plus souvent utilisés pour désigner le comportement global de ces

systèmes sont « l'auto-organisation » et « l'émergence ». Les principes et les propriétés fondamentales liés à ces deux notions ainsi que la distinction entre elles font l'objet de ce chapitre.

La suite de ce chapitre est organisée de la manière suivante. Dans une première partie nous recensons de façon non-exhaustive la notion d'auto-organisation, d'émergence et les propriétés associées. Nous proposons une définition d'un système auto-organisé et / ou émergent. Nous présentons quelques mises en œuvre pratiques de tels systèmes. Ensuite, nous montrons l'intérêt de l'utilisation d'une technologie reconfigurable de type *FPGA* pour la réalisation de tels systèmes.

#### 1.2 Auto-organisation

Le problème majeur parmi toutes les définitions que l'on rencontre dans la littérature est souvent la désignation d'un même terme en lui attribuant des propriétés parfois très différentes. Notre objectif n'est pas de donner une définition consistante de ce terme, mais plutôt d'analyser les contextes d'apparition de ce concept avec tous les attributs qui lui sont attachés. Ensuite, de proposer une réalisation matérielle d'un tel système en mettant en œuvre ces propriétés grâce aux technologies reconfigurables de type *FPGA* à travers l'exécution de procédés de reconfiguration dynamique que l'on trouve dans les systèmes reconfigurables [Tan01].

#### 1.2.1 Définitions courantes

Avant de présenter les définitions des systèmes possédant des propriétés d'auto-organisation les plus souvent rencontrées dans la littérature et d'assigner des définitions à ce principe dans le domaine des systèmes reconfigurables, nous rappelons les définitions des racines des mots suivants : « organiser », « organisation » et « auto ».

Le dictionnaire français Hachette [HAC] définit les termes « *organiser* », « *organisation* » et « *auto* » de la manière suivante :

#### organiser (verbe)

- 1. Mettre en place (les éléments d'un ensemble) en vue d'une fonction, d'un usage déterminés. Organiser un service.

- 2. Préparer, monter. Organiser un voyage, un spectacle. Régler, aménager. Organiser ses loisirs, son temps.

- 3. v. pron. Devenir organisé. Les secours s'organisent. Prendre ses dispositions pour agir efficacement.

#### organisation (nom féminin)

- 1. Manière dont un corps est organisé; structure. Organisation des reptiles, d'une cellule.

- 2. Action d'organiser. Voulez-vous vous charger de l'organisation de la fête?

- 3. Manière dont un ensemble quelconque est constitué, réglé. Organisation judiciaire.

- 4. Association, groupement.

auto- Élément, du gr. autos, « soi-même ».

D'après ces définitions, la notion d'« auto-organisation » d'un système pourrait désigner un phénomène de structuration réglementé des éléments constituant le système et de leurs associations selon une vision fonctionnelle, dont le but est de délivrer un « service attendu ».