# Contribution aux architectures adaptatives: Etude de l'efficacité énergétique dans le cas des applications à parallélisme de données

Xun Zhang

#### ▶ To cite this version:

Xun Zhang. Contribution aux architectures adaptatives: Etude de l'efficacité énergétique dans le cas des applications à parallélisme de données. Autre. Université Henri Poincaré - Nancy 1, 2009. Français. NNT: 2009NAN10106. tel-01748353

# HAL Id: tel-01748353 https://hal.univ-lorraine.fr/tel-01748353

Submitted on 29 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

#### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

U.F.R. Sciences et Techniques, Mathématiques, Informatiques, Automatique École Doctorale Informatique Automatique Electronique Electrotechnique Mathématiques Département de formation Doctorale Électronique Électrotechnique

# Contribution aux architectures adaptatives : étude de l'efficacité énergétique dans le cas des applications à parallélisme de données

# **THÈSE**

présentée et soutenue publiquement le 15/09/09

pour l'obtention du

## Doctorat de Nancy Université – Nancy 1

(spécialité Systèmes Électroniques)

par

#### Xun ZHANG

#### Composition du jury

Président : Olivier SENTIEYS Professeur, Université Rennes 1

Rapporteurs : El-Bay BOURENNANE Professeur, Université de Bourgogne

Lionel TORRES Professeur, Université Montpellier 2

Examinateurs: Serge WEBER Professeur, UHP (Directeur de thèse)

Hassan RABAH Maître de Conférences HDR, UHP (Co-directeur de thèse)

Yves BERVILLER Maître de Conférences, UHP

### Remerciement

Je remercie en tout premier lieu mes directeurs de thèse M. Serge WE-BER et M. Hassan RABAH, pour la confiance qu'ils m'ont témoignée tout au long de ces années de travail, leurs participations, leurs encouragements quotidiens et leurs précieux conseils au niveau scientifique.

J'adresse mes remerciements à **M. Oliver SENTIEYS**, professeur, ENS-SAT, Lannion, qui m'a fait l'honneur de présider le jury. Je voudrais exprimer ma gratitude à toutes les personnes qui m'ont fait l'honneur de participer à ce jury de thèse : **M. Lionel TORRES**, professeur à l'université de Montpellier 2 et **M. El-bay BOURENNANE**, professeur à l'Université de Bourgogne, pour l'attention qu'ils ont accordée à la lecture de ce mémoire de thèse et pour avoir bien voulu en être les rapporteurs.

Mes remerciements vont en particulier à **M. Yves BERVILLER**, Maître de conférences à Nancy Université qui lors de nombreuses discussions m'éclaira sur mon travail et eu la gentillesse de corriger mon manuscrit et de me faire part de ses commentaires.

Mes remerciements les plus chaleureux à tous les membres du laboratoire LIEN. Avec vous, la bonne humeur est indissociable du bon café, du thé et autres douceurs.

Mes remerciements vont également à ma famille, en particulier mes parents et ma soeur, cette thèse n'aurait jamais vu le jour sans leur soutien inconditionnel. Je ne saurais remercier assez **HUI** qui m'a encouragé tout au long de mes études et qui m'a apporté sont réconfort dans ma thèse et les moments difficiles.

# Table des matières

| Table d | les figu | res          |                                           | 1  |

|---------|----------|--------------|-------------------------------------------|----|

| Introdu | action g | générale     |                                           | 5  |

| Chapit  | re 1 Suj | pports po    | our les architectures adaptatives         | 9  |

| 1.1     | Introd   | $\frac{-}{}$ |                                           | 10 |

| 1.2     | Carac    | térisation   | et classification des SoCs adaptatifs     | 10 |

|         | 1.2.1    | Définiti     | ion générale                              | 10 |

|         | 1.2.2    | Niveau       | d'adaptation                              | 12 |

|         |          | 1.2.2.1      | Adaptation au niveau logiciel             | 12 |

|         |          | 1.2.2.2      | Adaptation au niveau matériel             | 13 |

| 1.3     | Adap     | tation par   | reconfiguration matérielle (RM)           | 14 |

|         | 1.3.1    | Reconfi      | iguration statique (RS)                   | 14 |

|         | 1.3.2    | Reconfig     | guration dynamique (RD)                   | 15 |

|         |          | 1.3.2.1      | Reconfiguration total dynamique (RTD)     | 16 |

|         |          | 1.3.2.2      | Reconfiguration partiel dynamique(RPD)    | 17 |

| 1.4     | Gestic   | n dynam      | ique des fréquences et d'alimentations    | 20 |

| 1.5     | Poten    | tiels des a  | architectures reconfigurables             | 23 |

|         | 1.5.1    | Archited     | cture: les tendances principales          | 23 |

|         |          | 1.5.1.1      | Architecture reconfigurable à grain fin   | 23 |

|         |          | 1.5.1.2      | Architecture reconfigurable à grain épais | 28 |

|         |          | 1.5.1.3      | Architecture reconfigurable hétérogène    | 31 |

| 1.6     | Concl    | usion        |                                           | 34 |

# Chapitre 2 Méthode et stratégie d'adaptation

| 2.1    | Introd   | luction                                                          | 38 |

|--------|----------|------------------------------------------------------------------|----|

| 2.2    | Problé   | ématique et applications cibles                                  | 38 |

| 2.3    |          | ance et énergie dans les applications périodiques                | 39 |

|        | 2.3.1    | Puissance dynamique                                              | 39 |

|        | 2.3.2    | Énergie consommée                                                | 40 |

| 2.4    | Effica   | cité énergétique                                                 | 42 |

| 2.5    | Modè     | le architectural                                                 | 45 |

|        | 2.5.1    | Unité de calcul Reconfigurable-RPM                               | 46 |

|        |          | 2.5.1.1 Placement et nombre de RPM                               | 47 |

|        | 2.5.2    | Contrôleur d'adaptation                                          | 52 |

|        |          | 2.5.2.1 Rôle du contrôleur                                       | 52 |

| 2.6    | Métho    | ode d'adaptation dynamique                                       | 54 |

|        | 2.6.1    | Fonction de transition                                           | 55 |

|        | 2.6.2    | Contexte d'applications spécifiques pour un système temps réel . | 55 |

|        | 2.6.3    | Prise en compte de l'efficacité énergétique                      | 58 |

|        | 2.6.4    | Étapes de l'adaptation et leur objectif                          | 60 |

|        |          | 2.6.4.1 Construction de la base de données du système            | 60 |

|        |          | 2.6.4.2 Choix et configuration de l'architecture optimale        | 62 |

|        | 2.6.5    | Méthode d'adaptation d'un traitement multi-tâches                | 66 |

|        | 2.6.6    | Résumé du fonctionnement du système d'adaptation                 | 66 |

| 2.7    | Concl    | usion                                                            | 68 |

| Chapit | re 3 Étu | ıde et validation expérimentale                                  |    |

|        |          |                                                                  |    |

| 3.1    | Introd   | luction                                                          | 72 |

| 3.2    | La pla   | ate-forme expérimentale                                          | 72 |

|        | 3.2.1    | Étude préliminaire                                               | 74 |

|        |          | 3.2.1.1 Contrainte de reconfiguration                            | 74 |

|        | 3.2.2    | Gestion dynamique de fréquence                                   | 76 |

| 3.3    | Appli    | cation jpge2000                                                  | 77 |

|        | 3.3.1    | Description de l'algorithme DWT                                  | 80 |

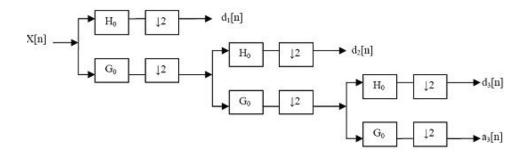

|        |          | 3.3.1.1 Étude de l'algorithme classique 2-D                      | 80 |

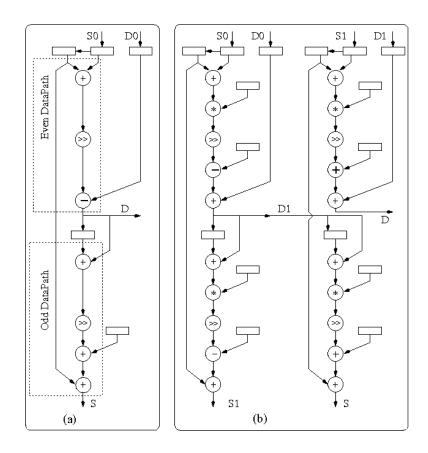

|        |          | 3.3.1.2 Exemple de DWT sans perte (5/3)                          | 82 |

|        |          | 3.3.1.3 Exemple de DWT avec perte (9/7)                     | 3 |

|--------|----------|-------------------------------------------------------------|---|

| 3.4    | Descr    | iption de l'architecture                                    | 4 |

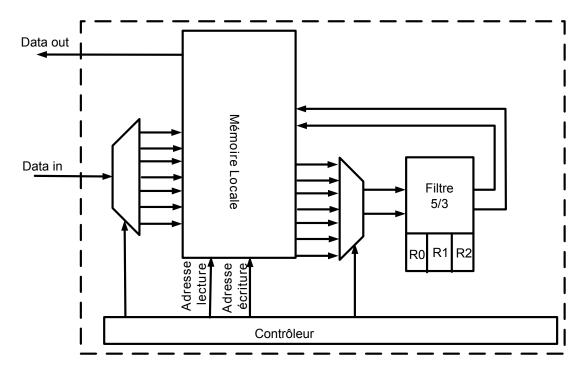

|        | 3.4.1    | Module de calcul                                            | 6 |

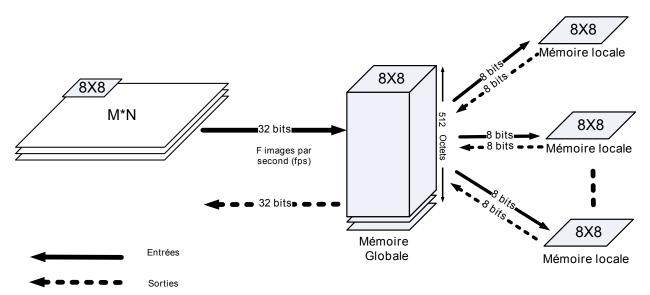

|        | 3.4.2    | Hiérarchie mémoire                                          | 7 |

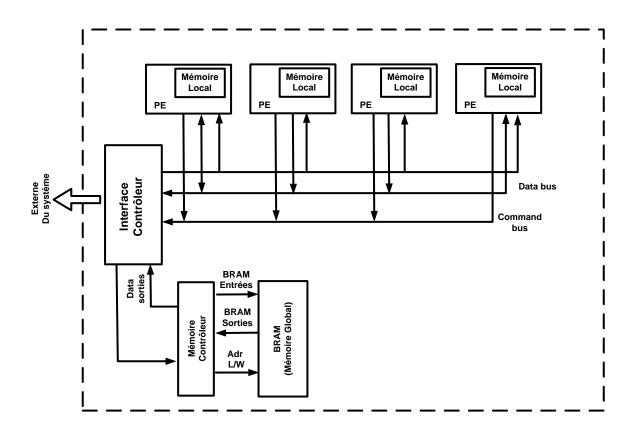

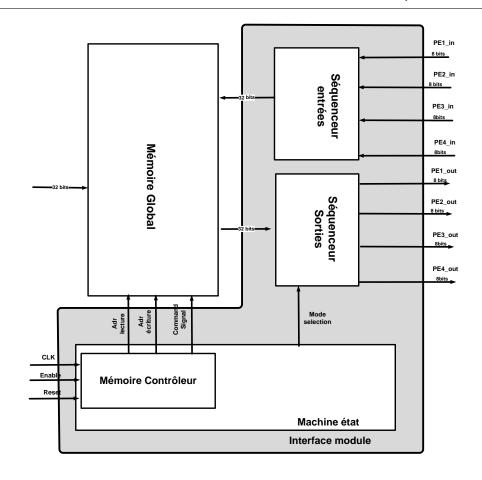

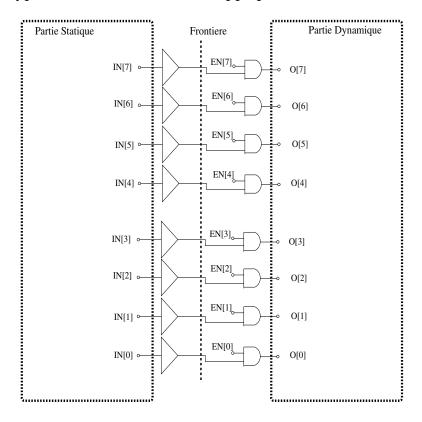

|        | 3.4.3    | Élement de communication                                    | 8 |

|        | 3.4.4    | Fonctionnement de l'architecture                            | 8 |

|        |          | 3.4.4.1 Période de fonctionnement                           | 8 |

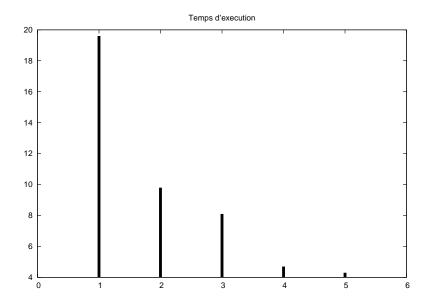

|        |          | 3.4.4.2 Temps d'exécution                                   | 0 |

|        |          | 3.4.4.2.1 Temps d'exécution maximum 9                       | 0 |

| 3.5    | Résul    | tats expérimentaux                                          | 1 |

|        | 3.5.1    | Distribution des ressources logiques                        | 1 |

|        | 3.5.2    | Placement de PE et de l'arbre de l'horloge                  | 2 |

|        | 3.5.3    | Variation du temps d'exécution réel et maximum 9            | 4 |

|        |          | 3.5.3.1 Temps d'exécution réel                              | 4 |

|        |          | 3.5.3.2 Contrainte de temps                                 | 4 |

|        |          | 3.5.3.2.1 Consommation de puissance 9                       | 5 |

|        |          | 3.5.3.3 Définition de l'efficacité énergétique 9            | 7 |

|        |          | 3.5.3.4 Calcul de l'efficacité énergétique                  | 8 |

|        |          | 3.5.3.5 Description du processus d'adaptation 9             | 9 |

| 3.6    | Concl    | usion                                                       | 3 |

|        |          |                                                             |   |

| Conclu | sion et  | Perspectives                                                |   |

|        |          |                                                             |   |

|        |          |                                                             |   |

| Annexe | es       |                                                             |   |

|        |          |                                                             |   |

| Annex  | e A Flot | t de conception de la reconfiguration partielle             |   |

|        |          | <u> </u>                                                    |   |

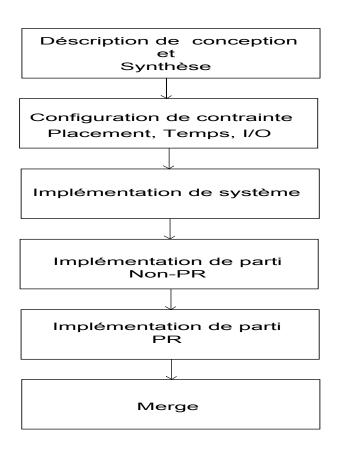

| A.1    | Descr    | iption du flot de conception utilisé                        |   |

|        | A.1.1    | Description et synthèse                                     |   |

|        | A.1.2    | Modification de contrainte du système                       |   |

|        | A.1.3    | Implémentation de la partie Statique                        |   |

|        | A.1.4    | Implémentation de la partie reconfigurable partiellement 11 |   |

|        | A.1.5    | Merge                                                       | 5 |

## Table des matières

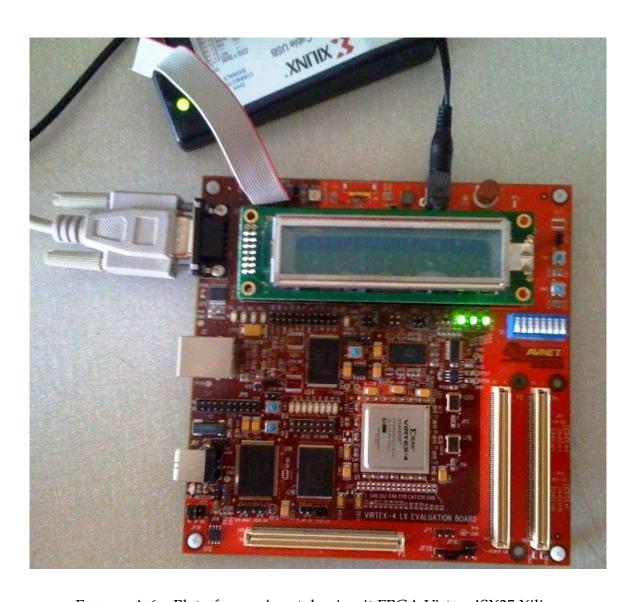

| A.2 Carte    | d'expérimentation -Virtex-4SX35 |

|--------------|---------------------------------|

| A.2.1        | MicroBlaze                      |

| A.2.2        | Fast Simplex Link - FSL         |

| A.2.3        | Xilinx matériel ICAP - HWICAP   |

| Annexe B Imp | lémentation de l'exemple IDWT   |

Bibliographie

# Table des figures

| 1.1  | Le système adaptatif et son environnement                             | 11 |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Reconfiguration dynamique totale                                      | 17 |

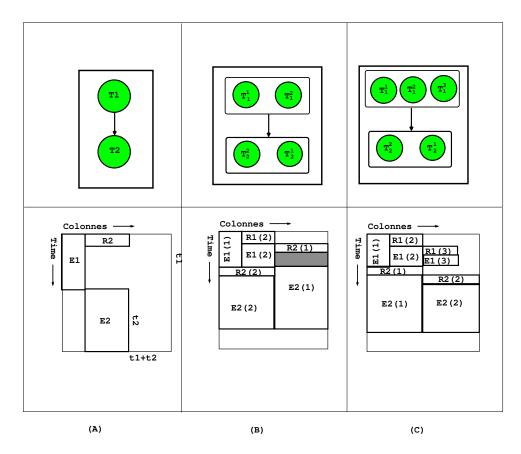

| 1.3  | Reconfiguration partiel dynamique                                     | 18 |

| 1.4  | La granularité du parallélisme pour maximiser la performance d'appli- |    |

|      | cation                                                                | 19 |

| 1.5  | La granularité du parallélisme pour maximiser la performance          | 20 |

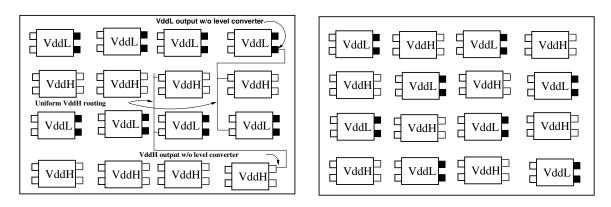

| 1.6  | Deux différents modèles layout pour un dual-Vdd FPGA [LLHC04]         | 22 |

| 1.7  | Exemple d'implémentation de DVS [LL05]                                | 23 |

| 1.8  | Blocs logique configurable(CLBs) Virtex-5 contenant deux slices       | 24 |

| 1.9  | Organisation interne de Virtex-4 de Xilinx                            | 26 |

| 1.10 | Exemple de l'architecture CASA [RLAR05]                               | 27 |

| 1.11 | Exemple d'une architecture reconfigurable sur Virtex-II de [Ua04]     | 28 |

| 1.12 | Architecture ADRES                                                    | 30 |

| 1.13 | Architecture DAP/DNA-2                                                | 31 |

| 1.14 | Architecture aSoC                                                     | 32 |

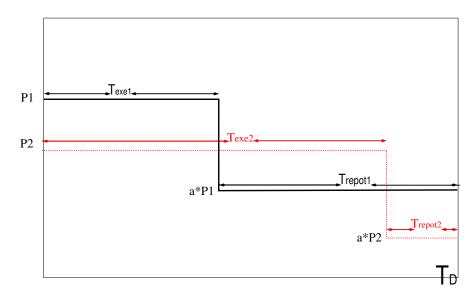

| 2.1  | Les puissances pendant le temps d'exécution et le temps de repos dans |    |

|      | une période fixée                                                     | 41 |

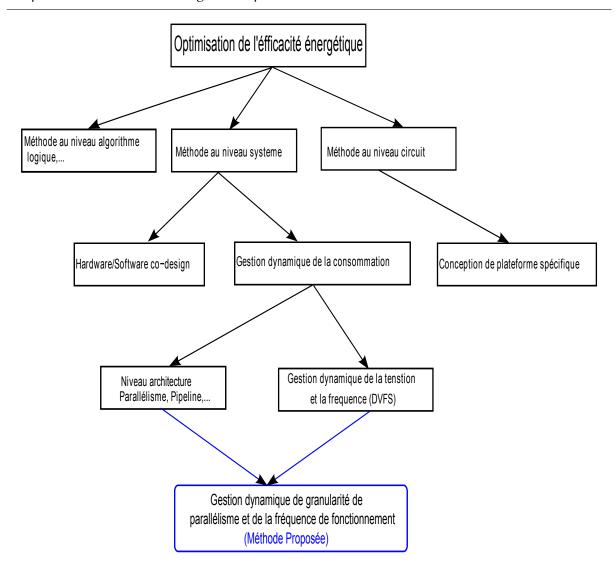

| 2.2  | Classifications des méthodes de l'optimisation de la consommation et  |    |

|      | solution proposée                                                     | 44 |

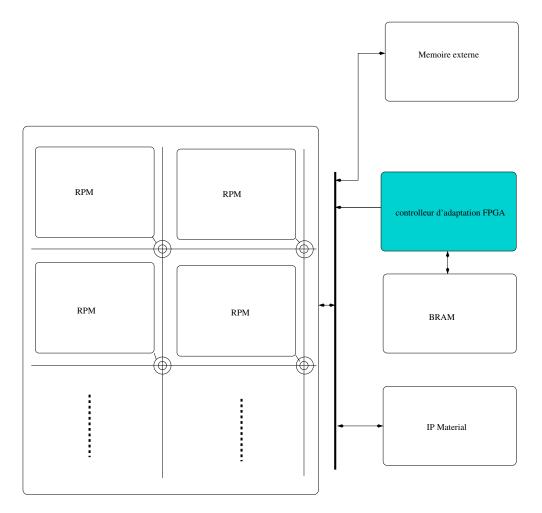

| 2.3  | Organisation de l'architecture du système adaptatif                   | 46 |

| 2.4  | Les temps d'exécution en fonction du nombre de modules fonctionnels   |    |

|      | pour la même fréquence de fonctionnement                              | 48 |

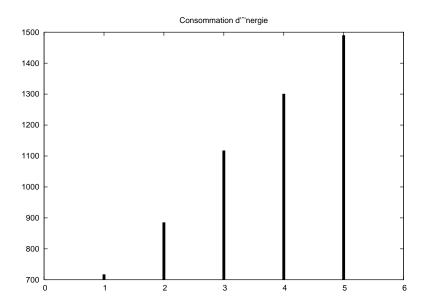

| 2.5  | Augmentation d'énergie en fonction de nombre de modules fonction-            |    |

|------|------------------------------------------------------------------------------|----|

|      | nels pour la même fréquence de fonctionnement                                | 49 |

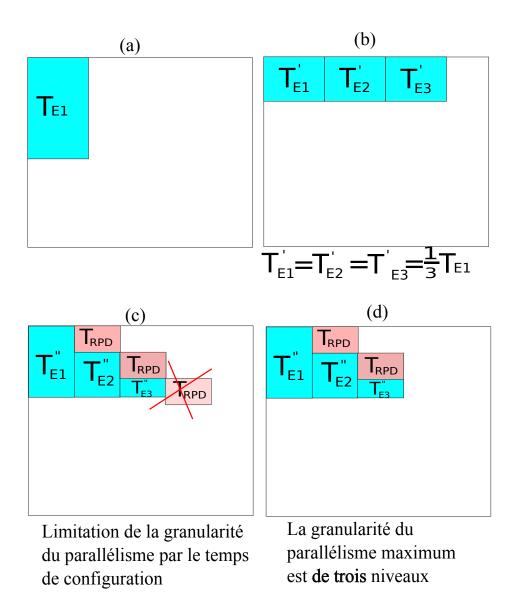

| 2.6  | Exemple de granularité de parallélisme et le temps de configuration          |    |

|      | partiel; (a) un module de calcul fonctionne; (b) trois modules de cal-       |    |

|      | cul fonctionnent en parallèle sans le temps de reconfiguration partiel;      |    |

|      | (c) la granularité est limitée par le temps de configuration partielle ; (d) |    |

|      | la granularité du parallélisme maximum sous condition du temps de            |    |

|      | configuration partielle                                                      | 51 |

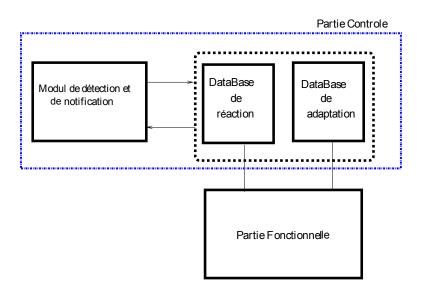

| 2.7  | Structure d'une partie contrôle du système d'auto-adaptation                 | 53 |

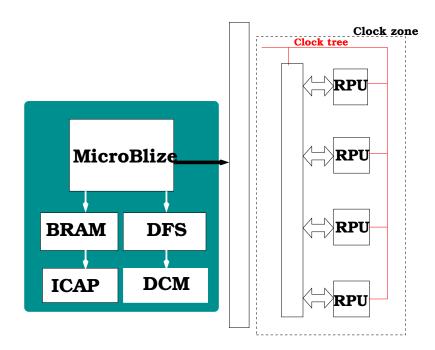

| 2.8  | Exemple d'un contrôleur en version MicroBlaze dans le circuit FPGA de        |    |

|      | Xilinx                                                                       | 54 |

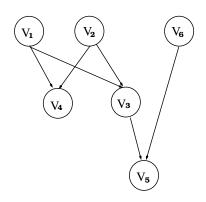

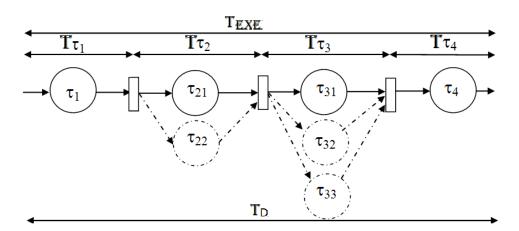

| 2.9  | Graphe de données d'une application sous contrainte de temps                 | 56 |

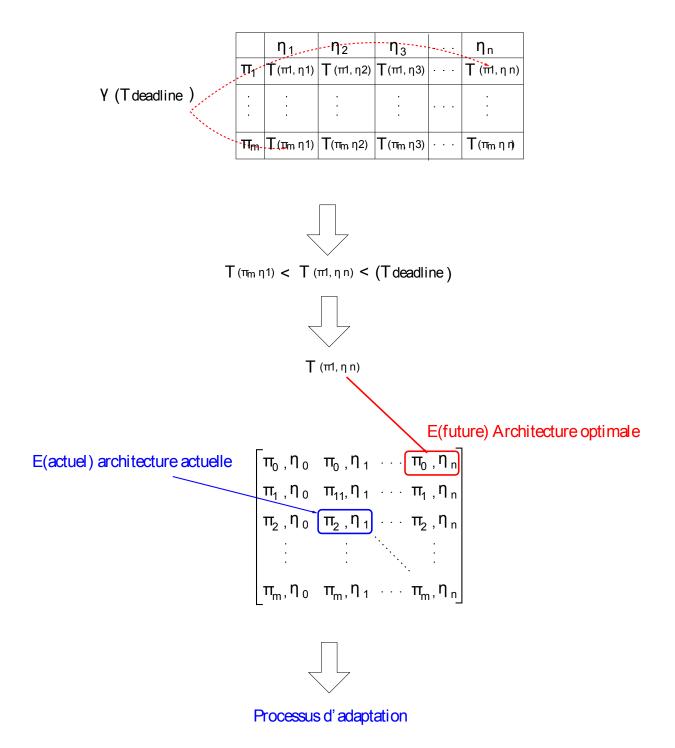

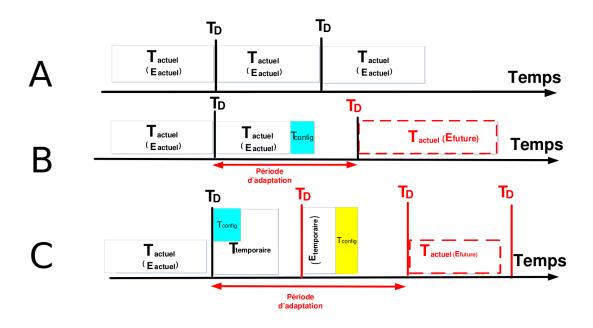

| 2.10 | Le processus de configuration d'architecture                                 | 59 |

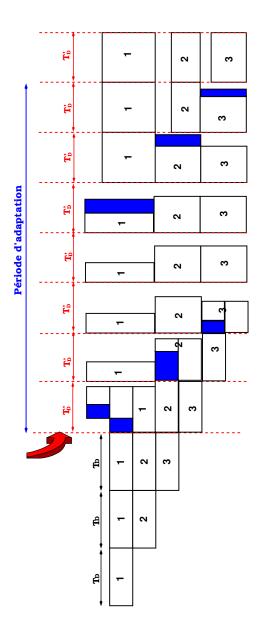

| 2.11 | Étapes de configuration d'architecture                                       | 61 |

| 2.12 | Les trois cas de relations entre la contrainte de temps et le temps d'exé-   |    |

|      | cution réel                                                                  | 63 |

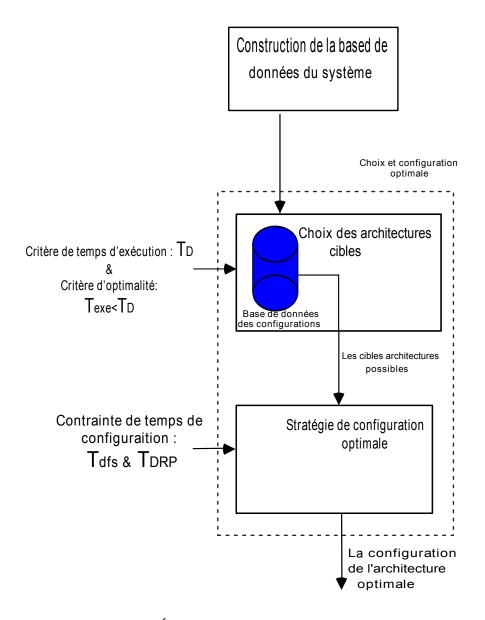

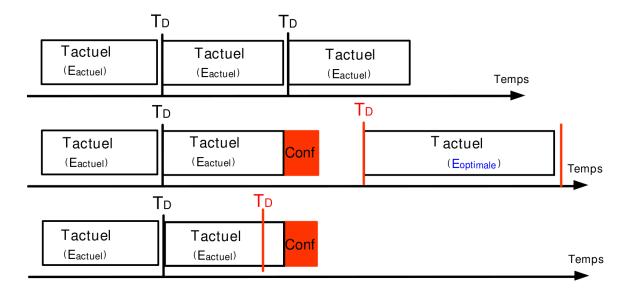

| 2.13 | Stratégies de la reconfiguration                                             | 65 |

| 2.14 | exemple d'un système d'adaptation d'une application multi-tâche en pi-       |    |

|      | peline                                                                       | 67 |

| 2.15 | le flot d'adaptation                                                         | 69 |

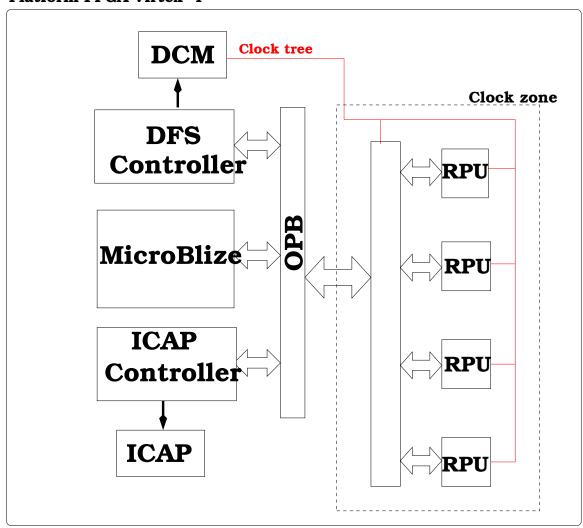

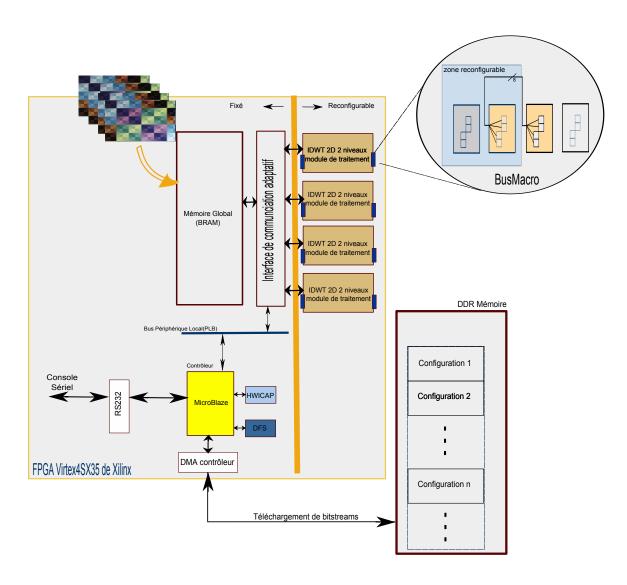

| 3.1  | La plat-forme auto-adaptative basée sur circuit FPGA de Xilinx               | 73 |

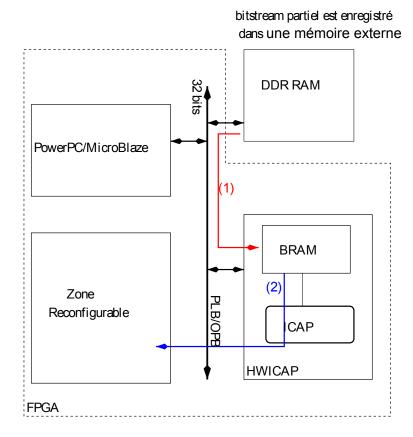

| 3.2  | Processus de reconfiguration partielle dynamique                             | 75 |

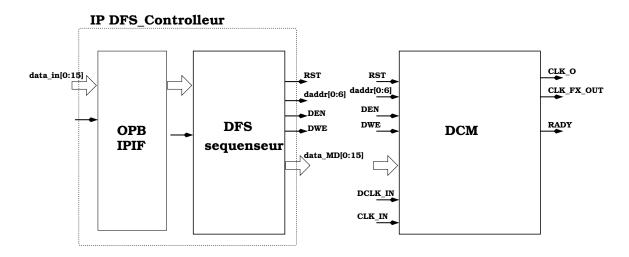

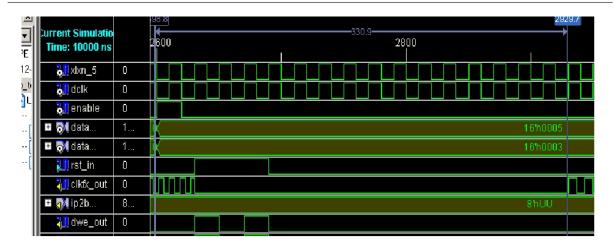

| 3.3  | Contrôleur de DFS                                                            | 77 |

| 3.4  | Contrôleur de DFS                                                            | 78 |

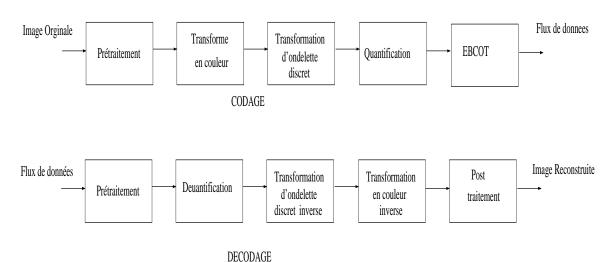

| 3.5  | Blocs constituant la chaîne de codage et décodage de JPEG2000                | 78 |

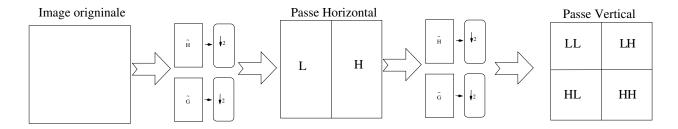

| 3.6  | Principe de la transformée en ondelettes discrètes                           | 80 |

| 3.7  | Transformée en 1D sur deux niveaux d'une image                               | 81 |

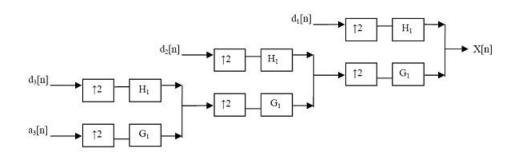

| 3.8  | Transforme inverse en 1D sur deux niveaux d'une image                        | 81 |

| 3.9  | IDWT 5/3 (a) et 9/7 DFG (b)                                                  | 83 |

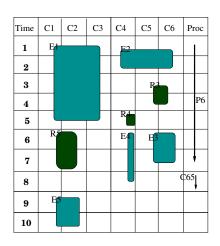

| 3.10 | Vue globale de l'architecture                                          | 85  |

|------|------------------------------------------------------------------------|-----|

| 3.11 | Architecture d'un PE                                                   | 86  |

| 3.12 | Interface de communication                                             | 89  |

| 3.13 | Distribution des ressources dans le système                            | 89  |

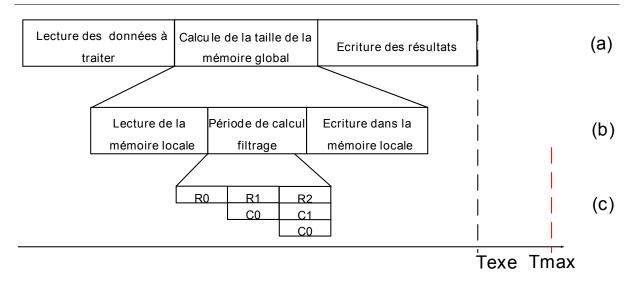

| 3.14 | Période de calcul du système                                           | 90  |

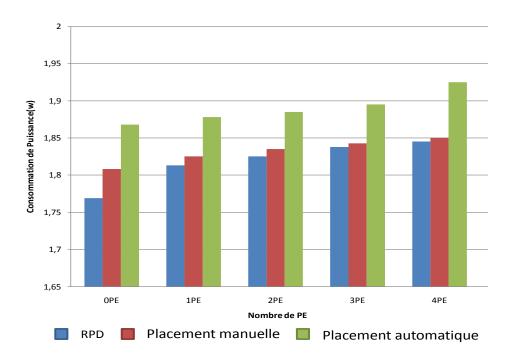

| 3.15 | Comparaison de la consommation de puissance en utilisant trois diffé-  |     |

|      | rentes méthodes de placement. Les placements de $RPD$ et Placement     |     |

|      | manuellement sont mêmes. $RPD$ active le nombre de PE par reconfi-     |     |

|      | guration partielle. Placement manuel active le nombre de PE par une    |     |

|      | simple interrupteur comme le cas Placement automatique                 | 93  |

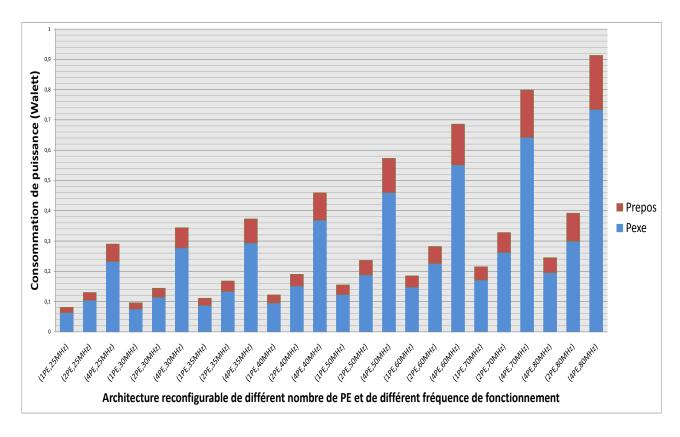

| 3.16 | Consommation de puissance en fonction du nombre de PE et des diffé-    |     |

|      | rentes fréquences de fonctionnement                                    | 96  |

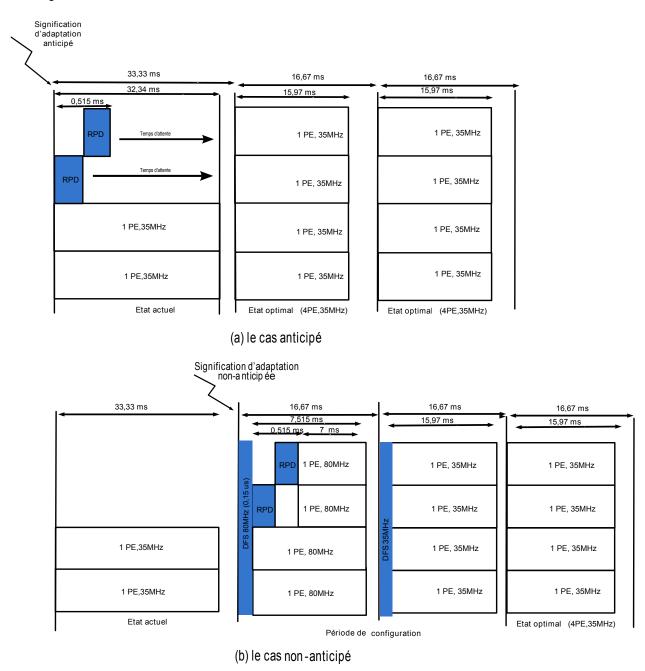

| 3.17 | Étapes de configuration anticipé(a) et non-anticipé(b)                 | 101 |

| A.1  | le flot de conception expérimenté                                      | 110 |

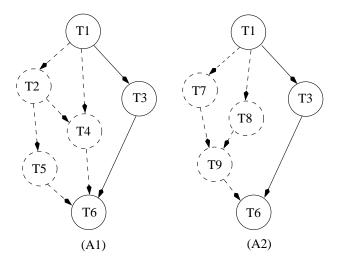

| A.2  | Description de l'application adaptative                                | 110 |

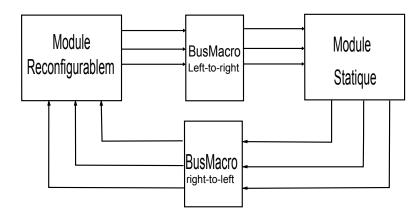

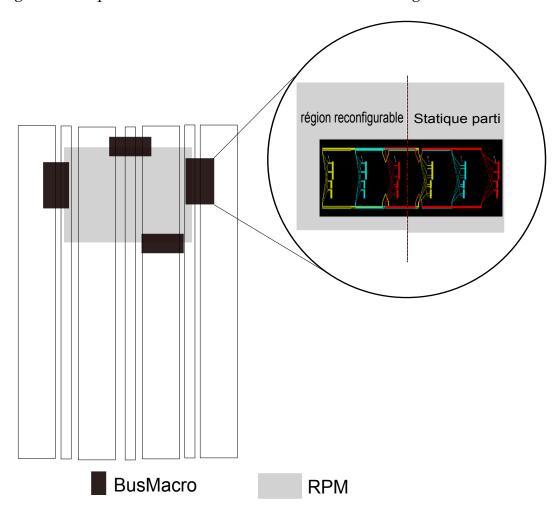

| A.3  | Interface pour la reconfiguration partielle : Slice Macro              | 112 |

| A.4  | Interface pour la reconfiguration partielle : Slice Macro              | 112 |

| A.5  | Placement de BusMacro                                                  | 113 |

| A.6  | Plate-forme $Avnet$ du circuit FPGA Virtex-4SX35 Xilinx                | 118 |

| B.1  | Vu global de l'architecture expérimentale                              | 128 |

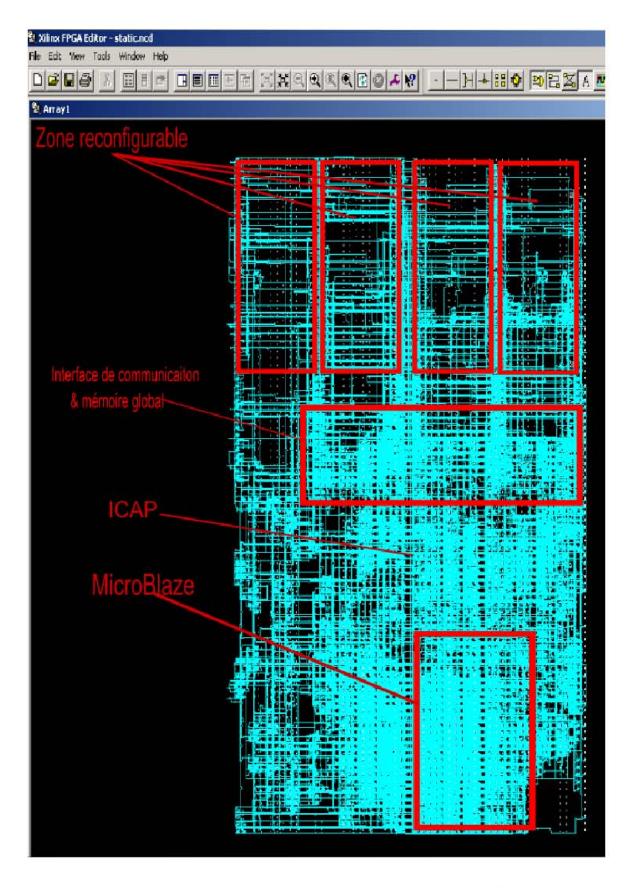

| B.2  | Placement de la partie statique du système avec la défintion des zones |     |

|      | reconfigurables                                                        | 129 |

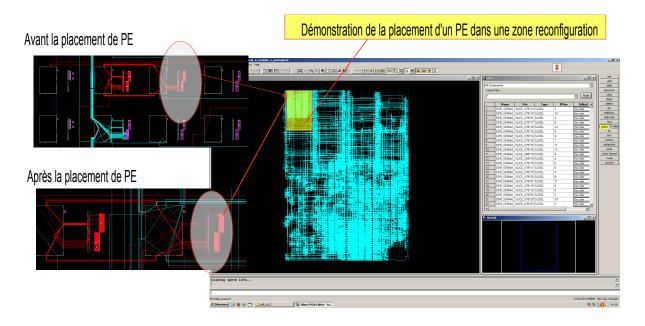

| B.3  | Implémentation de l'architecture de multi PE IDWT                      | 130 |

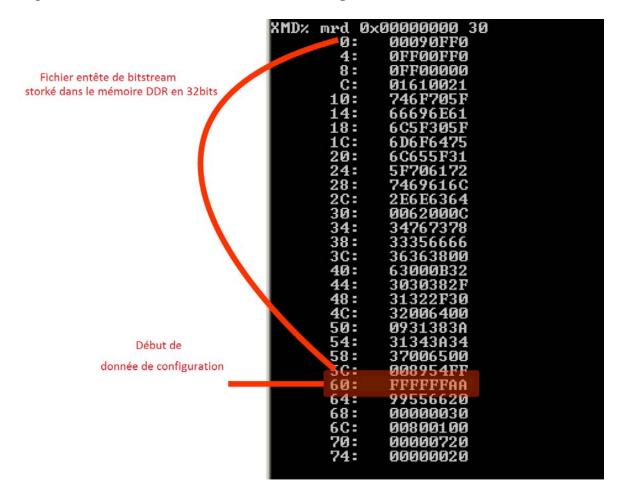

| B.4  | Exemple de stockage du bitstreams dans la mémoire DDR                  | 131 |

# Introduction générale

Le circuit configurable est apparu au début des années 80, beaucoup d'évolutions importantes ont eu lieu en ce qui concerne l'idée même de reconfigurer dynamiquement un composant. Une architecture reconfigurable est une architecture dont les ressources peuvent être redéfinies, complètement ou partiellement, pour réaliser un traitement donné. La reconfiguration peut être statique ou dynamique, dans le sens où l'architecture est reconfigurable au fil de l'exécution. Le travail s'inscrit en majeure partie dans le cadre de la reconfiguration partielle dynamique.

Aujourd'hui peu d'architectures reconfigurables sont effectivement réalisées sur silicium ce qui met les utilisateurs soucieux de cibler une architecture flexible et évolutive, face au manque de composants susceptibles de mettre en œuvre leurs applications.

La problématique qui motive ce travail de thèse peut se résumer ainsi : face aux multi-contraintes de l'application et variations dans le temps, est-il possible de développer une méthode permettant de choisir et d'adapter l'organisation d'une architecture respectant la contrainte temps réel tout en minimisant la consommation énergétique?

Les circuits reconfigurables actuels, notamment les permettent d'intégrer un grand nombre de ressources matérielles à granularité hétérogène allant de plusieurs microprocesseurs, d'opérateurs mathématiques jusqu'aux portes logiques élémentaires en très grand nombre [CH02, BBW+01]. Ceci amène à se poser la question sur la façon de concevoir les systèmes pour couvrir l'ensemble ou une partie des besoins (une meilleure utilisation des ressources, une puissance réduite, et une bonne vitesse d'exécution). Une possibilité est de partitionner une application en tâches matérielles et logicielles avant la synthèse, et de placer les tâches matérielles sur un accélérateur spécifique et les tâches logicielles sur un processeur à usage général. Certaines techniques de gestion [QSN07, LM05, NMB+03, MNC+03, RMVC05] sont proposées pour permettre aux tâches multiples d'être programmées de manière optimale.

Une autre possibilité est d'utiliser les SoPC. Dans ce cas de multiples noyaux fonctionnels et reconfigurables sont définis dans le système. Avec la technique de reconfiguration partielle et dynamique [Rab97], le dispositif reconfigurable permet de configurer une partie de logique de FPGA tandis que le système continue de fonctionner. En outre, comme mentionné ci-dessus, les plate-formes FPGAs actuelles pourraient également inclure le noyau de processeur et les accélérateurs spécifiques à l'application. Différentes architectures de ce type ont déjà été proposées aussi bien par des laboratoires universitaires que par des fabricants de SOC [UHGB04, AZB+07].

Pour ces deux possibilités, les solutions sont basées sur une topologie globale fixe et une architecture hétérogène associant un ensemble de GPP, DSP, et de processeurs spécifiques et d'architecture reconfigurables en grain fin ou gros grain. La contribution de ces dernières recherches est principalement focalisée sur les méthodes de gestions efficaces de ressources matérielles et logicielles. l'auto-adaptation demande non seulement une architecture hétérogène, mais aussi une évolution partielle et dynamique de sa topologie selon l'application exécutée et l'environnement de l'application.

L'objectif de ce travail de thèse est d'explorer la possibilité de maintenir des contraintes de temps d'exécution et de minimiser la consommation grâce à la reconfiguration dynamique et à la gestion dynamique de fréquence d'exécution dans un contexte d'applications où la quantité de donnée à traiter est variable.

#### Plan du mémoire

Le mémoire de thèse est organisé de la manière suivante : Le premier chapitre dresse un état de l'art des architectures adaptatives. Au niveau matériel, l'adaptation consiste en une reconfiguration partielle de l'architecture. La reconfiguration matérielle augmente la flexibilité de l'architecture en permettant l'implémentation d'un grand choix de fonctions. Dans ce chapitre, nous analysons les différentes possibilités d'adaptation des systèmes sur puce (SoC). Nous étudions ensuite la structure d'un SoC adaptatif. En mettant en évidence ses principaux éléments constitutifs. Nous complétons la caractérisation des SoCs adaptatifs par la présentation de différentes architectures et la comparaison des différentes structures.

Le deuxième chapitre détaille la méthodologie d'auto-configuration proposée. Il débute par une mise en évidence des différentes formes d'adaptations possibles décrites dans le chapitre précédent. Dans notre travail, nous nous concentrons sur deux méthodes : DRP et DFS. La reconfiguration partielle (DRP) nous permet de changer le niveau du parallélisme de tâche. La gestion dynamique de fréquence (DFS) de traitement permet d'obtenir la fréquence de traitement juste suffisante pour respecter la contrainte de temps. Le modèle d'un système adaptatif ainsi que ses éléments principaux sont présentés. Ensuite, nous montrons qu'il est possible d'améliorer le rendement des implantations à l'aide de notre méthode (adaptation du niveau de parallélisme et de la fréquence de traitement) tout en respectant la contrainte de temps de traitement.

Le troisième chapitre concerne la réalisation d'un prototype basé sur le modèle d'architecture décrit dans le chapitre précédent. La plate-forme expérimentale et le flot de conception utilisés seront d'abord présentés. Nous présentons ensuite les résultats issus de l'implémentation de fonctions clés de la compression d'images selon la norme JPEG2000 et analysons le comportement de notre architecture sur cette application. Les résultats expérimentaux sur le compromis efficacité énergétique et performance dans le cas de l'adaptation aux variations de quantité de données à traiter seront présentés et discutés.

La dernière partie de ce mémoire dresse un bilan du travail de thèse ainsi que les nombreuses perspectives ouvertes par ces travaux.

# **Chapitre 1**

# Supports pour les architectures adaptatives

| 1.1 | Introduction                                             |  |

|-----|----------------------------------------------------------|--|

| 1.2 | Caractérisation et classification des SoCs adaptatifs 10 |  |

|     | 1.2.1 Définition générale                                |  |

|     | 1.2.2 Niveau d'adaptation                                |  |

| 1.3 | Adaptation par reconfiguration matérielle (RM)           |  |

|     | 1.3.1 Reconfiguration statique (RS)                      |  |

|     | 1.3.2 Reconfiguration dynamique (RD)                     |  |

| 1.4 | Gestion dynamique des fréquences et d'alimentations 20   |  |

**Sommaire**

## 1.1 Introduction

Dans ce chapitre, nous allons présenter une étude consacrée aux supports pour les systèmes sur puce (SoC) adaptatifs. Un SoC adaptatif (ou auto-adaptatif) dispose (1) des mécanismes logiciels capables de reprogrammer les fonctions de traitement de son architecture (2) des mécanismes matériels capables de redéfinir complètement ou partiellement des caractéristiques de son architecture, de manière statique ou dynamique. Dans un premier temps, nous analyserons les différentes possibilités d'adaptation des SoC. Nous étudierons ensuite la structure d'un SoC adaptatif, en mettant en évidence ses principaux éléments constitutifs. Nous compléterons la caractérisation des SoCs adaptatifs par la présentation de différentes architectures et une comparaison de leurs différentes structures. Enfin, les méthodes d'adaptation seront étudiées.

# 1.2 Caractérisation et classification des SoCs adaptatifs

### 1.2.1 Définition générale

Nous considérons ici l'adaptation comme le processus de réutilisation et de continuité de service d'un système sur puce lorsque les besoins ou les conditions changent. L'adaptation permettra à la fois d'étendre l'utilisation d'un SoC pour d'autres applications et de maintenir et assurer la continuité de fonctionnement. L'adaptation est envisageable pendant la phase de conception (modèle adaptable) et pendant l'utilisation (système adaptable). Le modèle adaptable permet en particulier la réutilisation du même modèle auquel des modifications sont apportées pour réaliser des variétés ou une familles de SoC qui ne sont pas forcément adaptables. Nous appelons SoC adaptable le produit final qui peut être adapté aux besoins et aux conditions d'utilisation par l'utilisateur. On définira un SoC adaptatif comme le système qui est capable de détecter les modifications de son environnement et de s'adapter en conséquence.

On peut distinguer deux types d'adaptations. La première est l'adaptation spécifique où les adaptations particulières sont prévues et réalisées en ajoutant ou supprimant des modules ou bien en exploitant de manière intelligente les potentialités de cer-

taines fonctions. La seconde est l'adaptation générale qui doit en particulier répondre au problème de changement imprévisible de l'environnement. Cette adaptation est intéressante et convient aux systèmes plus complexes et rejoint la problématique d'autoorganisation qui n'est pas l'objet de cette thèse.

Le sujet de l'adaptation est largement étudié dans plusieurs disciplines aussi diverses que l'urbanisme avec les architectures adaptatives et l'informatique avec les logiciels adaptatifs. Dans toutes ces études, parmi les éléments clef de l'adaptabilité on trouve toujours la *modification*et la *modularité*. Ainsi, pour qu'un système soit plus adaptable, il faut autoriser et faciliter les modifications. Dans le cas de l'adaptation spécifique, un SoC doit être capable d'ajouter ou de supprimer des modules ou de modifier certains modules et d'assurer la communication entre eux en fonction des besoins et des conditions d'utilisation. Ces besoins et conditions doivent être introduits dans le flot de conception et utilisés comme contraintes qui doivent donc être prévues.

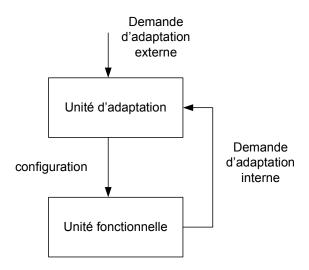

Les systèmes adaptatifs doivent réagir aux besoins de l'application mais également aux conditions de leurs fonctionnement internes ou externes. Ils doivent donc être capables de détecter l'état de l'environnement. La figure 1.1 représente un système adaptatif en relation avec son environnement. Le module d'adaptation surveille simultanément l'état du système et les conditions extérieures.

FIGURE 1.1 – Le système adaptatif et son environnement

L'action d'adaptation étant de modifier la structure du système, cette modification peut être effectuée au niveau logiciel ou matériel définissant ainsi les deux niveaux d'adaptation.

## 1.2.2 Niveau d'adaptation

#### 1.2.2.1 Adaptation au niveau logiciel

L'adaptation au niveau logiciel est réalisée par modification du programme s'exécutant sur un processeur en fonction de contraintes de l'application. L'objectif de la modification est d'optimiser le programme selon un certain nombre de critères dans un environnement où les paramètres de ces critères sont connus et fluctuent au cours de l'exécution du programme.

Plusieurs composants logiciels prouvent être assemblés pour une application. Ces composants logiciels permettent de définir des tâches plus ou moins complexes. Un programme peut être modifié par l'ajout, la suppression ou la modification d'une ou plusieurs tâches pour s'adapter à un nouveau service ou à un nouvel environnement.

Le travail [MLw98] propose une méthodologie pour la construction de programmes capables de s'adapter au changement de contraintes de l'application. Cette méthodologie est basée sur le choix des conceptions d'architecture de l'application prédéfinies. Un contrôleur est souvent installé dans le système et différents programmes prouvent être programmés dans le processeur. Dans les travaux [KBW03, BFY+02, NB02] un modèle à composants où chaque composant est constitué d'une partie contrôle et d'une partie fonctionnelle est proposé. La partie contrôle gère le cycle de vie du composant logiciel (démarrer, verrouiller, mis à jour, etc.). D'autres approches traitent l'aspect réutilisation des composants logiciels. Ces composants logiciels sont programmés dynamiquement par la partie contrôle. Évidemment, la reprogrammation est plus flexible que la modification d'architecture matérielle. Cependant, la solution logicielle est moins performante en terme de traitement et de consommation par rapport à la solution matérielle basée sur les ASIC et FPGA.

#### 1.2.2.2 Adaptation au niveau matériel

L'adaptation au niveau matériel est possible grâce aux architectures reconfigurables qui offrent la flexibilité des architectures programmables tels les processeurs à usage général et les performances des circuits ASICs [Har06]. Le concept de reconfiguration a largement été étudié depuis plusieurs années et reste encore un domaine de recherche actif. Plusieurs aspects de la reconfiguration ont été abordés et plusieurs architectures ont été proposées. Toutes ces architectures sont basées sur l'utilisation de blocs de calcul et d'éléments de communications reconfigurables. Les principales différences entre les architectures existantes résident dans les granularités des blocs de calcul qui peuvent être fin, épais ou hétérogènes aussi bien au niveau éléments de calcul que de communication [DeH96, Bob05].

Dans les architectures à grain fin (FPGA classique), la reconfiguration se fait au niveau bit permettant de réaliser des opérations de traitement ou de contrôle dédiées. Cependant, elles restent inefficaces dans le cas de certaines applications et posent le problème de la taille de configuration qui rend la reconfiguration dynamique complexe. Dans les architectures à grains épais, les interconnexions et les opérateurs sont configurables, mais travaillent au niveau arithmétique. Ceci a pour effet d'améliorer les performances sur les traitements arithmétiques, au détriment des optimisations au niveau bit. L'avantage des architectures à gros grain est de réduire la taille des configurations permettant d'envisager la reconfiguration dynamique de manière efficace.

Les FPGAs actuels en revanche offrent une alternative intéressante. En effet, ils intègrent des ressources matérielles allant d'une simple LUT, permettant de réaliser des fonctions au niveau bit, jusqu'à quelques microprocesseurs en dur en passant par des opérateurs plus ou moins complexes tels que les additionneurs, les fonctions multiplication accumulation, etc. Par ailleurs, ces circuits sont conçus et organisés sous forme de régions dont ont peut contrôler la fréquence et la tension d'alimentation et offrent également des possibilités de reconfiguration partielle. Il est ainsi possible de modifier et d'agir de manière dynamique et partielle sur les paramètres tension et fréquence en plus de la logique et des interconnexions.

L'idée de base de la reconfiguration dynamique est d'exécuter un ensemble de tâches matérielles sur un ensemble de surfaces logiques. Le nombre de tâches matérielles doit nécessairement être supérieur au nombre de surfaces logiques. Dans cette optique, la reconfiguration dynamique est vue comme un processus d'optimisation de surface. Les tâches matérielles sont alors obtenues par un découpage de l'application sous forme de partitions temporelles qui doivent être exécutées séquentiellement [KVGO99, TBWB03]. Les surfaces sur lesquelles doivent s'exécuter ces partitions sont le résultat du découpage spatial du circuit reconfigurable. Le processus de reconfiguration dynamique est aussi un processus d'allocation spatial et temporel des tâches d'une application. Cet aspect de la reconfiguration dynamique a largement été exploré depuis plusieurs années et reste encore un sujet assez ouvert. Parmi les problématiques abordées dans ce cas, il y a les aspects méthodes et outils pour le partitionnement spatial et temporel, la défragmentation, l'ordonnancement et exécutifs temps réel [RMVC05] [TSMM06]. L'architecture reconfigurable est une opportunité pour la réalisation d'un système adaptatif. Au niveau matériel, l'adaptabilité du système est obtenue par la configuration du circuit.

# 1.3 Adaptation par reconfiguration matérielle (RM)

Nous considérons qu'une application peut être constituée par un certain nombre de tâches. Chaque tâche peut représenter une opération ou un ensemble d'opérations de l'application. La reconfiguration matérielle (RM) nous offre une solution d'adaptation via la modification de la structure du système. La stratégie d'adaptation est le remplacement d'une application complète par une autre , ou le changement d'une partie de l'application pour répondre à des besoins de l'application.

## 1.3.1 Reconfiguration statique (RS)

La reconfiguration statique(RS) est l'approche la plus simple et la plus commune de la RM pour implémenter une application avec de la logique programmable. La RS concerne le changement de la fonctionnalité d'un ou de plusieurs composants d'un système indépendant de l'exécution d'une application. C'est-à-dire, le contenue de configuration reste statique pendant toute la vie de l'application.

La RS est similaire à l'utilisation de l'ASIC pour l'accélération d'applications. D'un point de vue application, il n'y a pas de grandes différences dans l'utilisation d'un FPGA ou d'un ASIC. Au niveau du coût système, le FPGA présente un grand avantage par rapport à l'ASIC. Pour une même surface de silicium, le FPGA peut être réutilisé plusieurs fois pour des applications différentes, ce qui n'est pas le cas pour un ASIC.

Le trait distinctif de la configuration statique est qu'elle consiste en un seul système. Avant de commencer une opération d'une fonction, les ressources reconfigurables sont chargées avec leurs configurations respectives. Une fois l'opération débutée, les ressources reconfigurables resteront dans cette configuration pendant toute l'opération de l'application. Ainsi, les ressources matérielles restent statiques pendant toute la durée de vie de la conception. La RS ne peut pas répondre aux besoins dans le domaine des systèmes adaptatifs. Concrètement, la RS s'emploie pour l'initialisation du prototype du système.

# 1.3.2 Reconfiguration dynamique (RD)

Ce mode de reconfiguration est basé sur la RS. Il offre la possibilité de changer de fonctionnalité pendant l'exécution d'une application pour reconfigurer le système en exécution. L'avantage de la RD a été plusieurs fois démontré [MB98, SD99, DLRN00]. Les caractéristiques principales de la RD sont : flexibilité, performance et coût par rapport à la RS.

*Flexibilité*: La RD supporte la reconfiguration au cours d'exécution. Ainsi, la durée de vie d'une configuration n'est plus celle de l'application entière. Une application peut être coupée en plusieurs parties qui seront exécutées avec un ordre de configuration. Donc la RD est plus adaptée à la conception de systèmes adaptatifs que la RS.

Performance : Par rapport la RS, la RD propose plus de moyens pour optimiser les performances de calcul grâce à plusieurs versions de fonctionnalité d'un compo-

sant qui peut être changé au cours d'exécution. Elle peut optimiser la performance ou ajuster la fonction du système en utilisant le circuit le plus optimisé qui est chargé ou déchargé dynamiquement pendant le traitement du système. Cela est la principale différence par rapport à la RS.

Coût: l'intérêt majeur de la RD est la possibilité d'une reconfiguration illimitée d'implémentation de plusieurs fonctions différentes avec le même matériel. L'un des principaux inconvénients des FPGAs par rapport aux ASICs est qu'ils sont moins denses en nombres de portes utiles et ont des fréquences de fonctionnement réduites. La RD est donc un moyen d'améliorer certains de ces handicaps en reconfigurant le circuit lorsque celui-ci a montré un accroissement des capacités de fonctionnement [BDHM05]. En utilisant la RD, une petite surface de logique programmable peut supporter une grande application. Le coût de circuit est donc réduit grâce à l'utilisation de la RD. Il y a deux aspects de la RD: la reconfiguration totale dynamique(RTD) et la reconfiguration partielle dynamique(RPD).

#### 1.3.2.1 Reconfiguration total dynamique (RTD)

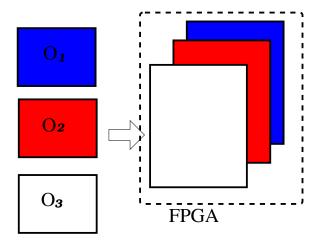

Dans ce type de reconfiguration, la totalité du contenu de la mémoire de reconfiguration du FPGA est remplacée par de nouvelles données de configuration. Ici, le terme "total" signifie la taille du FPGA. La figure 1.2 illustre ce mode de reconfiguration. Nous considérons un traitement constitué de trois segments d'un ou d'un groupe d'opérateur  $O_1$ ,  $O_2$  et  $O_3$ . La reconfiguration totale dynamique consiste en l'implémentation de ces trois opérateurs suivant leurs dépendances les uns par rapport aux autres en reconfigurant entièrement le système à chaque nouvelle étape.

L'avantage de la RTD est de supporter une grande flexibilité par rapport à la reconfiguration statique. Cependant, cette méthode est toujours supposée comme étant une reconfiguration entière du FPGA. Le seul problème principal pour l'utilisation de la RTD est tout d'abord d'arriver à un équilibre entre le partitionnement temporel de l'algorithme et la surface de FPGA.

Actuellement, l'évolution technologique des FPGAs permet d'implémenter de plus en plus d'applications dans un même circuit et ceux-ci peuvent supporter la reconfigu-

FIGURE 1.2 – Reconfiguration dynamique totale

ration partielle au cours d'exécution. Le problème de la taille des FPGAs est de moins en moins contraignant.

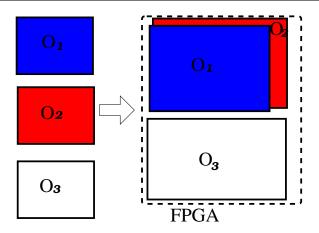

#### 1.3.2.2 Reconfiguration partiel dynamique(RPD)

Comme nous l'avons indiqué précédemment, l'inconvénient de la RTD est la nécessité de trouver un équilibre entre la taille des partitions. S'il n'est pas possible d'uniformiser la taille des partitions de l'application, l'utilisation des ressources du FPGA est inefficace, ce qui est une problématique. Pour résoudre cet inconvénient, il existe une technique, appelée reconfiguration partielle dynamique (RPD). La RPD supporte une approche de reconfiguration plus flexible que celle de la RTD. Elle peut reconfigurer une partie du matériel sans l'interruption des fonctions des autres parties. La figure 1.3illustre ce mode de reconfiguration. Précédemment, nous avons considéré un traitement constitué de trois opérateurs  $O_1, O_2$  et  $O_3$ . La reconfiguration partielle dynamique consiste à implémenter ces trois opérateurs suivant un ordre d'ordonnancement.

Par rapport à la RTD, la RPD ne consomme pas toute la surface du FPGA et permet de gérer efficacement cette surface. De plus, c'est une bonne alternative pour les algorithmes qui ne peuvent pas être partitionnés à des segments temporels liés avec la taille de la plate-forme entière. Parce que nous n'avons plus besoins de partitionner une ap-

FIGURE 1.3 – Reconfiguration partiel dynamique

plication en segments temporels en liant absolument la taille de la plate-forme entière. Nous pouvons donc nous concentrer sur l'ordonnancement des tâches reconfigurables pour avoir l'efficacité de l'implantation. De plus, l'optimisation de la contrainte de reconfiguration ( le temps de reconfiguration, l'allocation de l'application sur la puce) avec des méthodes de RPD est plus efficace que RTD grâce à certaines méthodes de RPD (masquant le temps de reconfiguration, l'ordonnancement de tâche, etc.). La RPD permet d'optimiser l'équilibre de performance et de consommation du système plus facilement. La RPD est utilisée pour implanter des tâches d'application sur la base de l'architecture FPGA SRAM. Plusieurs travaux de recherches ont exploité cet avantage dans la conception de système reconfigurables afin d'obtenir une bonne réutilisabilité [BBD05, SB06, BBD06, SEJN06, JPGCP04, BFY+02, HG07, AKM06].

Banerjee et al. [BBD05] présente une approche qui sélectionne la granularité du parallélisme de données pour maximiser les performances d'une application s'exécutant dans une architecture RPD. Cette approche choisit entre le niveau de parallélisme et les contraintes de temps de chaque niveau. Comme dans l'exemple qui est illustré dans la figure 1.4, trois granularités différentes se présentent pour différents niveaux de parallélisme, et aussi différents temps d'exécution. La figure 1.4-a est une chaîne simple avec deux tâches. Supposons que nous ayons à notre disposition les ressources suffisantes afin d'exécuter simultanément trois copies de la même tâche  $T_1$  ou 2 copies de la tâche  $T_2$ , (1.4-b) et (1.4-c) montrent des configurations possibles du graphe de tâches

après cette transformation.

FIGURE 1.4 – La granularité du parallélisme pour maximiser la performance d'application

Cependant, la transformation est sur l'architecture RPD où chaque copie de tâche ajoute une contrainte de reconfiguration significative. Donc, la transformation a besoin d'être guidée par une sélection de la granularité de parallélisme correcte. Mais, cette méthode n'a pas considéré la réutilisabilité de tâches.

Singhal et al. [SB06] mentionne le sujet de la réutilisation de composant. L'objectif est d'explorer le chevauchement potentiel entre deux tâches données avec une série de composants communs afin de réduire la latence de reconfiguration dynamique. Mais l'ordre de dépendance ou d'indépendance de tâches n'est pas considéré si la zone reconfigurable a besoin de mettre en place une nouvelle tâche.

Banerjee et al. [BBD06] a proposé une approche qui considère le problème de partitionnement matériel/logiciel au niveau tâche. Dans cette approche, toutes les tâches

ont deux versions, matérielle et logicielle. L'auteur propose une solution d'ordonnancement au cours d'exécution pour avoir le plus de performances. Comme indiqué sur la figure 1.5, une application est représentée par un graphe de tâches 1.5-a. Les temps d'exécution de chaque tâche pour les deux différentes versions et la surface occupée sur puce sont mesurés (figure 1.5-b). En utilisant ces paramètres, la solution optimisée de placement de tâche peut être trouvée (figure 1.5-c).

| Task | HW   | SW   | HW   |

|------|------|------|------|

| Lusk | Time | Time | Area |

| 1    | 5    | 23   | 3    |

| 2    | 2    | 9    | 3    |

| 3    | 2    | 11   | 2    |

| 4    | 3    | 14   | 1    |

| 5    | 2    | 10   | 2    |

| 6    | 3    | 7    | 4    |

FIGURE 1.5 – La granularité du parallélisme pour maximiser la performance

# 1.4 Gestion dynamique des fréquences et d'alimentations

La modification dynamique des fréquences de fonctionnement et des tensions d'alimentation permet d'obtenir un équilibre efficace entre performance et consommation du système. La gestion dynamique des fréquences et alimentations (Dynamic Frequency and Voltage Scaling(DFVS)) correspond à l'association de la gestion des fréquences (DFS¹) et gestion dynamique d'alimentation (DVS²). C'est une approche utilisée dans les ASIC ou dans un système basé sur le processeur pour ajuster la consommation d'énergie en temps réel. Les travaux [PBB98,TTR00,LLHC04,SN05,TBB98,TTR00] ont traité la configuration de la fréquence d'exécution et l'alimentation pour réduire la consommation d'énergie. Cependant sur les FPGAs, cette méthode n'est pas aussi fa-

<sup>1.</sup> Dynamic Frequency Scaling

<sup>2.</sup> Dynamic Voltage Scaling

cile à utiliser en raison de la structure spéciale du réseau interne de l'horloge sur FPGA et surtout la méthode DVS est très limitée sur FPGA. Actuellement, des fabricants de FPGA telle que xilinx proposent des cartes évaluation pour support DVS en utilisant un composant externe FPGA pour ajuster la tension de FPGAs<sup>3</sup>. Il existe également des recherches académiques, qui s'intéressent à cette problématique [LLHC04, LL05, PHBB07].

Gestion dynamique de fréquence La fréquence de fonctionnement influence directement la vitesse de calcul du circuit. Beaucoup de méthodes d'optimisations reposent sur le changement dynamique de la fréquence de fonctionnement comme les méthodes DFS(*Dynamique Fréquency Scaling*). La gestion dynamique de fréquence (DFS) est déjà connue dans les microprocesseurs et ASIC [DPF+00]. Elle est largement utilisée pour optimiser de la consommation d'énergie et les performances de calcul [DPF+00,SN05].

Gestion dynamique d'alimentation L'adaptation dynamique de la tension d'alimentation, appelée aussi : gestion dynamique d'alimentation  $^4$ , permet à un processeur de modifier dynamiquement sa tension d'alimentation et apporte un gain très significatif de la consommation. Beaucoup de méthodes d'optimisation [UH95, TBB98] reposent sur le changement dynamique de la tension d'alimentation  $V_{dd}$  pendant le fonctionnement du système. Cela suppose que le processeur soit capable d'ajuster à la demande sa tension et sa fréquence, et donc sa vitesse de traitement et sa consommation. Dans la littérature, il y a beaucoup de travail sur la gestion dynamique d'alimentation (DVS) [TBB98, BB95, KST01]. Nous donnons ci-après quelques exemple d'utilisation DVFS.

#### **lpARM**

Ce processeur [PBB98, TTR00], est une version de Berkekey de l'ARM8 conçu en technologie CMOS 0.6 *um*. Ses performances sont estimées à 6Mips à 5MHz-1.2v et 85Mips à 80MHz-3.8v. Lorsqu'il est en mode "IDLE"(en veille), le lpARM consomme 0.8mW et prend un cycle pour se réveiller. En ajustant la tension d'alimentation, le

<sup>3.</sup> info sur site: www.xilinx.com

<sup>4.</sup> Dynamic Voltage Scaling

système permet, non seulement fonctionner dans un état performante (80MHz-3.8v), mais aussi économiser la puissance consommé pendant le temps veille (5MHz-1.2v).

#### FPGA à multi-tension

Un autre exemple basé sur l'architecture FPGA est proposé dans [LLHC04]. Les multiples tensions ( $V_{dd}$ ) ou tensions de seuil( $V_t$ ) peuvent aussi améliorer l'efficacité énergétique. La réduction de  $V_{dd}$  limite la consommation de puissance dynamique, alors que l'augmentation de  $V_t$  limite la consommation de puissance statique. Cette architecture avec  $dual - V_{dd}$  et  $dual_V t$  obtient 13,6% et 14% de réduction de la puissance totale en moyenne pour les circuits combinatoires et séquentiels, respectivement [LLHC04]. Un exemple de sa structure est illustré dans la figure 1.6. L'avantage de cette architecture est d'optimiser la performance et l'efficacité d'énergie sur FPGA avec la technique multitension. La technique  $muti\ V_{dd}/multi\ Vt$  ont été employées sur ASIC [UH95,CSS01]. Cette architecture FPGA à multi-tension n'existe pas encore dans les plate-formes FPGA commerciales à cause de la limite des outils CAO et des structures de FPGAs.

FIGURE 1.6 – Deux différents modèles layout pour un dual-Vdd FPGA [LLHC04]

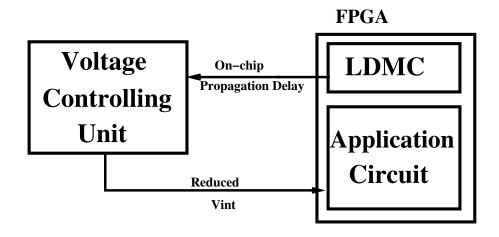

#### DVS dans les FPGAs du commerce

Une méthode pour supporter DVS sur les FPGAs commerciaux est proposée dans [LL05]. La tension de FPGA peut être gérée en temps réel. Pour maîtriser efficacement la réduction de la tension d'alimentation, un circuit spécial,LDMC(Logic Delay Measurement Circuit) est utilisé pour aider à ajuster dynamiquement la tension du FPGAs. La figure 1.7 illustre l'architecture du système avec l'implémentation de DVS. Dans ce

système, la tension est réglée par circuit externe du FPGAs. Parce qu'il n'y a pas encore de solution permettant au FPGA d'ajuster la tension par lui-même. Par conséquent, la technique DVS est souvent utilisée dans les microprocesseurs modernes et ASIC. Il y a moins d'exemples pour l'utilisation dans les FPGAs commerciaux.

FIGURE 1.7 – Exemple d'implémentation de DVS [LL05]

# 1.5 Potentiels des architectures reconfigurables

Dans la suite de ce travail, nous allons nous intéresser essentiellement aux architectures reconfigurables et nous présenterons des exemples d'architectures classées en tenant en compte de l'aspect granularité.

# 1.5.1 Architecture : les tendances principales

#### 1.5.1.1 Architecture reconfigurable à grain fin

Les premiers circuits reconfigurables (FPGA) ont été basés sur des éléments de traitement et des communications reconfigurables à grain fin. L'élément de traitement reconfigurable à grains fin est la LUT (Look Up table) qui permet de réaliser des fonctions combinatoires simples. A chaque élément configurable est associée une mémoire de configuration. Les technologies basées sur les mémoires SRAM permettent la reconfiguration par chargement de différents bitstreams.

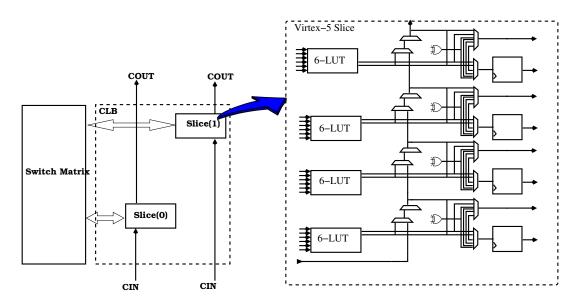

Les FPGAs commerciaux contiennent plusieurs LUT avec 3 à 6 entrées. La figure 1.8 illustre un exemple de LUT du FPGAs virtex-5. Par rapport aux anciennes versions de LUTs de FPGA à 4 entrées, elle permet de réaliser des fonctions de plus grandes tailles comme des RAM distribuées de 256 bits, registres à décalage de 128 bits et fonction à 8 entrées dans un même CLB. La reconfiguration de LUT est très flexible, et peut être utilisée pour réaliser n'importe quel circuit numérique. Cependant, les éléments fonctionnels reconfigurables à grain fin occupent substantiellement plus de surface, ont une grande latence, et consomment plus par rapport à des structures à grain épais. Néanmoins, dans les FPGAs modernes, on rencontre de plus en plus d'éléments de calcul à grain épais, tels que les multiplieurs, les DSPs jusqu'à des structures complexes en dur telles que les processeurs RISCs.

FIGURE 1.8 – Blocs logique configurable(CLBs) Virtex-5 contenant deux slices

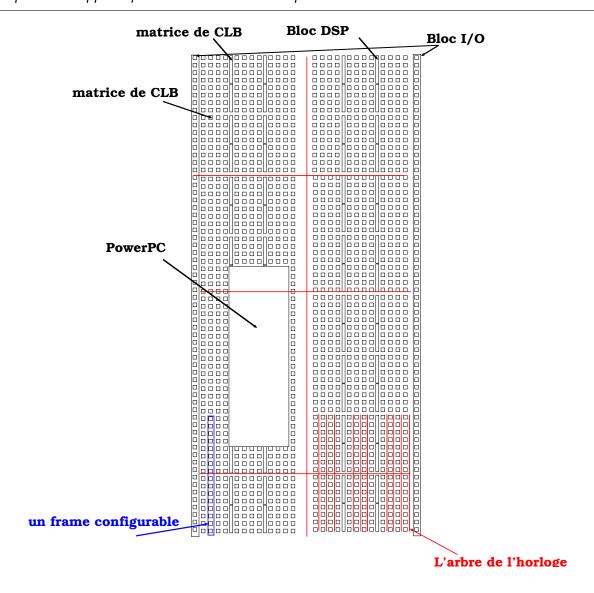

Les circuits FPGAs reconfigurables L'architecture interne des circuits FPGAs de la famille Virtex est détaillée dans les références [Inc05b] [Inc06] et [Inc05c]. L'unité reconfigurable est une trame (frame). Une trame est un ensemble de cellules logiques (CLB). Dans Virtex-II, celle-ci est une colonne qui occupe toute la longueur du circuit. Cependant, dans le cas des Virtex-4, 5 et 6, la trame a une taille de 16 CLBs (1.1). L'avantage de l'organisation de ces derniers circuits par rapport à Virtex-II est la possibilité de

définir les deux dimensions de la zone reconfigurable, alors que pour les Virtex-II une dimension est fixée (la colonne). La table 1.1 résume les caractéristiques principales des FPGAs à la famille Virtex. En plus, il est possible de définir des zones reconfigurables avec leur propre horloge fonctionnant grâce à une organisation en région d'horloge. La figure 1.9 illustre l'architecture d'un circuit Virtex-4 et la distribution de l'arbre de l'horloge.

TABLE 1.1 – Exemple de caractéristiques des FPGAs Virtex-II, Virtex-4 et Virtex-5

| Composant           | XC2VP                       | XC4V            | Virtex-5         |

|---------------------|-----------------------------|-----------------|------------------|

| architecture CLB    | 2 LUT4+ 2FF                 | 2LUT4+2FF       | 4LUT6+4FF        |

| Unité logique       | LUT à 4 entrées             | LUT à 4 entrées | LUT à 6 entrées  |

| zone minimale de RP | trame (longueur du circuit) | trame(16 CLB)   | trame16 CLB      |

| RAM distribuée      | 128 bits par CLB            | 64 bit par CLB  | 256 bits par CLB |

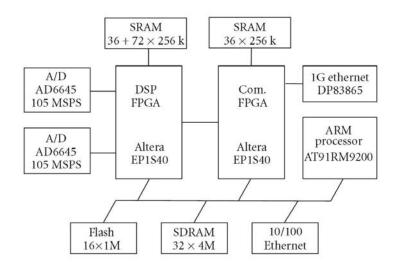

**Exemples d'architectures** *CASA*: est un système de traitement et d'acquisition. Celuici est utilisé dans les applications météo pour détecter les conditions dangereuses [RLAR05]. Un diagramme du système est donné dans la figure 1.10.

Un des deux FPGAs de CASA est dédié au traitement du signal (FPGA à gauche dans la figure), l'autre FPGA est responsable de la communication du résultat, mais peut aussi traiter les données en fonction de la configuration. Un microcontrôleur ARM exécutant Linux gère la ressource de configuration du FPGA. CASA contient aussi une série de mémoire (multi-banked memory), interfaces de réseau multiples, et des convertisseurs analogiques numériques (A/D). Dans cet exemple, le FPGA s'occupe du processus de communication. C'est un exemple appliqué dans un environnement qui demande beaucoup de puissance de calcul et différents algorithmes. L'un des avantages de cette architecture est les algorithmes de traitement exécutés sur le circuit FPGA qui peuvent être changés en réponse au changement des conditions météo. Cette configuration est effectuée au niveau grain fin dans le circuit FPGA. De plus, une fonction de contrôle à distance par le port ethernet augmente l'adaptabilité du système.

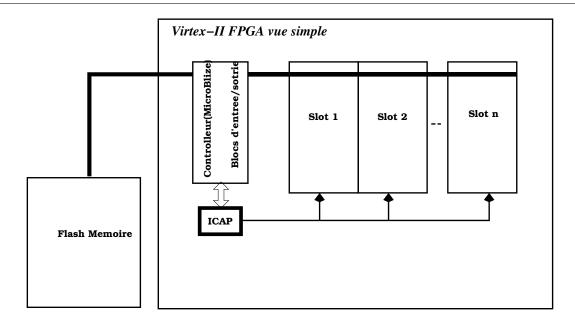

<u>System on-demand</u>: proposé par Ullmann et al. [UHGB04], est un système reconfigurable à grain fin sur la plate-forme de circuit FPGA Virtex-II Xilinx. Il est déve-

FIGURE 1.9 – Organisation interne de Virtex-4 de Xilinx

loppé pour les applications automobile industrielles [UHGB04]. Dans l'architecture de cette exemple 1.11, plus de trames reconfigurables sont connectées ensemble avec un bus du système. chaque trame peut être reconfigurée par des données de configuration (bitstreams) qui sont enregistré dans une mémoire flash . Un dialogue existe entre le contrôleur (microprocesseur) et le module reconfigurable pour identifier l'état du module reconfigurable en temps réel. Ce système est auto-adaptatif au niveau grain fin. Il supporte plus de flexibilité en utilisant la reconfiguration partielle. Et puis, il garde aussi le maximum de performance d'exécution grâce à l'implémentation du sys-

FIGURE 1.10 – Exemple de l'architecture CASA [RLAR05]

tème au niveau grain fin. Cependant, le choix de la taille de trame de reconfiguration est indépendant du nombre de fonctions logiques nécessaires à cause de la limitation de la méthode de reconfiguration dans le circuit FPGA. Celui-ci peut évoluer avec les nouveaux circuits FPGAs tels que Virtex-4,5. A cause de cette limitation, il n'y a pas une méthode pour distinguer comment choisir le nombre de zones reconfigurables ainsi que la consommation du circuit.

Bilan La reconfiguration d'une architecture à grain fin offre la plus grande flexibilité; ce qui peut être un point fort pour un système adaptatif. Elle permet de configurer les cellules logiques du circuit FPGA en fonction des différents besoins de l'application, pour spécialiser chaque tâche au maximum ce qui en général améliore l'efficacité. On peut par exemple ajuster la taille des opérateurs, le nombre de niveaux de pipeline, le taux de parallélisme, etc. Un autre intérêt est que les composants matériels ainsi que les outils bas niveau de génération de configurations sont facilement disponibles à faible coût. Enfin, certains de ces circuits possèdent une interface interne de reconfiguration, ce qui permet une forte intégration du système adaptatif complet.

Ces points forts des architectures reconfigurables à grain fin offrent une grande flexibilité pour la réalisation de système adaptatifs. Elles ont également quelques in-

FIGURE 1.11 – Exemple d'une architecture reconfigurable sur Virtex-II de [Ua04]

convénients tels que des temps de reconfiguration élevés, une augmentation de la surface, ainsi qu'une augmentation de la consommation d'énergie. Cependant, les dispositifs à grain fin sont en général limités par des temps de reconfiguration, une surface de silicium et une consommation d'énergie plus élevés que les structures à grains épais. A l'heure actuelle, ces architectures restent très efficaces d'un point de vue de l'adaptabilité de fonctionnement, mais inefficace d'un point de vue énergétique.

#### 1.5.1.2 Architecture reconfigurable à grain épais

Les circuits reconfigurables ont évolués depuis quelques années des grains fin à des structures à grain plus épais qui peuvent être des fonctions simples arithmétiques et logiques voir des processeurs élémentaires plus complexes. Alors que les architectures à grain fin sont plus adaptées aux traitements au niveau bit, les architectures à gros grains sont plus adaptées au traitement des données sur des mots de plus grandes tailles.

L'inadéquation des FPGAs avec certaines applications a amené les concepteurs à proposer d'autres modèles d'architectures. Les interconnexions et les opérateurs sont configurables dans ces architectures, mais travaillent au niveau arithmétique (par exemple

8 ou 16 bits). Ceci a pour effet d'améliorer les performances sur les traitements arithmétiques, au détriment des optimisations au niveau bit. Ces approches proviennent du fait que les applications sont constituées de cœurs de boucles très réguliers [ZBR00]. Ces architectures réduisent par ailleurs la taille des configurations, permettant d'envisager des stratégies de reconfiguration dynamique. La plupart de ces architectures utilisent un réseau d'interconnexion [ZWGR99] à deux dimensions, éventuellement hiérarchiques. On peut citer, par exemple, les architectures DRP-1 [DRP], Morphosys [LKS00], RaPiD [Cro99] ou le KressArray [HK95], Systolic Ring [G. 02]. Certaines architectures présentent une topologie linéaire comme le Piperench [GSM+99]. La taille des reconfigurations étant limitée, des mécanismes évolués peuvent ainsi être mis en œuvre pour distribuer les informations de configuration et réduire le coût (en consommation) du contrôle de ces architectures. Ces considérations ont été mises en œuvre dans les architectures Pleiades [Abn01]et DART [DCPS02], spécifiquement conçues pour la faible consommation.

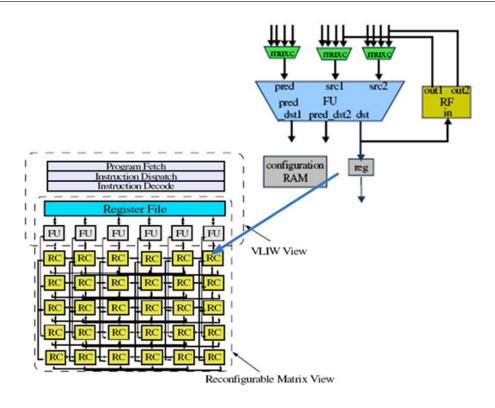

Exemples d'architectures <u>ADRES</u>: est une architecture reconfigurable à grain épais composée de deux parties : un processeur de type de VLIW et une matrice reconfigurable (fig.1.12) [MVV+03]. Dans la partie VLIW, certaines unités fonctionnelles (FU) sont connectées à un fichier de registres multi-ports (RF). La matrice reconfigurable contient des circuits reconfigurables (RC)(fig. 1.12). Chaque RC est un élément de calcul reconfigurable gros grains et correspond à une ALU 32 bits. La configuration de ces ALUs permet de réaliser des fonctions telles que l'addition, la multiplication et les fonctions logiques.

ADRES réduit d'abord la communication globale et la complexité de programmation grâce au partage des fichiers de registres et l'accès mémoire entre le processeur VLIW et la matrice reconfigurable.

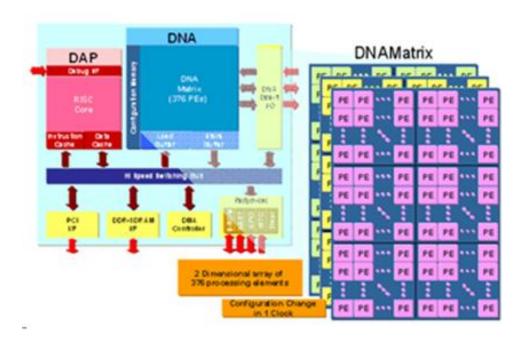

<u>DAP/DNA</u> est un processeur reconfigurable d'IPflex <sup>5</sup> qui possède une version de plate-forme reconfigurable dynamiquement. Le DAP/DNA consiste en une matrice d'éléments de calcul (PE) et un processeur RISC (DAP). La matrice permet une re-

<sup>5.</sup> www.IPflex.com

FIGURE 1.12 – Architecture ADRES

configuration en un cycle des 376 éléments de calcul et les interconnexions (fig. 1.13). Chaque élément de calcul peut être reconfiguré soit en mode séquentiel, soit en mode parallèle.

L'environnement de développement DAP/DNA-II permet d'assister le concepteur dans les différentes étapes du processus de développement jusqu'à l'implantation sur le composant. La flexibilité est offerte par la configuration d'interconnexion et la configuration de fonction de PE. La taille de DNA et la matrice de PE sont fixés.

**Bilan** Les systèmes reconfigurables à grain épais se présentent comme un bon compromis entre FPGAs et circuits spécifiques (ASICs). Ce type d'architecture est basé sur une adaptation au niveau du jeu d'instructions. Différentes fonctions sont réalisées par la reconfiguration de l'organisation du chemin de données dans chaque PE et l'interconnexion des PEs.

FIGURE 1.13 – Architecture DAP/DNA-2

#### 1.5.1.3 Architecture reconfigurable hétérogène

Afin de trouver un compromis entre ces différentes caractéristiques, des architectures hétérogènes ont été conçues notamment par des fabricants de FPGAs tels que Xilinx et Altera qui proposent différentes familles de circuits intégrant plus ou moins de blocs spécialisés (DSP, mémoire, transceiver, proceseurs) [Wol00]. Dans les circuits FPGAs actuellement commercialisés, on rencontre de plus en plus un mélange de granularité. En effet, certains éléments de calcul à grains épais sont embarqués dans ces FPGAs. Ce sont par exemple des multiplieurs, des modules "DSP", ou encore des processeurs sous forme d'IP (Nios, Microblize) ou en dur (PowerPCs pour Xilinx [Inc05b] [Inc04a]).

La structure d'architecture reconfigurable hétérogène est composée de différents types d'éléments de calcul à grain fin et/ou à grain épais. L'adaptation est réalisée par le choix de type de élément de calcul et les interconnexions entre ces éléments. Le type d'élément peut être changé en utilisant la reconfiguration partiel [Inc04b] [Inc05c] tel que [MCM+04]. L'interconnexion entre les éléments peuvent être également reconfigurée comme dans l'exemple aSoC [LLTB]

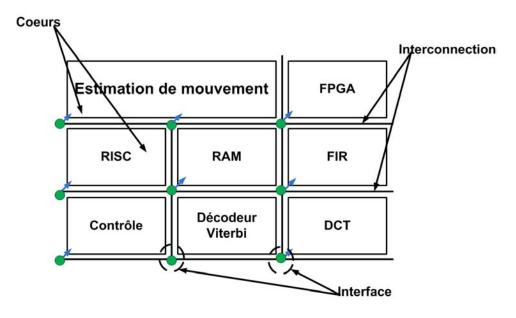

**Exemples d'architectures** <u>aSoC</u>: est une architecture basée sur un réseau d'interconnexions en point à point [LLTB]. Comme illustré sur la figure 1.14, les briques constitutives sont des éléments de traitement hétérogènes. L'architecture est constituée de briques qui peuvent être de granularités différentes. L'aSoC est très flexible puisque le concepteur peut définir les modules de calcul (IP) qu'il souhaite intégrer à son architecture.

Certaines briques peuvent être des briques reconfigurables de gros grain ou de grain fin. Les interfaces de communication de l'aSoC relient point à point les briques entre elles. Les instructions de connexions contrôlent un crossbar qui peut établir des liaisons entre les quatre briques du voisinage direct (au nord, au sud, à l'est et à l'ouest) de la brique dont il fait partie.

FIGURE 1.14 – Architecture aSoC

Le crossbar peut aussi créer une liaison entre une de ces briques de voisinage et le module de calcul avec lequel il peut communiquer. La figure 1.14 montre l'interface de communication d'une brique avec le crossbar et la mémoire d'instructions. Sur cette figure nous trouvons aussi un dispositif permettant la gestion dynamique de la consommation de puissance de la brique [LLTB]. L'un des avantages qu'offre cette architecture est qu'elle supporte des transferts de données ordonnancés que ce soit de manière statique hors ligne ou bien dynamique en ligne.

*FiPRe*: est un système reconfigurable basé sur du multi-processeurs [MCM+04]. Le coprocesseur, RISP (Reconfigurable instruction set processeur [BL00] [BLD02]), embarqué est responsable de l'accélération de certaines fonctions critiques. Ce modèle multi-processeur a été implémenté en utilisant la technologie Virtex-II Xilinx. De plus, il peut être inséré ou remplacé en temps réel. Le processeur RISPs est implémenté dans une zone reconfigurable. Ces processeurs peuvent être remplacés par des co-processeurs différents. Cependant, la taille de la zone reconfigurable est fixée dans la conception (4 colonnes CLBs/1280LUTs). En comparant avec *aSoC*, les modules de calcul *RISP* ne sont pas pré-implémentés sur le circuit. Chaque module de calcul est implémenté dans une zone reconfigurable. Il peut être remplacé par un autre co-processeurs tels que FFT opérateurs, filtrage d'image, etc.

$\underline{DyCORE}$ : est un système adaptatif qui est capable de reconfigurer une partie du système et peut s'adapter à différents comportements [AKM06]. Il est très similaire à aSoC dans lequel les éléments à grains épais et/ou à grain fin sont connectés ensemble sur un bus. Cependant, la grande différence avec ce dernier exemple tient dans le fait qu'il est modifiable par reconfiguration dynamique. Il est capable de réaliser une architecture multiprocesseur et aussi un architecture multi PEs matériel selon les besoins d'application. Un contrôleur d'adaptation est installé à côté du système.

**Bilan** Ce type d'architectures contient différents type d'éléments de calcul permettant d'adapter le fonctionnement d'une application spécifique. De nombreuses architectures (ex : ASoC) reconfigurables hétérogènes peuvent reconfigurer leur réseau d'interconnexion entres les éléments de calcul . Un des avantages de ces architectures, est la possibilité d'adapter le parallélisme de l'application à celui de l'algorithme exécuté. Cette spécificité autorise l'ajustement la fréquence de fonctionnement et/ou la tension d'alimentation en fonction du niveau de parallélisme de l'algorithme.

Très peu d'architectures (ex :DyCORE) reconfigurables hétérogènes peuvent reconfigurer leurs éléments de calcul. Un des avantages de ces architectures, est la possibilités de changer le type d'éléments de calcul pour adapter le fonctionnement spécifique de l'application.

Les trois types d'architectures décrivent les possibilités d'adaptation au niveau matériel. La plupart des études menées sur ce thème se concentrent uniquement sur le gain en performances et l'adaptabilité aux multi-fonctions au prix d'une consommation d'énergie non maîtrisée.

## 1.6 Conclusion

Dans ce chapitre, nous avons présenté les caractéristiques des architectures pouvant être utilisées comme SoCs adaptatifs au niveau matériel. Les éléments principaux sont décrits selon la granularité des éléments de calcul et d'interconnexion. Pour chaque type de granularité, différentes architectures sont analysées. Malgré la quantité d'architectures existantes, le marché est encore dominé par les FPGAs, en particulier ceux de Xilinx et Altera.

Grâce à la reconfiguration partielle dynamique dans le circuit FPGA, il est possible de réduire le problème des temps de reconfigurations prohibitifs. Le surplus de surface peut être partiellement compensé par une augmentation de la fonctionnalité apparente permise par la flexibilité du système. Le problème principal à résoudre reste la consommation énergétique, induite principalement par le système de routage intercellules [SN05] [DPF+00]. Cette contrainte, bien que unanimement reconnue comme l'une des plus critiques pour les systèmes embarqués [Bol07], n'est quasiment jamais prise en compte lors de la conception des architectures reconfigurables.

Notre objectif n'est pas de concevoir un système avec une meilleure performance ou une meilleure consommation d'énergie, mais de proposer un moyen permettant de trouver un compromis entre la consommation d'énergie et les performances lors de l'exécution de l'application. Et surtout, d'adapter ce compromis aux variations des conditions de fonctionnement de l'application.

Pour atteindre cet objectif, nous exploitons le parallélisme offert par les circuits FP-GAs et sa mise en oeuvre dynamique par reconfiguration partielle dynamique en permettant d'implémenter différentes versions et le nombre adéquat d'instances d'une tâches. La gestion dynamique du parallélisme est associée à la gestion dynamique

de fréquence afin de permettre au système de s'adapter au nouvel environnement et de garantir toujours l'efficacité énergétique et les performances nécessaires. Cette méthode sera développée dans le chapitre suivant.

# **Chapitre 2**

# Méthode et stratégie d'adaptation

### **Sommaire**

| Sommane |     |                                                        |                                                                |    |  |  |  |

|---------|-----|--------------------------------------------------------|----------------------------------------------------------------|----|--|--|--|

|         | 2.1 | Introduction                                           |                                                                |    |  |  |  |

|         | 2.2 | Problématique et applications cibles                   |                                                                |    |  |  |  |

|         | 2.3 | Puissance et énergie dans les applications périodiques |                                                                |    |  |  |  |

|         |     | 2.3.1                                                  | Puissance dynamique                                            | 39 |  |  |  |

|         |     | 2.3.2                                                  | Énergie consommée                                              | 40 |  |  |  |

|         | 2.4 | Efficacité énergétique                                 |                                                                |    |  |  |  |

|         | 2.5 | Modèle architectural                                   |                                                                |    |  |  |  |

|         |     | 2.5.1                                                  | Unité de calcul Reconfigurable-RPM                             | 46 |  |  |  |

|         |     | 2.5.2                                                  | Contrôleur d'adaptation                                        | 52 |  |  |  |

|         | 2.6 | Méthode d'adaptation dynamique                         |                                                                |    |  |  |  |

|         |     | 2.6.1                                                  | Fonction de transition                                         | 55 |  |  |  |

|         |     | 2.6.2                                                  | Contexte d'applications spécifiques pour un système temps réel | 55 |  |  |  |

|         |     | 2.6.3                                                  | Prise en compte de l'efficacité énergétique                    | 58 |  |  |  |

|         |     | 2.6.4                                                  | Étapes de l'adaptation et leur objectif                        | 60 |  |  |  |

|         |     | 2.6.5                                                  | Méthode d'adaptation d'un traitement multi-tâches              | 66 |  |  |  |

|         |     | 2.6.6                                                  | Résumé du fonctionnement du système d'adaptation               | 66 |  |  |  |

|         | 2.7 | Concl                                                  | usion                                                          | 68 |  |  |  |

### 2.1 Introduction

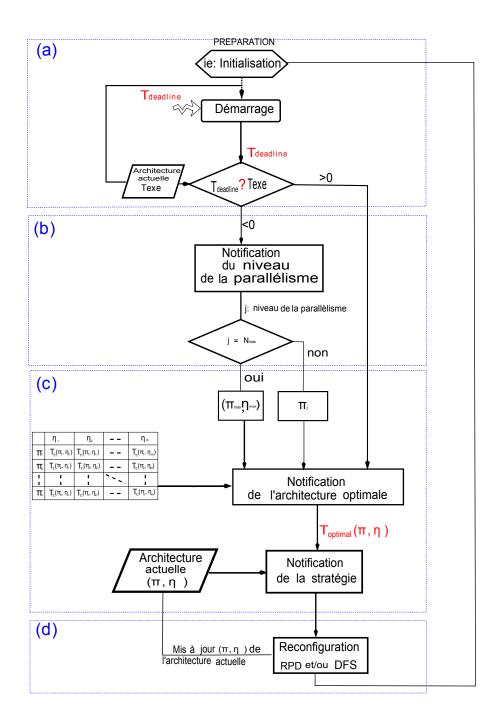

Ce chapitre présente la méthodologie d'adaptation proposée. Dans ce travail, nous nous concentrons sur les deux méthodes : DRP et DFS. La reconfiguration partielle (DRP) nous permet de modifier le niveau du parallélisme des tâches. La reconfiguration de fréquence (DFS) de traitement permet d'obtenir la fréquence de traitement juste suffisante pour respecter la contrainte de temps et de réduire le temps d'attente. Le prototypage d'un système adaptatif selon ces méthodes ainsi que les éléments principaux de son architecture sont présentés. Ensuite, nous montrons qu'il est possible d'améliorer le rendement des implantations à l'aide de notre méthode (le niveau de parallélisme et la fréquence de traitement) tout en respectant la contrainte de temps.

# 2.2 Problématique et applications cibles

Dans la majorité des applications multimédia, un flot de données subit des traitements successifs qui peuvent être organisés sous forme de tâches avec une dépendance de données. Le temps d'exécution de ces applications dépend des temps d'exécutions des tâches et de la cible d'implémentation. Dans le cas d'une exécution sur un processeur unique, ce temps est la somme des temps d'exécution de chaque tâche. Plusieurs techniques permettent de réduire ce temps d'exécution comme la parallélisation par pipeline. Généralement, les traitements dans ces applications multimédias sont effectués de manière périodique et la période de traitement  $T_D$  corresponds à une contrainte à respecter.

Les temps d'exécution des tâches ne sont pas les mêmes et sont inférieurs à la période de l'application. La plupart des architectures sont surdimensionnées pour que le temps d'exécution des tâches soit toujours inférieur à la période. De ce fait, la durée d'attente des processeurs (matériels ou logiciels) peut être non négligeable et a un effet sur la consommation de puissance et bien entendu sur l'efficacité énergétique et l'efficacité d'utilisation de l'architecture.

Le temps d'attente est souvent exploité pour réduire la consommation en échelon-

nant dynamiquement la fréquence de fonctionnement et la tension d'alimentation. On peut ainsi atteindre un état de fonctionnement optimal pour des conditions de fonctionnement fixées. Lorsque ces conditions changent, par exemple dans le cas où la quantité de données à traiter augmente il est alors nécessaire d'agir sur l'organisation du système pour assurer le fonctionnement et d'atteindre un nouvel état optimal. Cette action peut se faire en allouant des ressources supplémentaires et en agissant sur les fréquences et tensions d'alimentation dans les limites possibles. Il est en conséquence nécessaire de prévoir un mécanisme permettant d'assurer conjointement ces actions. Évidemment, on ne peut utiliser que les ressources disponibles en les réorganisant de manière efficace.

Notre contribution dans ce domaine est d'associer la gestion dynamique de fréquence et de tension avec la reconfiguration dynamique partielle pour adapter la consommation d'un système en fonction des variations de la quantité de données traitées.

# 2.3 Puissance et énergie dans les applications périodiques

Dans cette étude nous nous intéressons essentiellement à la puissance dynamique dissipée dans les circuits CMOS de type FPGA. La puissance statique est considérée constante et dépendant du type de circuit choisi. Elle est dissipée quand le circuit lorsqu'il est alimenté, et elle est indépendante de l'activité du circuit.

# 2.3.1 Puissance dynamique

La puissance dynamique est dissipée lorsque le circuit est actif et les valeurs des signaux changent [Cur07]. Les signaux peuvent être des signaux de logique, d'horloge ou des signaux entrées/sorties. La dissipation est due aux commutations (charge et décharge des capacités du circuit) et aux courents de court-circuit pendant le phase de commutation. Les études menées pour estimer la dissipation de puissance dans les FPGAs [A.D00, LAK02] montrent toutes que 60 à 70% de la puissance est due aux interconnexions, 20% à la distribution d'horloge et le reste se répartit entre les blocs

de calcul et les entrées/sorties. L'expression simplifiée de la puissance dynamique est donnée par l'équation 2.1 [TGM07] :

$$P_{dyn} = C_L * V_{dd}^2 * P_{trans} * f_{clk}$$

$$\tag{2.1}$$

Où,  $P_{trans}$  est la probabilité de transition,  $C_L$  est la capacité de charge et  $f_{clk}$  est la fréquence de l'horloge de communication. Si nous définissons :

$$C_{eff} = P_{trans} * C_L (2.2)$$

Nous pouvons aussi décrire la puissance dynamique avec une expression plus familière :

$$P_{dyn} = C_{eff} * V_{dd}^2 * f_{clk} {2.3}$$