# Recherche des performances dans la mise en oeuvres des codes linéaires cycliques en ASIC à haut debit

Thierry Vallino

# ▶ To cite this version:

Thierry Vallino. Recherche des performances dans la mise en oeuvres des codes linéaires cycliques en ASIC à haut debit. Sciences de l'ingénieur [physics]. Université Paul Verlaine - Metz, 1999. Français. NNT: 1999METZ053S . tel-01749117

# HAL Id: tel-01749117 https://hal.univ-lorraine.fr/tel-01749117v1

Submitted on 29 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

# LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

SIN2 99153

# Thèse

présentée par

# **VALLINO Thierry**

pour l'obtention du titre de

Docteur de l'Université de Metz en Micro-électronique

# Recherche des performances – dans la mise en œuvres des codes linéaires cycliques en ASIC à haut débit.

Soutenue le 17 décembre 1999

Composition du jury:

## Rapporteur:

M. CALVEZ Jean Paul:

Professeur, IRESTE-Université de Nantes

M. PIESTRAK Stanislaw:

Professeur, Université de Wroclaw

Directeur de thèse:

M. LEPLEY Bernard:

Professeur, Université de Metz

# Examinateurs:

M. BRAUN Francis:

Professeur, Université de Strasbourg

M. DANDACHE Abbas:

Maître de Conférences, Université de Metz

M. DELAHAYE Jean Pierre:

Ingénieur TDF-C2R Metz

M. MONTEIRO Fabrice:

Maître de Conférences, Université de Metz

#### LICM / CLOES

Laboratoire Interfaces Composants et Microélectronique Centre Lorrain d'Optique et d'Electronique des Solides

Université de Metz et SUPELEC

# Thèse

présentée par

# **VALLINO Thierry**

pour l'obtention du titre de

Docteur de l'Université de Metz en Micro-électronique

| BIBLIOTHEOLIE UNIVERSITAIRE<br>. METZ |           |  |  |  |

|---------------------------------------|-----------|--|--|--|

| N° inv.                               | 19991555  |  |  |  |

| Cote                                  | SM3 99/53 |  |  |  |

| Loc                                   | Magasin   |  |  |  |

# Recherche des performances dans la mise en œuvres des codes linéaires cycliques en ASIC à haut débit.

Soutenue le 17 décembre 1999

Composition du jury:

#### Rapporteur:

M. CALVEZ Jean Paul:

Professeur, IRESTE-Université de Nantes

M. PIESTRAK Stanislaw:

Professeur, Université de Wroclaw

Directeur de thèse:

M. LEPLEY Bernard:

Professeur, Université de Metz

#### Examinateurs:

M. BRAUN Francis:

Professeur, Université de Strasbourg

M. DANDACHE Abbas:

Maître de Conférences, Université de Metz

M. DELAHAYE Jean Pierre:

Ingénieur TDF-C2R Metz

M. MONTEIRO Fabrice:

Maître de Conférences, Université de Metz

# LICM / CLOES

Laboratoire Interfaces Composants et Microélectronique Centre Lorrain d'Optique et d'Electronique des Solides Université de Metz et SUPELEC

# REMERCIEMENTS

Je tiens tout d'abord à remercier M. Bernard LEPLEY, directeur du LICM/CLOES pour m'avoir accepté dans son laboratoire et pour les conseils qu'il m'a fournis tout au cours de ce travail.

Je tiens aussi à remercier M. Abbas DANDACHE et M. Fabrice MONTEIRO pour avoir pris sur leur temps pour encadrer cette thèse et pour les conseils qu'ils m'ont apportés.

Je remercie tout particulièrement M. CALVEZ et M. PIESTRAK pour avoir bien voulu être les rapporteurs de mon travail.

Enfin, je voudrais remercier les autres membres du jury, M. BRAUN, M. DELAHAYE, pour avoir bien voulu examiner ce travail.

Je tiens tout particulièrement à remercier les thésard du laboratoire Angélique, Hervé, Jean Philippe, Serge et les membres du CESIUM Gaëlle, Jean-François et Rémy pour m'avoir « supporter » pendant ces années et pour l'ambiance conviviale qu'ils ont créé.

Enfin, je remercie également ma famille et tous mes amis pour leur soutien moral.

# Résumé

L'essor des télécommunications est un des faits marquant de cette fin du siècle. Il s'accompagne d'un accroissement des applications dédiées (télévision numérique, Internet). Cependant, les voies de transmissions ne sont pas parfaites et peuvent corrompre les données émises. L'utilisation des codes correcteurs d'erreurs permets alors dans une certaine mesure d'y remédier. Notre travail s'est articulé autour de deux axes.

Le premier axe a consisté à trouver et développer l'architecture d'un codeur/décodeur à logique majoritaire fonctionnant à haut débit et pouvant traiter des flots continus de données. L'étude des différentes implantations possibles de diviseur polynomial (cœur du codeur/décodeur) a permis de montrer que l'architecture parallèle était la mieux adaptée à nos contraintes. Celle-ci a été décrite en VHDL synthétisable et simulée sous le logiciel Altera MaxPlus II. A partir de cette description, l'impact du degré de parallélisme sur la surface et le débit du codeur/décodeur a été étudié sur plusieurs codes à logique majoritaire (DSCC, DTI, EG). Il en ressort que l'augmentation du débit est nettement plus importante que celle de la surface (circuit EPF10K10LC84-3).

Le deuxième axe de recherche a consisté à une étude de faisabilité dans la mise en œuvre d'un code Reed-Solomon avec effacements. La méthode des effacements permets d'accroître la capacité de correction des codes Reed-Solomon d'origine au moyen d'une technique de marquage. Habituellement, l'implantation des codes RS avec effacements est réalisée mais sans mettre en œuvre la technique de marquage. Un tel marquage a été développé et simulé en coopération avec TDF-C2R. La simulation ayant permis de valider cette technique, un codeur/décodeur RS (127,121,7) a été décrit en VHDL synthétisable et simulé sous le logiciel Altera MaxPlus II. Les résultats ont permis de montrer que les performances d'un tel circuit sont comparables à celles des circuits usuels n'implantant pas le marquage.

Mot-clé: logique majoritaire, architecture parallèle, Reed-Solomon, effacements, codes linéaire cycliques

## **Abstract**

Recent progress in telecommunication is the most important fact of this end of century. It is accompanied by a growth of dedicated applications (numerical TV, internet,...). However, media are not perfect and can corrupt the emitted data. The use of error correcting code permits to detect and correct the errors at the receipt.

The first part of this research was to find and develop an architecture of majority logic codec which can be used with high output throughput data stream. The study of the different implementation of the polynomial divider (core of the codec) allowed us to demonstrate the parallel architecture was the better choice compared with our constraints. This one has been described in VHDL and simulated with MaxplusII software of Altera. Using this description, the impact of the parallelism degree on both the area and the output throughput of the codec has been studied for different code (DTI, DSCC, EG).

The second part of this research was to implement a "Reed-Solomon with erasures" codec in ASIC. The use of erasure increases the error capability of the original Reed-Solomon code. An erasure processing (developed in co-operation with TDF) has been validated through the simulation based on several error models. After this validation, a (127,121,7) RS code with erasures has been described in VHDL and simulated with MaxplusII software of Altera in order to cope with the constraints of real time applications.

Keywords: majority logic, parallel architecture, Reed-Solomon, erasures, linear cyclic codes

# **Sommaire**

| REMERCIEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| RÉSUMÉ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                          |

| SOMMAIRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                          |

| LISTE DES FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                          |

| BIBLIOGRAPHIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                         |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 14                                                                       |

| CHAPITRE I. LES CODES CORRECTEURS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                         |

| I.1. Généralités  I.1.1. Position du problème I.1.2. Solutions possibles pour la détection et la correction des erreurs I.1.2.1.Systèmes avec ARQ (Automatic Repeat reQuest). I.1.2.2.Codes correcteurs d'erreurs I.1.2.3. Systèmes hybrides I.1.3. Conclusions  I.2. Les codes linéaires.                                                                                                                                                                                                                                                                                                                                                                                                        | 18<br>18<br>20<br>20<br>23<br>24<br>25                                     |

| <ul> <li>I.2.1. Rappels mathématiques</li> <li>I.2.1.1. Structure de groupe</li> <li>I.2.1.2. Structure de corps</li> <li>I.2.1.3. Structure d'espace vectoriel</li> <li>I.2.2. Les codes linéaires</li> <li>I.2.2.1. Codes en blocs</li> <li>I.2.2.2. Code linéaire, Matrice génératrice, Matrice de contrôle</li> <li>I.2.2.3. Décodage des codes linéaires</li> <li>I.2.2.3.1. Décodage par tableau standard</li> <li>I.2.2.3.2. Décodage par syndrôme</li> </ul>                                                                                                                                                                                                                              | 26<br>26<br>26<br>27<br>27<br>29<br>30<br>30<br>33                         |

| <ul> <li>I.3. Les codes cycliques</li> <li>I.3.1. Définition</li> <li>I.3.2. Polynôme générateur.</li> <li>I.3.3. Processus d'encodage.</li> <li>I.3.3.1. Codage systématique.</li> <li>I.3.3.2. Algorithme de codage par division.</li> <li>I.3.3.3. Exemple d'implantation d'un codeur par division.</li> <li>I.3.3.3.1. Préliminaire- conception d'un multiplicateur</li> <li>I.3.3.3.2. Circuit de division.</li> <li>I.3.3.3.3. Propriétés.</li> <li>I.3.4. Processus de décodage</li> <li>I.3.4.1. Détection des erreurs</li> <li>I.3.4.2. Correction des erreurs : le décodeur de Meggitt</li> <li>I.3.4.2.1. Propriété du syndrôme</li> <li>I.3.4.2.2. Le décodeur de Meggitt.</li> </ul> | 34<br>34<br>34<br>35<br>35<br>36<br>37<br>37<br>38<br>39<br>40<br>40<br>41 |

| 1.4. Conclusions                                                                  | 44       |

|-----------------------------------------------------------------------------------|----------|

| CHAPITRE II. LES CODES À LOGIQUES MAJORITAIRES                                    | 45       |

| II.1. Le décodage à logique majoritaire                                           | 4:       |

| II.1.1. Principe de décodage [13]                                                 | 4:       |

| II.1.2. Le code Difference Set Cyclic Code (DSCC) [24]                            | 4        |

| II.1.2.1. Série parfaite de différence finie                                      | 4        |

| II.1.2.2. Construction du polynôme générateur [24]                                | 48       |

| II.1.2.3. Construction de la matrice W [9]                                        | 49       |

| II.1.2.4. Exemple des éléments d'un code DSCC                                     | 50       |

| II.1.3. Code Doubly Transitive Invariant (DTI)                                    | 51       |

| II.1.3.1. Théorie mathématique II.1.3.1.1. Permutation affine                     | 5:       |

| II.1.3.1.2. Propriété d'invariance                                                | 51       |

| II.1.3.1.2.1 Notion de descendance                                                | 52<br>52 |

| II.1.3.1.2.2. Invariance                                                          | 52       |

| II.1.3.2. Code DTI de type 0                                                      | 52       |

| II.1.3.2.1. Construction du polynôme générateur                                   | 53       |

| II.1.3.2.2. Construction de la matrice W                                          | 53       |

| II.1.3.2.3. Exemple                                                               | 54       |

| II.1.3.3 Code DTI de type I                                                       | 56       |

| II.1.4. Code Euclidean Geometry (EG)                                              | 57       |

| II.1.4.1. Bref rappel sur la géométrie euclidienne                                | 57       |

| II.1.4.1.1. Définition de l'espace EG                                             | 57       |

| II.1.4.1.2. Ligne dans EG(m,2 <sup>s</sup> ).                                     | 58       |

| II.1.4.2. Définition du code EG d'ordre s.                                        | 58       |

| II.1.4.2.1. Définition du vecteur d'incidence.                                    | 58       |

| II.1.4.2.2. Exemple II.1.4.2.3. Les codes EG                                      | 59       |

| II.1.4.3. Construction du polynôme générateur                                     | 60       |

| II.1.4.3.1. Définition de la fonction W <sub>2</sub> <sup>s</sup>                 | 60<br>60 |

| II.1.4.3.2. Construction du code générateur                                       | 61       |

| II.1.4.3.3. Exemple.                                                              | 61       |

| II.1.4.4. Construction de la matrice W                                            | 62       |

| II.1.5. Conclusions                                                               | 63       |

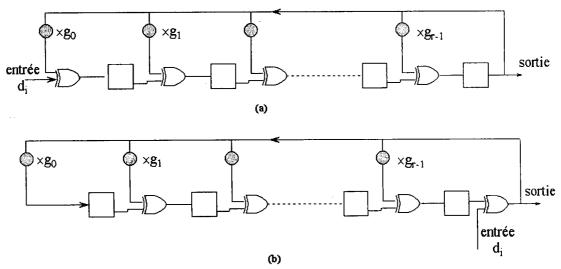

| II.2. Implantation du codeur                                                      | 63       |

| II.2.1. Choix de l'architecture                                                   | 63       |

| II.2.1.1. Architecture série                                                      | 63       |

| II.2.1.2. Architecture systolique [17]                                            | 64       |

| II.2.1.2.1 Présentation                                                           | 64       |

| II.2.1.2.2 Avantages et inconvénients                                             | 68       |

| II.2.1.4. Architecture Parallèle                                                  | 69       |

| II.2.1.4.1. Architecture asynchrone ICC                                           | 69       |

| II.2.1.4.2. Architecture parallèle synchrone II.2.1.4.2.1. Architecture de type 1 | 71       |

| II.2.1.4.2.2. Architecture de type 2                                              | 71       |

| II.2.1.4. Conclusions                                                             | 73<br>74 |

| II.2.2 Architecture parallèle du codeur                                           | 75       |

| II.2.2.1. Le circuit de codage                                                    | 75       |

| II.2.2.1.1. Principe de fonctionnement du circuit de codage                       | 75       |

| II.2.2.1.2. Vue générale du circuit de codage                                     | 77       |

| II.2.2.2. Mémoires                                                                | 77       |

| II.2.2.2.1. Systèmes avec RAM                                                     | 78       |

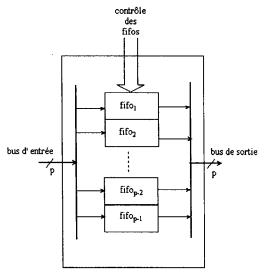

| II.2.2.2.1. Systèmes avec Fifo                                                    | 79       |

| II.2.2.2.1.1. Cellule de base de la FIFO asynchrone d'entrée                      | 79       |

| II.2.2.2.1.2. Cellule de base de la FIFO asynchrone de sortie                     | 80       |

| II.2.2.2.1.3. Génération de la FIFO asynchrone                                    | 80       |

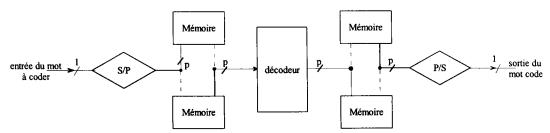

| II.2.2.3. Conversion série/parallèle                                              | 82       |

| II.2.2.4. Conversion parallèle/série                                                 | 84              |

|--------------------------------------------------------------------------------------|-----------------|

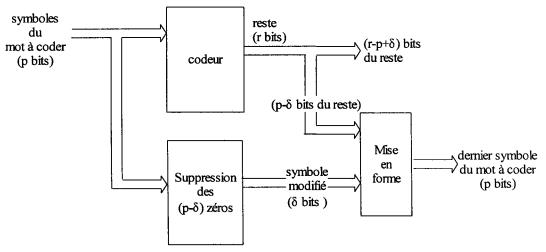

| II.2.2.5. Codeur                                                                     | 84              |

| II.2.2.5.1. Diviseur                                                                 | 85              |

| II.2.2.5.2. Mise en Forme                                                            | 88              |

| II.2.2.5.3. Cœur du codeur                                                           | 89              |

| II.2.3 Conclusions                                                                   | 90              |

|                                                                                      | 01              |

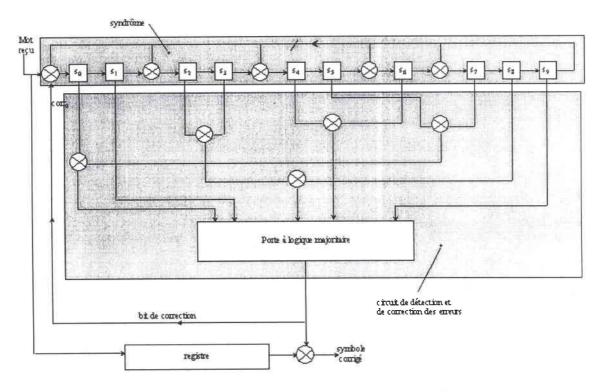

| II.3. Implantation du décodeur                                                       | <b>91</b><br>91 |

| II.3.1. Choix de l'architecture.                                                     | 91              |

| II.3.1.1. Architecture série.                                                        | 92              |

| II.3.1.2. Architecture en pipeline.                                                  | 95              |

| II.3.1.3. Architecture Parallèle. II.3.1.3.1. Détection et localisation des erreurs. | 95              |

| II.3.1.3.2. Correction des erreurs                                                   | 97              |

| II.3.1.3.3. Cas des codes raccourcis.                                                | 99              |

| II.3.1.3.4. Circuit de décodage                                                      | 100             |

| II.3.1.4.1. Conclusions                                                              | 102             |

| II.3.2. Réalisation du décodeur                                                      | 102             |

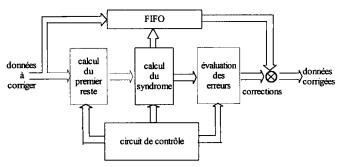

| II.3.2.1. Schéma général du décodeur                                                 | 102             |

| II.3.2.2. La conversion parallèle/série                                              | 103             |

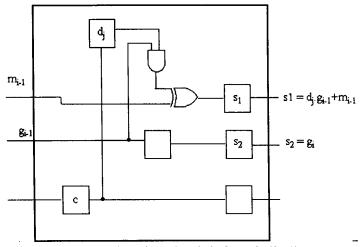

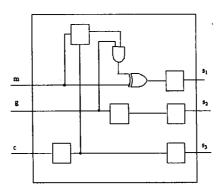

| II.3.2.3. Le circuit de décodage                                                     | 105             |

| II.3.2.3.1. La porte à logique majoritaire                                           | 105             |

| II.3.2.3.1.1. Méthode par comptage                                                   | 105             |

| II.3.2.3.1.2. Méthode par tri                                                        | 106             |

| II.3.2.3.1.3. Choix de la méthode                                                    | 108             |

| II.3.2.3.2. La matrice W                                                             | 108             |

| II.3.2.3.3. Le syndrome                                                              | 109             |

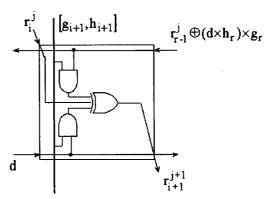

| II.3.2.3.4.Cœur du décodeur                                                          | 110             |

| II.3.3. Conclusions.                                                                 | 112             |

| II.4 Résultat                                                                        | 112             |

| II.4.1. Etude du codeur.                                                             | 112             |

| II.4.1.1. Méthodologie                                                               | 112             |

| II.4.1.3. Etude en débit et en surface du diviseur parallèle                         | 114             |

| II.4.1.3 Circuit de codage.                                                          | 115             |

| II.4.1.4 Conclusion.                                                                 | 116             |

| II.4.2. Etude du décodeur.                                                           | 117             |

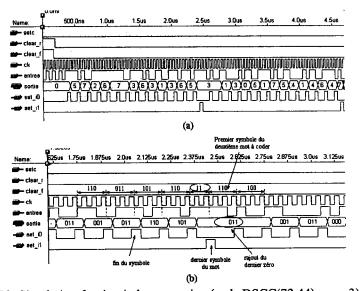

| II.4.2.1. Méthodologie de validation du décodeur                                     | 117             |

| II.4.2.2. Etude du décodeur.                                                         | 117             |

| II.4.2.2.1. Validation de l'architecture « pipelinée »                               | 117             |

| II.4.2.2.2. 2. Etude de la surface de l'architecture « pipelinée »                   | 118             |

| II.4.2.3. Circuit de décodage.                                                       | 119             |

| II.5. Conclusions et perspectives                                                    | 120             |

| CHAPITRE III.                                                                        | 121             |

| LE CODE REED-SOLOMON (127,K,D) AVEC EFFACEMENTS                                      | 121             |

| III.1. La théorie des codes Reed-Solomon                                             | 122             |

| III.1.1. Présentation du code                                                        | 122             |

| III.1.1.1. Construction du polynôme générateur                                       | 122             |

| III.1.1.2. Caractéristique du mot code                                               | 122             |

| III.1.1.3. Exemple                                                                   | 123             |

| III.1.2. Algorithme de décodage                                                      | 125             |

| III.1.2.1. Evaluation de S                                                           | 125             |

| III.1.2.2. Localisation des erreurs et correction                                    | 125             |

| III.1.2.2.1. Localisation des erreurs                                                | 125<br>126      |

| III.1.2.2.2. Correction des erreurs                                                  | 120             |

| III 1 2 2 Algorithma do Doulelraura                                               | 107 |

|-----------------------------------------------------------------------------------|-----|

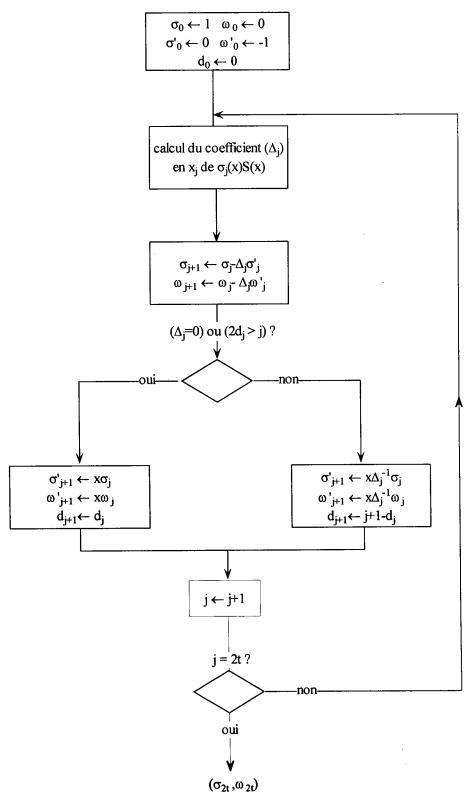

| III.1.2.3. Algorithme de Berlekamp.                                               | 127 |

| III.1.2.4. Exemple.                                                               | 130 |

| III.1.3. Prise en compte des effacements                                          | 133 |

| III.1.3.1. Position du problème et première conséquence                           | 133 |

| III.1.3.2. Méthode de Forney                                                      | 134 |

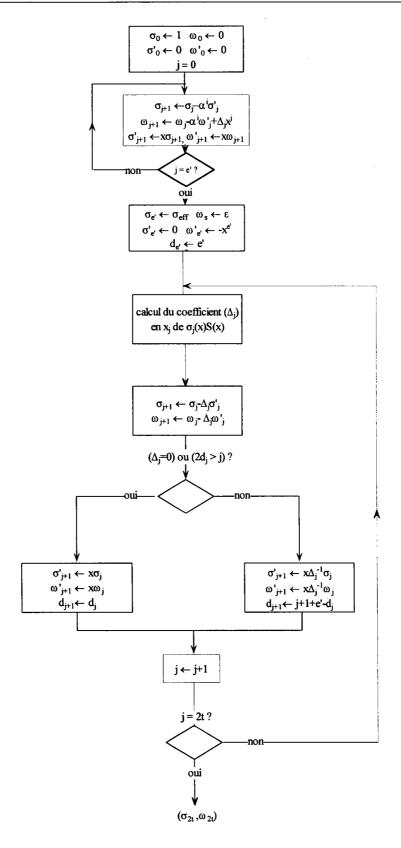

| III.1.3.2. Algorithme de Berlekamp modifié                                        | 135 |

| III.1.3.3. Exemple                                                                | 137 |

| III.2. Simulation et implantation du code Reed Solomon (127,k,d) avec effacements | 139 |

| III.2.1. Code de RS(127,k,d) avec effacements                                     | 140 |

| III.2.2.Simulation                                                                | 141 |

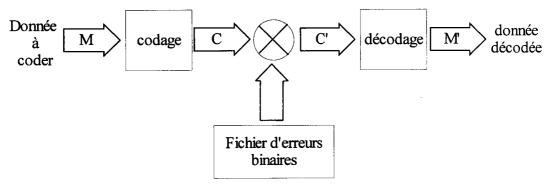

| III.2.2.1. Principe de simulation                                                 | 141 |

| III.2.2.2. Résultat                                                               | 142 |

| III.2.3. Implantation                                                             | 145 |

| III.2.3.1. Choix du multiplieur.                                                  | 146 |

| III.2.3.2. Implantation du codeur                                                 | 147 |

| III.2.3.3. Implantation du décodeur                                               | 149 |

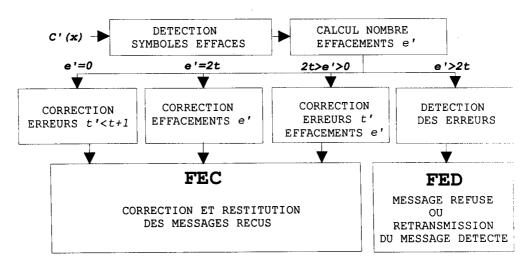

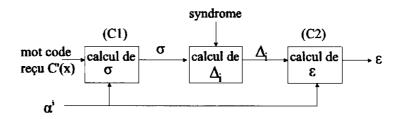

| III.2.3.3.1. Principe de correction                                               | 149 |

| III.2.3.3.2. Organisation générale                                                | 150 |

| III.2.3.3.3. Calcul du syndrome                                                   | 151 |

| III.2.3.3.4. Implantation de l'algorithme de Berlekamp                            | 152 |

| III.2.3.3.5. Localisation et évaluation des erreurs                               | 156 |

| III.2.3.3.5. Résultats                                                            | 157 |

| III.3. Conclusions                                                                | 158 |

| CONCLUSION GÉNÉRALE.                                                              | 160 |

| ANNEXE A. LES CORPS DE GALOIS.                                                    | 164 |

| I. Définition des corps de Galois                                                 | 164 |

| I.1. Définition                                                                   | 164 |

| I.2. Caractéristique du corps de Galois                                           | 165 |

| I.3. ordre de GF(q)                                                               | 165 |

| I.4. Autres propriété de GF(q)                                                    | 166 |

| II. Le corps de Galois GF(2 <sup>m</sup> )                                        | 166 |

| II.1. Définitions                                                                 | 166 |

| II.1.1. Polynôme irréductible                                                     | 166 |

| II.1.2. Polynôme primitif                                                         | 167 |

| II.2. Le corps GF(2 <sup>m</sup> )                                                | 167 |

| II.2.1. Construction du corps GF(2 <sup>m</sup> )                                 | 167 |

| II.3. Propriétés de GF(2 <sup>m</sup> )                                           | 169 |

| II.3.1. Conjugué d'un élément de GF(2 <sup>m</sup> ) et propriétes                | 169 |

| II.3.2. Polynôme minimal et propriétés                                            | 170 |

|                                                                                   |     |

# Liste des figures

| Tableau 1. Types de bruits pouvant intervenir dans une transmission.                            | 19 |

|-------------------------------------------------------------------------------------------------|----|

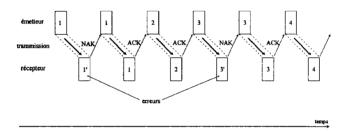

| Fig I-1. Exemple de fonctionnement d'un système « Stop and Wait ARQ ».                          | 21 |

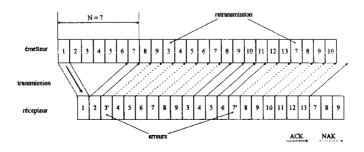

| Fig I-2. Exemple d'un système Go back 7 ARQ                                                     | 21 |

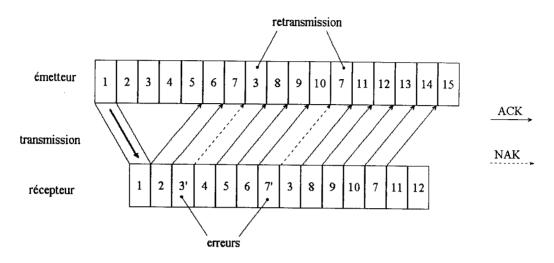

| Fig I-3. Exemple de fonctionnement d'un système « selective repeat ARQ »                        | 22 |

| Fig I-4. Exemple d'utilisation d'un code correcteur d'erreur                                    | 23 |

| Tableau 2. Résumé des différentes méthodes de corrections des erreurs                           | 25 |

| Fig I-5. Représentation générale du système de communication considéré                          | 28 |

| Fig I-6. Exemple d'implantation de codeur                                                       | 30 |

| Fig I-7. Principe de décodage des codes linéaires                                               | 31 |

| Fig I-8. Tableau standard pour un code linéaire $C(n,k)$ [p = $2^{n-k}$ -1, M = $2^k$ -1]       | 32 |

| Fig I-9. Caractéristiques du code (7,4)                                                         | 32 |

| FigI-10. Tableau Standard utilisé pour le décodage du code (7,4)                                | 33 |

| Fig I-11. Implantation générale d'un décodeur pour un code linéaire                             | 34 |

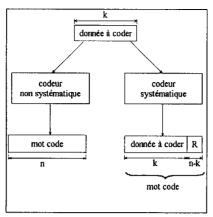

| Fig I-12. Principe d'un codage systématique.                                                    | 36 |

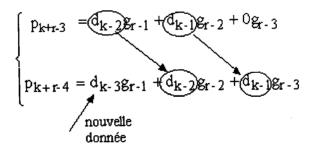

| Fig I-13. Principe du multiplieur                                                               | 37 |

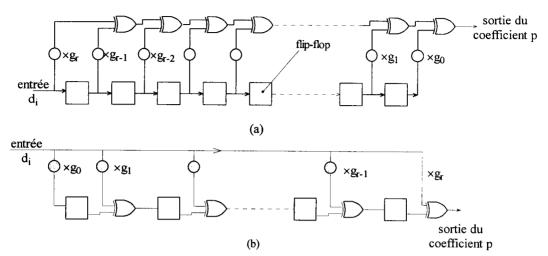

| Fig I-14. Circuit de multiplication de deux polynômes                                           | 38 |

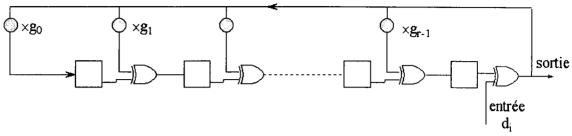

| Fig I-15. Exemple de circuit de division polynomiale                                            | 39 |

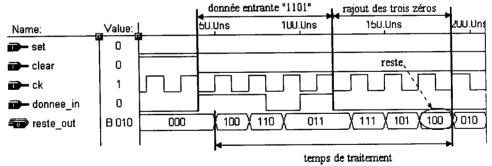

| Fig I-16. Exemple de simulation d'un diviseur $(g(x) = 1+x+x^3)$                                | 39 |

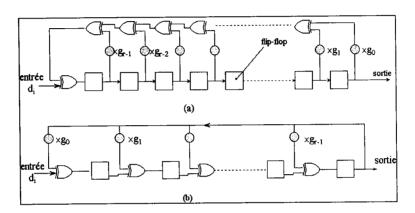

| Fig I-17. Circuit modifié pour le calcul du reste                                               | 40 |

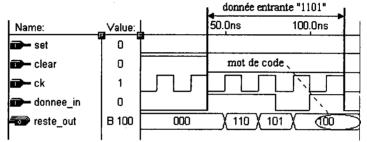

| Fig I-18. Exemple de simulation d'un diviseur du second type $(g(x) = 1+x+x^3)$                 | 40 |

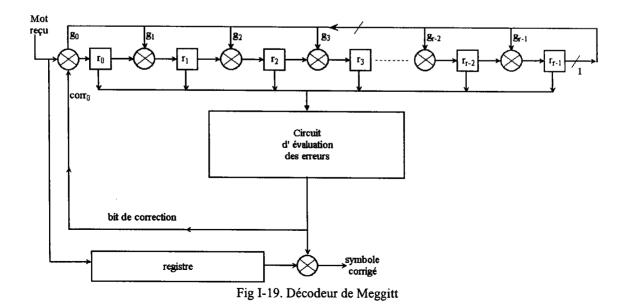

| Fig I-19. Décodeur de Meggitt                                                                   | 42 |

| Fig I-20. Exemple d'applications de codes correcteurs d'erreurs                                 | 44 |

| Tableau 3. Liste des premiers codes DSCC                                                        | 49 |

| Fig II-1. Exemple d'implantation du décodeur DSCC (21,11)                                       | 50 |

| Tableau 4. Liste des racines de $\delta$ et de H                                                | 55 |

| Fig II-2. Construction de la matrice orthogonale à la position $\alpha^{14}$                    | 55 |

| Fig II-3. Matrice de décodage du code DTI (5,3).                                                | 56 |

| Fig II-4. Représentation de GF(2 <sup>4</sup> ) en fonction des éléments de GF(2 <sup>2</sup> ) | 59 |

| Fig II-5. Vecteur d'incidence des lignes passant par $\alpha^{14}$ dans EG (2,4)                | 60 |

| Fig II-6. Calcul des poids W <sub>2</sub> <sup>2</sup> des nombres de 1 à 15                    | 62 |

| Fig II-7. Architecture série du codeur                                                          | 64 |

| Fig II-8. Exemple formel d'une division polynomiale                                             | 65 |

| Fig II-9. Circuit d'implantation de la formule (2.11)                                           | 65 |

| Fig II-10. Cellule de base de l'architecture systolique                                         | 66 |

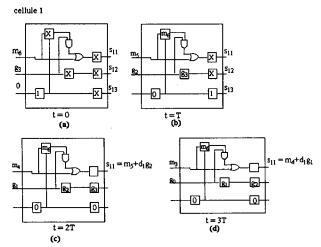

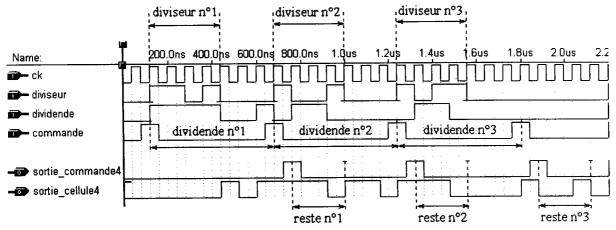

| Fig II-11. Fonctionnement de la première cellule du diviseur systolique                         | 67 |

| Fig II-12. Fonctionnement de la deuxième cellule                                                | 67 |

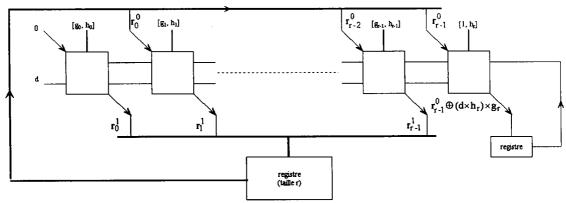

| Fig II-13. Exemple de diviseur systolique ( $k = 7$ , $r = 3$ )                                 | 68 |

| Fig II-14. Exemple de simulation d'un diviseur systolique ( $k = 7$ , $r = 3$ )                 | 68 |

|                                                                                                 |    |

Recherche des performances dans la mise en œuvre des codes linéaires cycliques en ASIC à haut débit

| l'ableau 5. comparaison des surfaces des architectures série et systolique                       | 69         |

|--------------------------------------------------------------------------------------------------|------------|

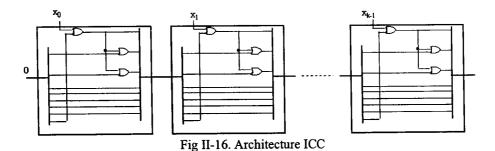

| Fig II-15. Cellule de base de l'architecture ICC pour le polynôme $1+x+x^2+x^8$                  | 70         |

| Fig II-16. Architecture ICC                                                                      | 70         |

| Tableau 6. Performances des architectures séries et ICC                                          | <b>7</b> 1 |

| Fig II-17. Principe de l'architecture parallèle                                                  | <b>7</b> 1 |

| Tableau 7. Surface d'un diviseur parallèle                                                       | 72         |

| Tableau 8. Débit et temps de calcul du reste pour un diviseur parallèle                          | 72         |

| Fig II-18 Schéma d'implantation d'un multiplieur/diviseur polynomial                             | 73         |

| Tableau 9. Caractéristiques des architectures étudiées.                                          | 74         |

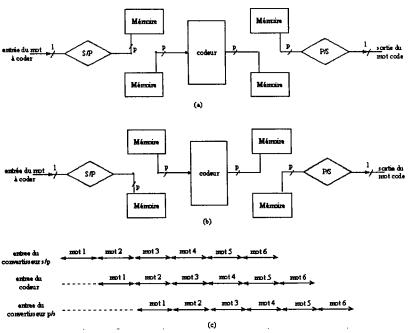

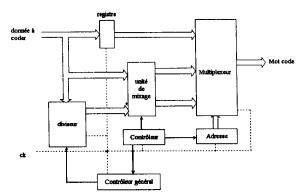

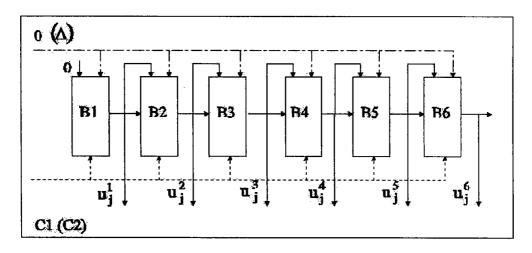

| Fig II-19. Principe de fonctionnement du circuit de codage                                       | 75         |

| Fig II-20. Architecture générale du circuit de codage.                                           | 77         |

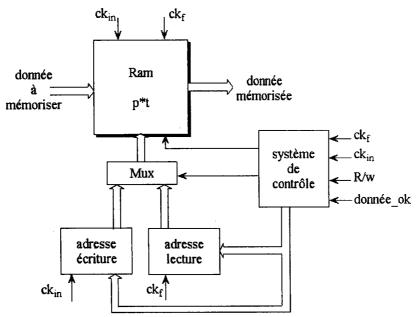

| Fig II-21. Schéma de principe d'un système utilisant des RAM.                                    | 78         |

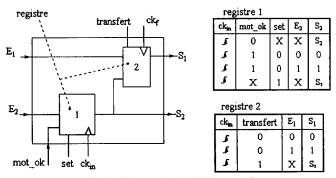

| Fig II-22. Cellule de base de la FIFO asynchrone                                                 | 79         |

| Fig II-23. Registre à décalage pour la FIFO asynchrone                                           | 80         |

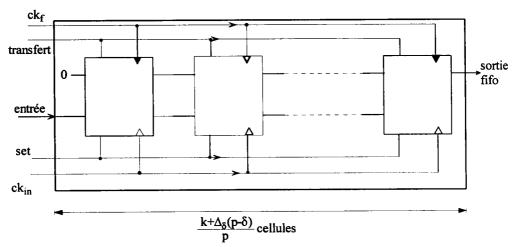

| Fig II-24. Schéma de la mémoire utilisée dans le circuit de codage.                              | 81         |

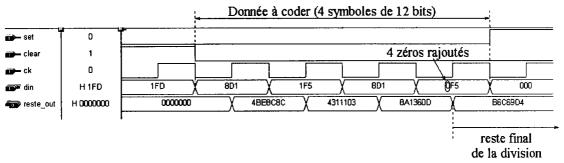

| Fig II-25. Simulation d'une mémoire pour le codeur DSCC(72,44) (p = 12)                          | 81         |

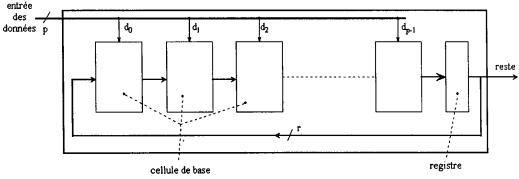

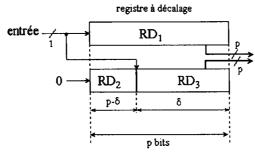

| Fig II-26. Schéma de principe de la conversion série/parallèle                                   | 82         |

| Fig II-27. Architecture du circuit de conversion série-parallèle                                 | 83         |

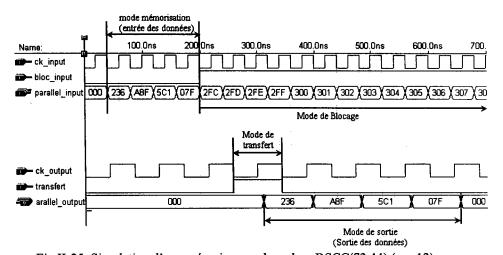

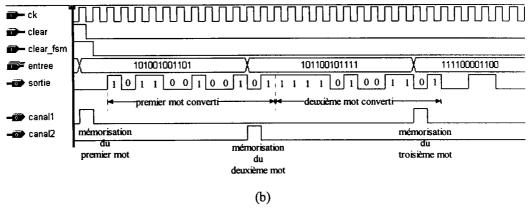

| Fig II-28. Simulation du circuit de conversion (code $DSCC(72,44) - p = 3$ )                     | 83         |

| Fig II-29. Architecture et simulation du convertisseur série/parallèle                           | 84         |

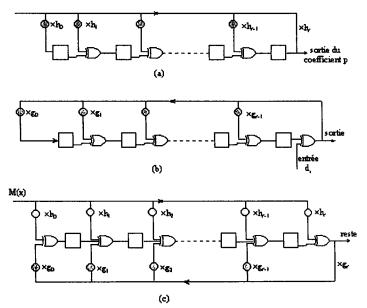

| Fig II-30. Schéma de principe du codeur parallèle                                                | 85         |

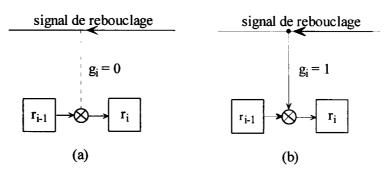

| Fig II- 31. Cellule de base du diviseur série                                                    | 86         |

| Fig II-32. Implantation du circuit série de division                                             | 86         |

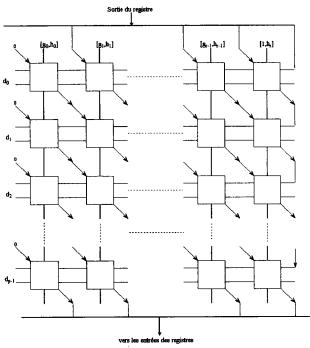

| Fig II-33. Architecture du diviseur parallèle de type 2.                                         | 87         |

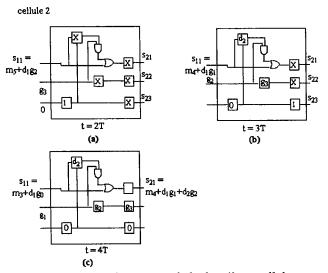

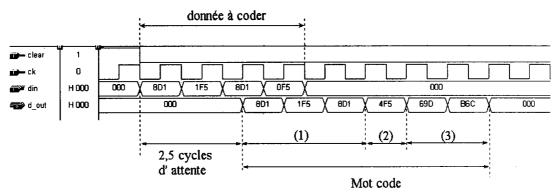

| Fig II-34. Exemple de simulation du diviseur pour le code DSCC(42,44) avec un parallélisme de 12 | 88         |

| Fig II-35. Circuit de mise en forme du mot code                                                  | 89         |

| Fig II-36. Schéma du cœur du codeur                                                              | 89         |

| Fig II-37. Exemple de simulation du cœur du codeur pour le code DSCC (72,44)                     | 90         |

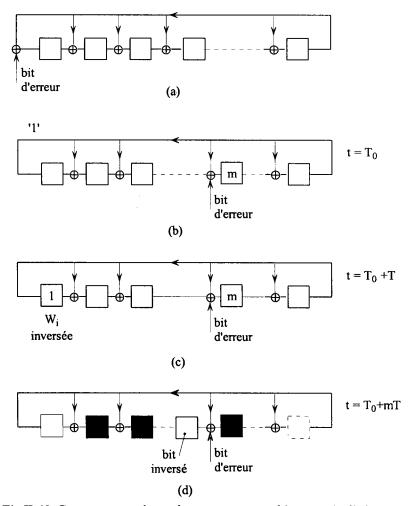

| Fig II-38. Circuit conventionnel d'un décodeur à logique majoritaire                             | 91         |

| Fig II-39. Organisation temporelle du décodeur pipeliné                                          | 92         |

| Fig II-40. Comportement du syndrome avec une architecture pipelinée                              | 93         |

| Fig II-41. Conditions utilisées dans l'architecture pipeline du décodeur à logique majoritaire   | 94         |

| Fig II-42. Caractéristiques du décodeur pipeline pour le code DSCC(1075,813)                     | 95         |

| Fig II-43. Architecture implantant la détection des erreurs                                      | 96         |

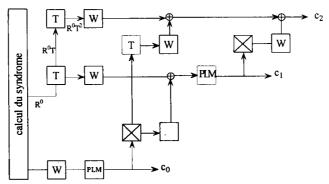

| Fig II-44. Nouvelle architecture du décodeur                                                     | 97         |

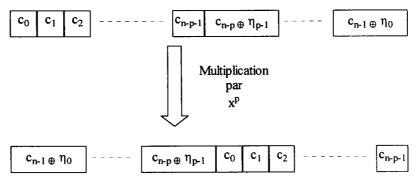

| Fig II-45. Effet de la multiplication par x <sup>p</sup> sur le mot de code                      | 98         |

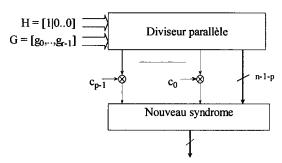

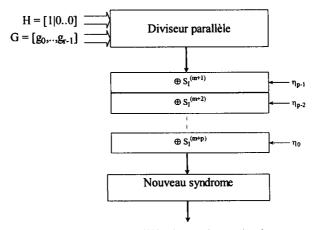

| Fig II-46. Architecture parallèle pour le calcul du nouveau syndrome                             | 99         |

| Fig II-47. Calculateur parallèle du syndrome (code raccourci)                                    | 100        |

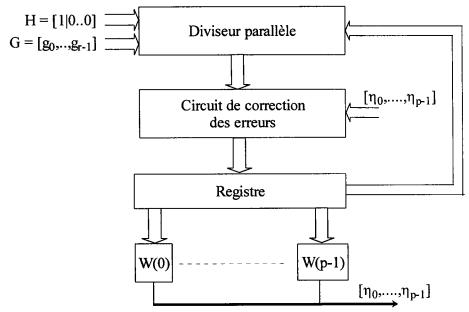

| Fig II-48. Structure du circuit de décodage parallèle                                            | 101        |

| Fig II-49. Caractéristiques des différentes architectures                                        | 102        |

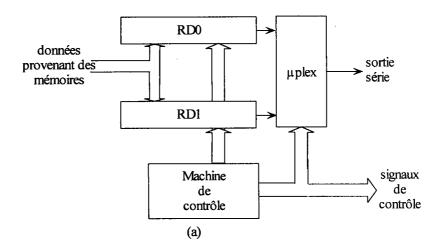

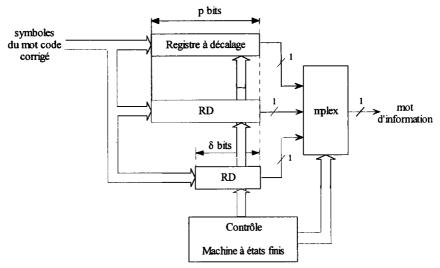

| Fig II-50. Schéma de principe du décodeur parallèle                                       | 103 |

|-------------------------------------------------------------------------------------------|-----|

| Fig II-51. Architecture du convertisseur parallèle/série.                                 | 104 |

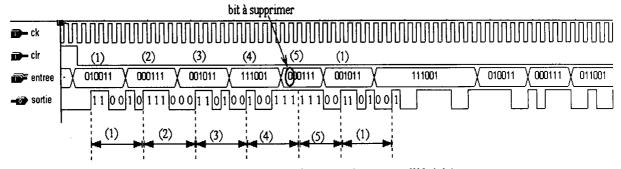

| Fig II-52. Exemple de fonctionnement du convertisseur parallèle/série                     | 104 |

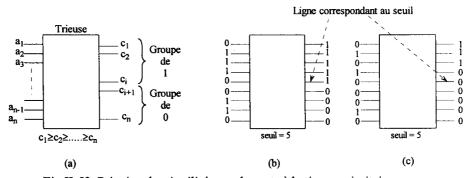

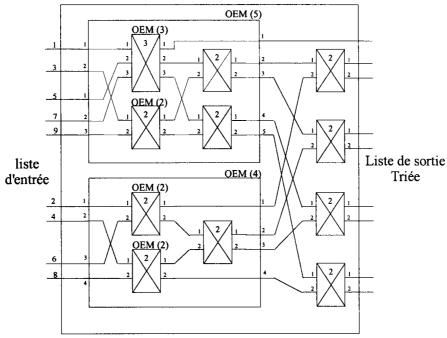

| Fig II-53. Principe du tri utilisé pour la porte à logique majoritaire                    | 106 |

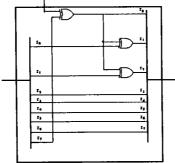

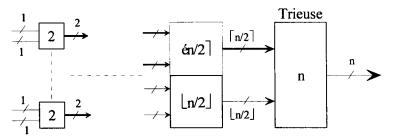

| Fig II-54. Architecture générale d'une trieuse de n lignes                                | 107 |

| Fig II-55. Exemple d'un OEM à 9 éléments                                                  | 108 |

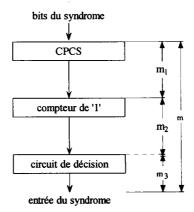

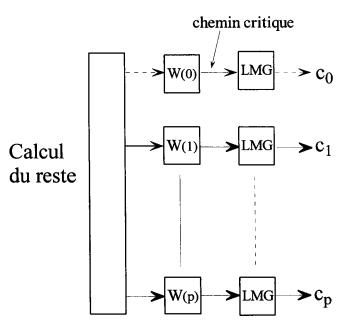

| Fig II-56. Principe du calcul du syndrome                                                 | 109 |

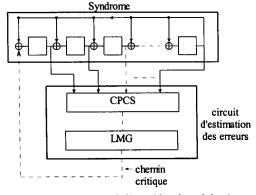

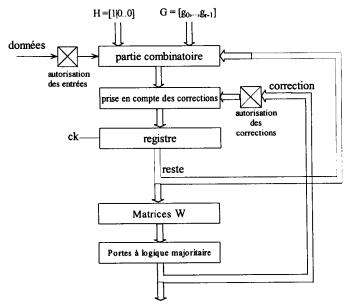

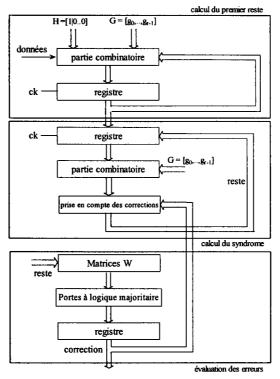

| Fig II-57. Architecture utilisée pour le calcul du syndrome                               | 110 |

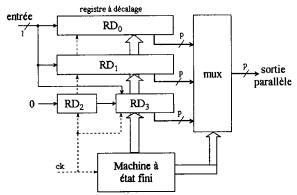

| Fig II-58. Architecture du cœur du décodeur                                               | 111 |

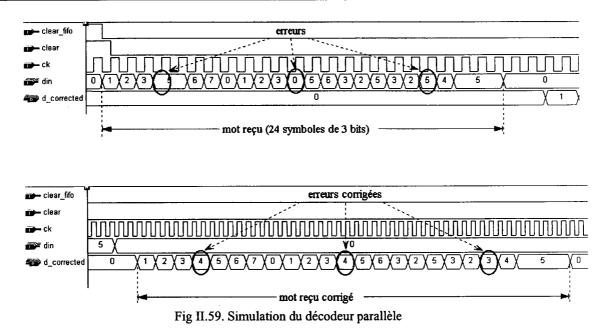

| Fig II.59. Simulation du décodeur parallèle                                               | 112 |

| Fig II-60. Caractéristiques des polynômes utilisés pour l'étude de la surface et du débit | 114 |

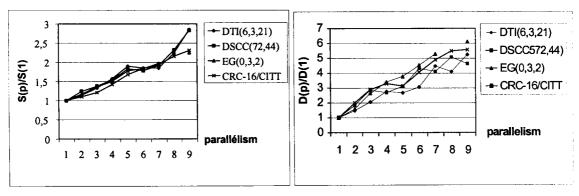

| Fig II-61. Etude du débit (a) et de la surface (b) du diviseur parallèle                  | 114 |

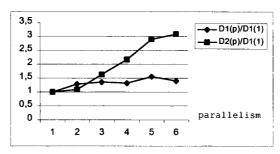

| Fig II-62. Comparaison des deux diviseurs parallèles                                      | 115 |

| Fig II-63. Caractéristiques du codeur parallèle pour le code DSCC (72,44)                 | 116 |

| Fig II-64. Comparaison du débit des deux architectures proposées                          | 118 |

| Fig II-65. Tailles des différentes portes à logique majoritaires                          | 118 |

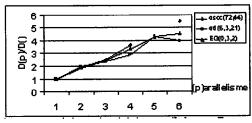

| Fig II-66. Etude du débit (a) et de la surface (b) du décodeur                            | 119 |

| Fig III-1. Algorithme de Berlekamp                                                        | 129 |

| Fig III-2. Algorithme modifié de Berlekamp-Massey                                         | 136 |

| Fig III-3. Principe de Simulation                                                         | 142 |

| Fig III-4. Résultats des simulations.                                                     | 143 |

| Fig III-5. Comparaison des performances.                                                  | 144 |

| Fig III-6. Comparaison avec d'autres codes.                                               | 145 |

| Fig III-7. Principe de Multiplication                                                     | 148 |

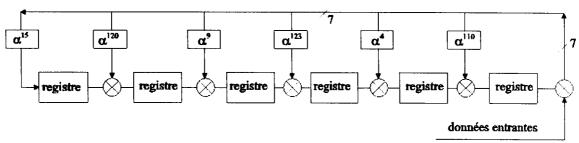

| Fig III-8. Diviseur polynomial du code RS (127,121,7)                                     | 148 |

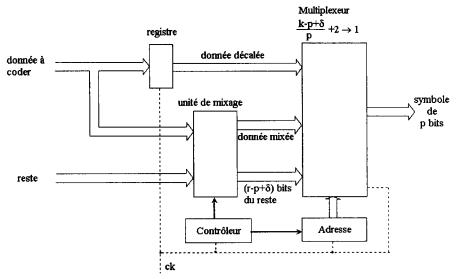

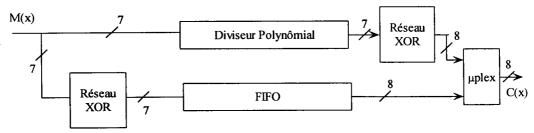

| Fig III-9. Architecture du codeur                                                         | 149 |

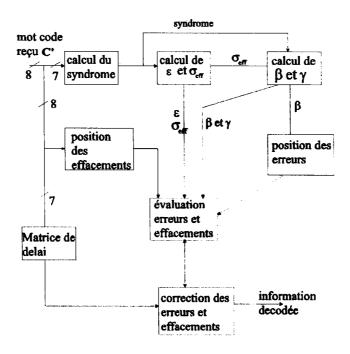

| Fig III-10. Principe de décodage                                                          | 149 |

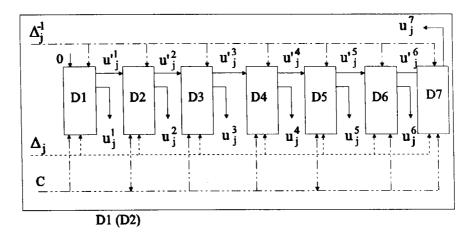

| Fig III-11. Architecture utilisée pour le décodeur du Reed-Solomon (127,k,d).             | 150 |

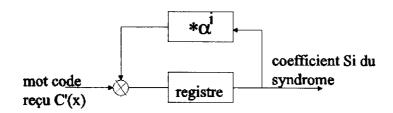

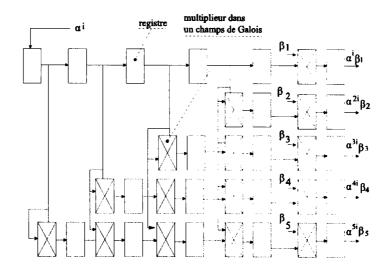

| Fig III-12. Circuit de calcul des coefficients $lpha^i$                                   | 152 |

| Fig III-13. Schéma du système implantant l' équation (3.28)                               | 153 |

| Fig III-14. Schéma du circuit de calcul des polynômes $\epsilon$ et $\sigma_{\text{eff}}$ | 154 |

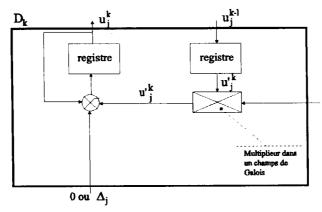

| Fig III-15. Principe du décalage à droite                                                 | 154 |

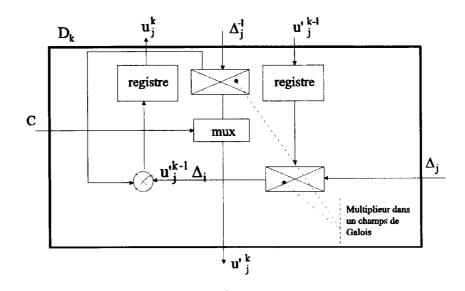

| Fig III-16. Schéma de principe de D <sub>k</sub>                                          | 155 |

| Fig III-17. Circuit utilisé pour le calcul des polynômes $\beta$ et $\gamma$ .            | 155 |

| Fig III-18. Circuit d'évaluation de $\beta(\alpha^{-i})$                                  | 150 |

|                                                                                           |     |

# **Bibliographie**

- [1] M.S. Hodgart, « Efficient coding and error monitoring for spacecraft digital memory » Int. J. Electronics, 1992, Vol 73, n°1, pp 1-36

- [2] Bruce Schneier,« Applied cryptography, protocols, algorithms and source code in C » John Wiley & Sons, 1994

- [3] Florent Chabaud, « Recherche de performance dans l'algorithmique des corps finis, application à la cryptographie », Thèse de l'école Polytechnique, Paris, 1996

- [4] M. Nicolaidis, Y.Zorian, «On line testing for VLSI- A compendium of approches», Journal of electronic testing- theory and application, vol 12n n°1/2, February-April 1998, pp 7-20

- [5] » A. Paschalis & all, « Efficient design of totally self checking checker-decoders for all cyclic AN codes, IOLTW'99, Rhodes

- [6] T.C. Dietterich, G. Bakiri, « Solving multiclass learning problems via error correcting output code », , Journal of artificial intelligence research, 1995, n°2, pp 263, 286

- [7] Osamu Yamada & al,1 « Error correction system for a difference set cyclic code in a teletext system », brevet n° 4,675,868 ; juin 1987

- [8] Osamu Yamada, « FM Multiplex Broadcasting », NHK laboratories Notes, vol 372, 1989

- [9] Delahaye J.P, « A difference-set cyclic code(1057,813,34) ». Annals of Telecommunications 51 n°1-2,1996

- [10] T. Vallino, S. Piestrak, A. Dandache, F. Monteiro, B. Lepley, « Study of a new parallel architecture dedicated to the family of the DSCC codes »

5rd IEEE International On-Line Testing Workshop, Rhodes, Greece, July 5-7 1999

[11] A. Dandache, T. Vallino, F. Monteiro, J.P. Delahaye, « Code Reed Solomon (127,k,d) avec effacements: simulation et conception sur FPGA »

Traitement du Signal, Vol 16, n°4, 1999

[12] J.G. Remy, J. Cueugniet, C. Siben, «Système de radiocommunication avec les mobiles»,

Eyrolles, collection C.N.E.T-E.N.S.T, 1988

[13] Shu Lin, D. J. Costello Jr, « Error control coding : Fundamentals and applications », Prentice Hall 1983

[14] C. R. Hawthorne & all, « An Error-Correction Scheme for a helical-scan magnetic data storage system »

IEEE journal on selected areas in communications vol 10, n°1, 1992

[15] M. D. Rice and S. B. Wicker , « Modified majority logic decoding of cyclic codes in hybrid-ARQ systems »

IEEE Trans. Commun, vol. 40, pp. 1413--1417, Sep. 1992

[16] G. Battail, « Théorie de l'information : Application aux techniques de communication » Edition Masson, 1997

[17] A. Poli, Li. Huguet, « codes correcteurs, théorie et applications »

Collection Masson, 1989

[18] A Donnedu, Cours de mathématiques (volume 1 et 2), édition Vuibert

[19] Alexandru Spataru, « Théorie de la transmission vol II : codes et décision » Edition Masson, 1973 [21] G. Cohen, J.L. Dornstetter, P. Godlewski, «Codes correcteurs d'erreurs: une introduction au codage algébrique », collection C.N.E.T/ ENST; Edition Masson 1992

[22] Leonard D. Baumert, « cyclic difference sets »

Lecture notes in Mathematics, vol 182, Springer-Verlag, 1971

[23] J. Singer, « A theorem in finite projective geometry and some applications to number theory », AMS Trans, 43, 1938.

[24] E.J. Weldon Jr, « Difference set cyclic codes », The Bell System Technical Journal, September 1966

[25] T. Kasami, L. Lin, W.W Peterson, « Some results on cyclic codes which are invariant under the affine group and their applications », Inf. control, 2, pp 475-496, 1968.

[26] C. R. P. Hartmann & all, « On the structure of generalized finite geometry code », IEEE trans on information theory, IT-20(2) Mars 1974.

[27] Michael Braun & all, « Parallel CRC computation in FPGA », Rapport de laboratoire, Université de Saarlands

[28] Beniamino Castagnolo, Maria Rizzi, «High Speed Error correction circuit based on iterative cells », Int. J. Electronics. 1993, Vol 14 n°4, pp 529-540

[29] Kobayashi & all, « New LSI Architecture for ultra High Speed Error correction an it's application to the majority decoding LSI for (1057,83) code », Nhk laboratories Notes, 1992

[30]. Kobayashi & all, « 50 Mhz CMOS pipelined majority logic decoder », IEICE trans. Fundamentals, vol E79-a, n°7, juillet 1993

[31] K.E. Batcher, « Sorting Networks and their applications », proc 1968, SJCC AFIPS vol 32, 1968, pp 307-314

- [32] Stanislaw J. Piestrak, «The minimal test set for multioutput threshold circuits implemented as sorting networks », IEEE trans on computers vol 42 n°6 juin 1993

- [33] Tong Bi Pey and Charles Zukowski, «High Speed Parallel CRC», IEEE trans on communication vol 40 n°4, 1992

- [34] « CRC MegaCore function » Altera Datasheet, ver 2A-DS-CRC-02, April 1999

- [35] R. Blahut, «Transform techniques for error control code», IBM J of Research and Development, 23, 1979, pp 299-315

- [36] J.L. Dornstetter, « On the equivalence between Berlekamp's and euclid's theorem » IEEE Trans on Inf Theory, vol IT-33 May 1987, pp428-431

- [37] « Reed-Solomon decoder with erasures », Société Hammer Core (mars 1999)

- [38] « AHA 4011. 10 Mbytes/sec Reed-Solomon Error correction device », Product Specification, Advanced Hardware Architectures

- [39] K. Matsushima & all, « Parallel encoder and decoder architecture for cyclic codes », IEICE trans on fundamentals, vol E79-A, n°9, sept 1996

- [40] C. Paar, « A New architecture for parallel finite field multiplier with low complexity based on composite field », IEEE trans on computers July 1996, vol 45, n°7, pp 1313-1323

# Introduction

Ces dernières années ont vu l'émergence de réseaux de communications aussi divers que la téléphonie mobile, internet, intranet. Elle s'est accompagnée d'un accroissement des applications dédiées (visioconférence par exemple). Cependant ces diverses applications n'utilisent plus un seul support de transmission dédié, mais tout un panel de médias (voie hertzienne, câble, satellite, etc). Aussi, différents protocoles sont ou ont été à l'étude pour faciliter la transmission à travers ces supports (recommandation DAVIC, norme MNSC). Cependant ceux-ci doivent utiliser des fonctions de traitement des données de plus en plus complexes. Parallèlement, le volume des données à transmettre s'accroît. Par conséquent le risque d'erreur augmente. Il est alors nécessaire d'assurer la sûreté des données de plus en plus rapidement. Pour cela diverses techniques peuvent être utilisées :

- implantation software: le problème majeur consiste à implanter des algorithmes efficaces en temps de cycles de calculs (par exemple l'utilisation de masques est souvent nécessaire pour implanter un XOR entre deux bits sur un DSP). Cependant, cette technique est très souple et permet de reconfigurer « rapidement » son système.

- implantation hardware: elle permet de réaliser et d'implanter des fonctions complexes fonctionnant à des débits relativement élevés. En contrepartie cette méthode

n'offre pas la souplesse d'une architecture software (cependant, il existe des FPGA pouvant se reprogrammer in situ).

Une des fonctions complexes (telles que la compression de données, le modulateur, le démodulateur, le codage de canal, etc) à implanter pour la transmission de donnée est d'assurer la sûreté des messages envoyés. En effet, les médias utilisés pour transporter les données ne sont pas parfaits et sont le siège de perturbations pouvant corrompre les messages transmis. L'impact des erreurs va alors être aggravé par l'augmentation du débit et de la quantité de données. Pour faire une comparaison, une erreur de un bit a un impact plus important dans un fichier compressé que dans un fichier non compressé.

Il va alors être nécessaire de contrôler les erreurs afin de permettre une restitution aussi fidèle que possible du message émis et à un débit de plus en plus important. Plusieurs méthodes ont été développées afin de détecter/corriger les erreurs [13]:

- Transmission avec requête (ARQ): On rajoute des symboles de parité pour effectuer une détection d'erreur. Si une erreur est détectée, on demande une retransmission,

- Transmission utilisant des codes correcteurs d'erreurs : cette fois ci la redondance est calculée selon une loi qui permet la détection et la correction des erreurs,

- Transmission hybride : cette méthode utilise conjointement le système ARQ et les codes correcteurs d'erreurs

Les méthodes ARQ et ARQ-hybride peuvent être utilisées respectivement pour des applications à faible et moyen débit à cause de la retransmission [13]. Par contre, les codes correcteurs d'erreurs peuvent être utilisés pour des applications à haut débit [13]. Le dialogue entre la source et le destinataire n'existe plus, ce qui est nécessaire pour certaines applications (vérification des mémoires dans une navette spatiale par exemple [1]) [Il est à noter que les codes correcteurs ne sont pas limités à cet usage et sont aussi

utilisés dans d'autres domaines tels que la cryptographie [2], [3], le test en ligne [4],[5] ou l'intelligence artificielle [6]

De ces trois méthodes, la plus adaptée aux hauts débits consiste donc en l'utilisation des codes correcteurs. Les premières implantations des codes correcteurs ont été logicielle et arrivent à la limite de leur performance. Il est donc nécessaire de développer et d'implanter des architectures matérielles spécifiques aux codes correcteurs et dédiées à des applications à haut débit. Plusieurs architectures peuvent être mises en concurrence :

- L'architecture série: première architecture utilisée pour les codes linéaires cycliques, son avantage est qu'elle est simple à implanter (XOR et flip-flop uniquement) mais lente et ne permet pas de traiter des données en continu [17].

- L'architecture systolique: Les opérations se font toujours en série, mais en pipeline. Lorsque le débit augmente, cette architecture n'est pas capable de traiter un flot continu de données [17].

- L'architecture parallèle: C'est une généralisation de l'architecture série. Elle permet des débits plus importants que les deux précédentes et peut traiter un flot continu de données. On doit alors tenir compte d'une nouvelle contrainte: La surface du codeur/décodeur parallèle [10].

Notre travail porte essentiellement sur l'étude des performances des codes correcteurs d'erreurs notamment, les codes linéaires cycliques.

Le chapitre 2 présente l'étude de l'impact du parallélisme sur la surface pour un code particulier : le code DSCC (Difference Set Cyclic Code). Ce code est un code linéaire cyclique utilisé par la télévision japonaise NHK pour sécuriser le transport de données [7], [8]. Ce code a aussi été étudié à TDF-C2R [9] et intégré dans un simulateur de code correcteur de la même société. Les résultats de l'étude ayant été concluants [10], elle a

été étendue à la famille des codes cycliques à décodage à logique majoritaire à laquelle le code DSCC appartient.

Le troisième chapitre porte sur un autre problème des codes correcteurs qui consiste à réduire le coût de la transmission. Effectivement, plus le nombre d'erreurs s'accroît, plus le nombre de symboles de redondance à utiliser augmente, ce qui a pour conséquence une utilisation plus importante de la bande passante. Cependant, certains codes (Reed-Solomon) permettent, grâce à l'utilisation de nouveaux algorithmes (code de Reed-Solomon avec effacement), une augmentation de la capacité de correction (i.e. le nombre maximum d'erreurs pouvant être corrigé) sans accroître le coût de la transmission. Par contre, cette augmentation peut se faire au détriment de la surface du codeur utilisé et du débit. Dans la plupart des applications industrielles [37] [38] implantant le code de Reed-Solomon avec effacements, la détection des effacements (qui permet d'augmenter la capacité de correction) n'est pas réalisée. Le Reed-Solomon est (comme les codes à logiques majoritaires) un code linéaire cyclique. Mais, alors que les codes à logiques majoritaires sont des codes binaires (l'information est soit un 1 soit un 0), les codes de Reed-Solomon travaillent sur des symboles de plusieurs bits. Cet emploi de symboles au lieu d'un simple bit entraîne un système de correction complexe. L'étude que nous avons effectuée ne concerne alors pas l'amélioration de l'architecture du système de correction (amélioration de l'architecture) mais uniquement l'étude de l'implantation sur FPGA de la détection des effacements pour un code de Reed-Solomon. Une technique de marquage permettant d'implanter les effacements (méthode qui accroît la capacité de correction sans trop augmenter la redondance) a été développée en collaboration avec TDF-C2R, simulée puis synthétisée sur FPGA afin de valider le concept.

# Chapitre I. Les codes correcteurs

Ce premier chapitre est consacré à une présentation générale des codes correcteurs. La partie I.1. pose le problème des transmissions et du stockage des données et présente différentes solutions possibles avec leurs avantages et inconvénients. Les parties I.2. et I.3. sont une description générale de deux familles de codes correcteurs d'erreurs : les codes linéaires et les codes linéaires cycliques.

## I.1. Généralités

# I.1.1. Position du problème

Dans la société actuelle, que ce soit dans la vie quotidienne ou professionnelle, l'information peut être considérée comme une richesse à deux points de vue :

- Au niveau d'une application, c'est l'information qui constitue réellement la richesse du système. Par exemple lors du transfert de données entre deux banques, c'est l'information qui est primordiale et non son transport (même si celui ci est important).

- A un deuxième niveau, les infrastructures et services offerts pour transporter cette information constitue eux aussi une richesse (boom des téléphones portables par exemple, télévision « pay per view »).

Cependant, d'un point de vue très général, toutes ces applications ont le même but : mettre en relation (conversation, échange de données) deux points quelconques (personnes, application, matériel) via des supports de transmission très divers (voies hertzienne, câble, fibres optiques). L'augmentation des transferts d'informations (prises au sens large) peut alors être limitée par les caractéristiques physiques des supports de transmission. Par exemple dans le cas de la télévision « pay per view », on doit transmettre N programmes là où avant on ne transmettait qu'un seul programme (limitation du spectre en fréquence pour une application). Il sera alors nécessaire d'avoir un débit plus important pour transmettre les données.

Des techniques particulières ont été mises au point pour utiliser au mieux le spectre en fréquence disponible. On peut citer par exemple le multiplexage en fréquence ou le multiplexage temporel. Ces deux techniques se focalisent sur l'encombrement spectral et l'utilisation optimum des fréquences allouées à une application.

Parallèlement, on peut diminuer le volume des données à transmettre (optimisation du coût de transmission) grâce à l'emploi d'un codage adéquat (codage de source) [16].

| Type de bruit | Remarques diverses                                                                                   |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Galactique    | Bruit prépondérant pour une fréquence comprise entre 20 MHz et 200MHz Négligeable au-delà de 300 MHz |  |  |  |  |

| Atmosphérique | Prépondérant jusqu'à 20 MHz<br>Essentiellement dû aux éclairs lors des orages                        |  |  |  |  |

| Industriel    | Lignes de transports d'énergies Dispositifs de chauffage à induction,                                |  |  |  |  |

| Urbain        | Enseignes lumineuses Dispositif d'allumage des véhicules                                             |  |  |  |  |

| Brouillage    | Diaphonie<br>Intermodulation entre émetteurs                                                         |  |  |  |  |

Tableau 1. Types de bruits pouvant intervenir dans une transmission.

Toutefois, la transmission entre un émetteur A et un récepteur B peut être considérée comme imparfaite (le tableau 1 donne un aperçu des différents types de bruit pouvant intervenir pendant une transmission de données [12]). Comme le débit des données à

transmettre augmente, le risque d'erreur devient de plus en plus important. Par exemple, dans le cas d'une application pour laquelle un codage de source est employé, une « petite » erreur pendant la transmission peut transformer une partie importante du message originel (ce qui pour un transfert entre banques est catastrophique). Le récepteur B doit donc posséder un moyen de vérifier le message reçu, c'est à dire pouvoir détecter/corriger les éventuelles erreurs entachant ce message. La méthode employée dépend alors de l'application visée et du type de bruit perturbant la transmission.

# I.1.2. Solutions possibles pour la détection et la correction des erreurs

Une des techniques parmi tant d'autres pour minimiser l'impact des erreurs dues au canal de transmission consiste à rajouter de la redondance (symboles quelconques) au message à transmettre. Cependant si on minimise l'effet des erreurs éventuelles, le récepteur ne peut toujours pas les détecter. Aussi au lieu de rajouter des symboles quelconques, rajoute-t-on des symboles qui dépendent de l'information suivant une loi connue à la fois de l'émetteur et du récepteur. Celle ci dépend alors de l'application choisie et du type de bruit présent sur le canal de transmission. Suivant la loi utilisée, différentes stratégies sont possibles.

## I.1.2.1. Systèmes avec ARQ (Automatic Repeat reQuest).

Les systèmes avec ARQ [13] utilise une loi ajoutant des symboles de parité. Cette loi permet de détecter la présence d'erreurs mais le récepteur ne peut ni localiser ni corriger les éventuelles erreurs. Dans le cas d'un message considéré comme erroné, le récepteur émet une requête demandant la réémission de ce message. On parle alors de codes détecteurs d'erreurs avec ARQ. Trois implantations de base du système ARQ existent :

- « Stop and Wait ARQ »

- « Go back N ARQ »

## • « Selective repeat ARQ »

Dans le cas du système « Stop and Wait ARQ », l'émetteur attend que le récepteur lui envoie un signal pour continuer l'émission des données. Le récepteur ne peut envoyer que deux valeurs ACK ou NAK. La réception du signal ACK indique que la transmission s'est bien déroulée et l'émetteur peut envoyer le message suivant. Dans le cas contraire (NAK), des erreurs ont perturbé la transmission et l'émetteur doit de nouveau envoyer la donnée précédente. La figure I-1 montre un exemple de déroulement d'une session « Stop and Wait ARQ »

Fig I-1. Exemple de fonctionnement d'un système « Stop and Wait ARQ ».

Dans le cas du système « Go back N ARQ », l'émetteur envoie de façon continue les messages sans s'occuper du récepteur. Le premier signal d'accusé de réception arrive après N cycles de transmission (N dépendant de l'application). Si cet accusé indique qu'il n'y a aucune erreur, l'émetteur continue sa transmission. Dans le cas contraire, l'émetteur émet le mot erroné et les N mots suivants (voir figure I-2). Ce système est plus intéressant que le système « Stop and Wait ARQ » mais n'est pas valable pour des débits importants à cause du nombre important de messages non erronés qui sont retransmis dans le cas d'une erreur sur un seul message.

Fig I-2. Exemple d'un système Go back 7 ARQ

Pour le système « Selective repeat ARQ », la procédure utilisée est similaire à celle du système « Go back N ARQ » mais il n'y a retransmission que du message erroné (figure I-3). Cela implique l'utilisation d'une mémoire au niveau du récepteur afin de remettre en ordre les données reçues.

Fig I-3. Exemple de fonctionnement d'un système « selective repeat ARQ »

Les systèmes de décodage utilisés par ces techniques sont simples à implanter. De plus, ces systèmes sont adaptatifs dans le sens où il n'y a retransmission que dans le cas où une erreur se produit. Cependant, ils présentent deux inconvénients majeurs qui interdisent l'utilisation de l'ARQ pour des applications ayant des flots continus de données :

- Le débit utile décroît rapidement quand le nombre d'erreurs augmente.

- Il est nécessaire d'utiliser un canal bidirectionnel ou deux canaux de transmission pour assurer le dialogue émetteur/récepteur, chose qui n'est pas possible dans toutes les applications [14], [15].

La méthode décrite dans le paragraphe suivant permet de s'affranchir d'un dialogue entre l'émetteur et le récepteur et est utilisée pour des systèmes de communication à une voie de transmission. Ce sont les codes correcteurs d'erreurs (Forward Error Correction).

<sup>22</sup> Recherche des performances dans la mise en œuvre des codes linéaires cycliques en ASIC à haut débit

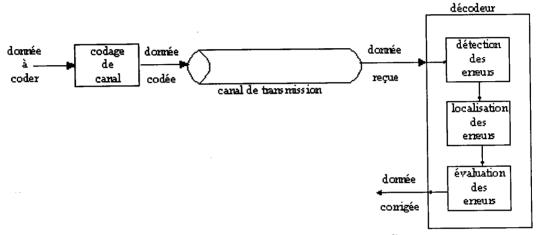

# I.1.2.2.Codes correcteurs d'erreurs

Pour les codes correcteurs d'erreurs, la redondance suit une loi mathématique qui permet à la fois la détection, la localisation et la correction des erreurs (codage de canal). Le décodage demande alors plus d'opérations (localisation et correction) que dans les cas précédents. L'implantation du décodeur sera alors plus ou moins difficile selon le code utilisé (la figure I-4 donne le schéma général d'une transmission avec un code correcteur).

Fig I-4. Exemple d'utilisation d'un code correcteur d'erreur

Comme il ne peut y avoir de retransmission des données erronées, le code correcteur utilisé pour une application doit pouvoir détecter et corriger les erreurs les plus vraisemblables statistiquement (taux de couvertures). Il est alors nécessaire de connaître le type d'erreurs (isolée ou en paquet) et leur fréquence d'apparition. Plusieurs modèles de canaux de transmissions (modèles de Pareto, de Neymann-Pearson, de Markov [16]) ont été développés. Ils sont utiles pour faire des simulations nécessaires au choix d'un code approprié à une application [projet européen RACE]. Par exemple, le modèle de Pareto a été utilisé pour modéliser l'intervalle entre deux erreurs consécutives et des tests de comparaison ont été effectués en RFA par IBM et les PTT. Ces tests ont permis de montrer que ce modèle est valable pour des intervalles courts [17]

L'avantage des codes correcteurs est qu'ils permettent un débit utile constant (égal à k/n avec k et n respectivement la taille de la donnée avant codage et la taille après codage). Par contre, pour corriger un nombre important d'erreur, il est nécessaire d'utiliser des codes dont le paramètre n est grand avec des conséquences sur :

- le temps de traitement,

- le débit (pour un k donné, le débit utile chute avec n),

- la surface utilisée pour implanter le décodeur.

De plus si le nombre d'erreurs dans le mot reçu est supérieur à la capacité de correction du code utilisé, le mot en sortie du décodeur est mal décodé. La fausse correction devient alors une source d'erreurs.

Ce dernier inconvénient peut être supprimé si on utilise conjointement un code correcteur d'erreurs et un système ARQ. On parle alors « d'ARO hybride ».

## I.1.2.3. Systèmes hybrides

Deux types de système hybride existent. Dans ce paragraphe, nous nous intéresserons au système hybride de type I uniquement. Pour les systèmes de type II, on peut se référer à [13, p 479-497].

Le système hybride de type I consiste à utiliser un code correcteur d'erreur dans un système avec ARQ (qui peut être l'un de ceux du paragraphe A.I.2.1). L'emploi du code correcteur d'erreur permet la détection et la correction d'un certain nombre d'erreurs et diminue la fréquence de retransmission des messages. En effet, si le message reçu peut être corrigé par le code correcteur, il n'y a pas besoin de demander une retransmission. Certains codes correcteurs ont déjà été modifiés pour pouvoir être inclus dans un tel système [15].

Pour des canaux avec un taux d'erreur faible, le système ARQ est plus efficace que le système hybride à cause de son système adaptatif. Par contre, quand le nombre d'erreurs croît, le système hybride devient plus avantageux car il diminue le nombre de retransmission à effectuer [13]. Cependant, ce système ne peut toujours pas être utilisé pour des systèmes à une voie de transmission.

# I.1.3. Conclusions

Le tableau 2 résume les avantages et les inconvénients de chaque méthode.

| Méthode                        | Avantages                                  | Inconvénients  Débit faible  Dialogue émetteur/récepteur |  |  |

|--------------------------------|--------------------------------------------|----------------------------------------------------------|--|--|

| ARQ                            | Simple à implanter                         |                                                          |  |  |

| FEC (forward error correction) | Débit constant<br>Pas de dialogue          | Le mot décodé peut être faux<br>Plus lourd à implanter   |  |  |

| ARQ hybride                    | Moins de retransmission FEC moins puissant | Nécessite un dialogue                                    |  |  |

Tableau 2. Résumé des différentes méthodes de corrections des erreurs

Dans toute cette étude, nous ne nous intéresserons qu'à la deuxième stratégie, celle des codes correcteurs, c'est à dire que nous nous placerons dans le cas d'applications pour lesquelles le dialogue n'est pas autorisé et le débit de sortie doit être constant.

Essentiellement, on peut décomposer les codes correcteurs en deux sous familles principales: les codes convolutifs et les codes linéaires. Ces codes sont utilisés couramment dans l'industrie. Dans le cadre de cette étude, nous nous limiterons à l'étude des codes linéaires et plus particulièrement des codes linéaires cycliques. Pour les codes convolutifs et multivariables, on pourra consulter respectivement les ouvrages [13, pp 257-446] et [18, pp201-317].

# I.2. Les codes linéaires.

# I.2.1. Rappels mathématiques

Dans ce paragraphe, nous allons rappeler quelques définitions de base utiles pour l'étude des codes linéaires et cycliques. Pour de plus amples informations on pourra étudier [19, tome 1 et 2] ou tout autre livre de mathématiques sur les structures fondamentales

## I.2.1.1. Structure de groupe

Un ensemble C muni d'une loi interne × (C, ×) possède une structure de groupe si :

- la loi  $\times$  est associative :  $\forall a,b,c \in C$ ,  $a \times (b \times c) = (a \times b) \times c$ .

- la loi interne possède un élément neutre  $e : \forall a \in C$ ,  $a \times e = e \times a = a$ .

- tout élément de C admet un inverse  $a^{-1}$ :  $a \times a^{-1} = a^{-1} \times a = e$ .

Lorsque la loi est commutative, on dit que C est un groupe commutatif. (On note alors sa loi additivement).

## I.2.1.2. Structure de corps

Soit E un ensemble muni de deux lois de compositions interne (+ et x). On dit que E est un corps si

- (E,+) est un groupe commutatif,

- × est une loi associative,

- × est distributive pour l'addition +,

- × possède un élément neutre,

- Tout élément non nul est inversible.

#### I.2.1.3. Structure d'espace vectoriel

Soit E un ensemble quelconque et K un corps commutatif. On suppose que E est muni d'une loi de composition interne + et d'une loi de composition externe × sur K, c'est a dire:

$$E \times E \rightarrow E$$

:

$K \times E \rightarrow E$ :

$$(a,b) # a+b$$

$(\alpha,a) \# \alpha \times a$

On a alors la définition suivante :

E est un espace vectoriel sur K si

(E,+) est un groupe commutatif

-

$$\forall a,b \in E, \forall \alpha \in K$$

$$\alpha \times (a+b) = \alpha \times a + \alpha \times b$$

-

$$\forall a \in E, \forall \alpha, \beta \in K$$

$(\alpha+\beta) \times a = \alpha \times a + \beta \times a$

$$(\alpha + \beta) \times a = \alpha \times a + \beta \times a$$

-

$$\forall a \in E, \forall \alpha, \beta \in K$$

$\alpha \times (\beta \times a) = (\alpha \times \beta) \times a$

$$\alpha \times (\beta \times a) = (\alpha \times \beta) \times a$$

-

$$\forall a, \in E$$

,

$$1 \times a = a \times 1$$

(Par exemple, pour tout corps commutatif K, l'ensemble K[x] des polynômes à une indéterminée x sur le corps K est un espace vectoriel).

De plus, si l'espace vectoriel est de dimension finie, il est possible de calculer une base de cet espace (c'est à dire un ensemble d'éléments linéairement indépendants). Tout élément de l'espace vectoriel peut alors s'écrire comme une combinaison linéaire des éléments de la base utilisée.

L'utilisation de cette structure et l'existence d'une base va permettre de définir un certain type de codes en blocs : les codes linéaires.

# I.2.2. Les codes linéaires

# I.2.2.1. Codes en blocs

D'après le paradigme de Shannon, tout système de communication peut être schématisé de la façon suivante [16] :

<sup>27</sup> Recherche des performances dans la mise en œuvre des codes linéaires cycliques en ASIC à haut débit

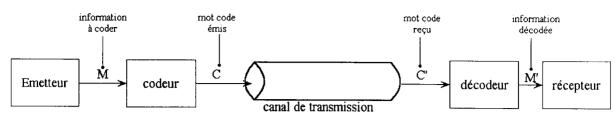

Fig I-5. Représentation générale du système de communication considéré

D'après ce qui a été écrit dans le chapitre précédent, l'émetteur rajoute des symboles à l'information à transmettre (redondance) suivant une loi  $\psi$  connue du récepteur. Le destinataire du message peut alors vérifier si la loi  $\psi$  est respectée. Si cette loi n'est pas respectée, le message reçu contient une ou plusieurs erreurs (détection des erreurs) et le récepteur va tenter de les localiser et les corriger (décodage). Dans le cas contraire, aucune erreur n'a été détectée (il y a toujours la possibilité que les erreurs aient transformé un mot de code en un autre mot de code).

De plus, il est nécessaire que la loi  $\psi$  fasse correspondre à une information un seul mot code.  $\psi$  doit donc être une bijection entre l'espace des mots d'informations et l'espace des mots codes.

Dans le cas particulier du codage binaire par bloc (les symboles appartiennent à l'ensemble  $\{0,1\}$ ), les bits d'informations sont regroupés en blocs de taille fixe k (il y donc  $2^k$  messages distincts possibles). Le codeur transforme (loi  $\psi$ ) alors ces blocs en mot code constitués de n bits. Par conséquent, il y a  $2^k$  mots de code distincts qui correspondent aux  $2^k$  mots d'information ( $\psi$  est une bijection).

A la réception, en observant le mot, le destinataire peut décider s'il y a des erreurs ou non. Si le message n'appartient pas à l'ensemble des mots de codes il y a une erreur. Dans le cas contraire on considère qu'il n'y a pas d'erreurs de transmission (les éventuelles erreurs ne sont pas couvertes par le code utilisé). Pour déterminer si le mot

reçu est un mot de code, le récepteur doit utiliser un dictionnaire (mémoire de 2<sup>k</sup>\*n bits). Pour des valeurs de k et n assez grandes, cette manière de faire devient coûteuse.

La linéarité (i.e.  $\psi$  est une loi linéaire) devient alors une structure souhaitable pour un code en bloc car elle permet de réduire la complexité du codage et du décodage.

# I.2.2.2. Code linéaire, Matrice génératrice, Matrice de contrôle

On définit un code linéaire C(n,k) par [17]:

Soit  $V = \{(v_1, v_2, ... v_n) / v_i \in \{0,1\}\}$ . Un code en bloc de longueur n constitué de  $2^k$  mot code distincts C(n,k) est dit linéaire si et seulement si les  $2^k$  mot de codes forment un sous espace vectoriel de V de dimension k

D'après le paragraphe I.2.1.3., il existe une base dans cet espace. Comme la dimension de l'espace vectoriel est k, il existe k vecteurs indépendants. On peut donc utiliser ces vecteurs pour former une base de l'espace vectoriel. On va noter  $g_i$  le i<sup>ème</sup> vecteur de la base.

D'après la définition d'une base d'un espace vectoriel de dimension finie, tout élément de C peut s'écrire comme une combinaison linéaire des vecteurs de la base considérée. Par conséquent, l'ensemble C peut s'écrire :

$$C = \{u \in V \mid u = a.G, a = (a_1, a_2, ..., a_k) \in \{0,1\}^k\} \quad (1.1)$$

où G est une matrice  $k \times n$  dont les lignes sont les vecteurs  $g_i$  de la base de C. La matrice G est alors appelée matrice génératrice de C

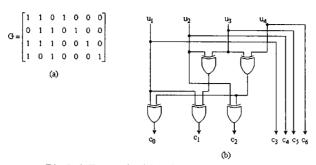

Le circuit de codage peut être constitué d'un circuit mémorisant les k lignes de la matrice G. le codage consiste alors à additionner (modulo 2) les différentes lignes de la base selon le mot « u » à coder. La figure I-6 (b) est un exemple d'implantation d'un codeur dont la matrice génératrice est représentée à la figure I-6 (a).

<sup>29</sup> Recherche des performances dans la mise en œuvre des codes linéaires cycliques en ASIC à haut débit