## Vérification des contraintes temporelles de bout-en-bout dans le contexte AutoSar

Aurélien Monot

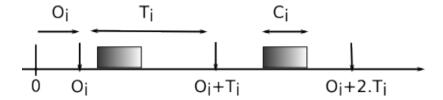

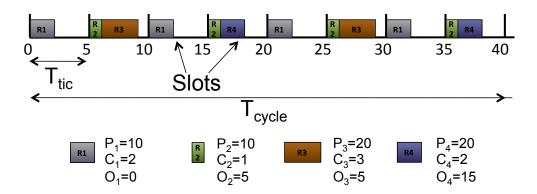

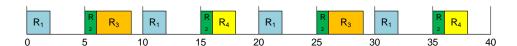

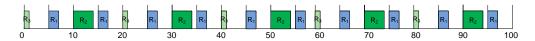

#### ▶ To cite this version:

Aurélien Monot. Vérification des contraintes temporelles de bout-en-bout dans le contexte AutoSar. Autre [cs.OH]. Université de Lorraine, 2012. Français. NNT: 2012LORR0384. tel-01749592v1

## HAL Id: tel-01749592 https://hal.univ-lorraine.fr/tel-01749592v1

Submitted on 29 Mar 2018 (v1), last revised 30 Dec 2012 (v3)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

#### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

## ÉCOLE DOCTORALE IAEM

Département de formation doctorale en informatique

## Vérification des contraintes temporelles de bout-en-bout dans le contexte AutoSar

## THÈSE

présentée et soutenue publiquement le 29 novembre 2012

pour l'obtention du

Doctorat de l'Université de Lorraine (spécialité informatique)

par

### Aurélien MONOT

Thèse dirigée par Françoise SIMONOT et Nicolas NAVET préparée au LORIA, Projet TRIO

Jury:

Invit'e:

Président : Jean Charles FABRE - Professeur à l'INP-Toulouse

Rapporteurs: Laurent GEORGE - Maître de conférence à l'Université de Paris Est

Alain GIRAULT - Directeur de recherche à l'INRIA Rhône-Alpes

Autres membres : Nicolas NAVET - Assistant Professeur à l'Université du Luxembourg

Françoise SIMONOT - Professeur à l'Université de Lorraine

Pierre Étienne MOREAU - Professeur à l'Université de Lorraine

Pierre-Étienne MOREAU - Professeur à l'Université de Lorraine Bernard BAVOUX - Expert en systèmes électroniques

chez PSA Peugeot Citroën

## Remerciements

Cette thèse doit beaucoup aux nombreuses personnes qui m'ont encouragé, soutenu et conforté tout au long de ces années de thèse. Qu'elles trouvent dans ce travail l'expression de mes plus sincères remerciements.

En premier lieu, je souhaite remercier Françoise Simonot eu égard à son rôle de directrice de thèse, pour avoir toujours su se rendre disponible malgré un emploi du temps fort chargé et pour m'avoir prodigué de précieux conseils tout au long de ces travaux. Je lui suis très reconnaissant de la confiance qu'elle m'a accordée quand elle m'a proposé ce projet de thèse Cifre et pour son rôle à la fin de la thèse où elle a su trouver les mots pour m'encourager dans les moments difficiles de la rédaction.

Pour leur encadrement remarquable, j'aimerai remercier très chaleureusement mes deux autres co-encadrants de thèse, Nicolas Navet et Bernard Bavoux qui ont partagé ma garde respectivement à Nancy et à Vélizy tout au long des travaux de thèse. J'ai trouvé chez eux deux beaucoup d'enthousiasme et de gentillesse à mon égard ce qui a rendu nos discussions professionnelles et personnelles constructives et très agréables. Nicolas m'a appris beaucoup quant aux qualités d'un chercheur et Bernard a su me guider adroitement dans le monde de l'entreprise en me montrant les méthodes de travail dans un grand groupe et en me dirigeant vers les bons interlocuteurs parmi les nombreux collaborateurs chez PSA Peugeot Citroën.

Un grand merci également à Liliana Cucu-Grosjean, tour-à-tour mon enseignante, ma tutrice de stage, ma collègue de bureau, ma chef d'équipe et mon amie. Son dynamisme, son énergie et sa détermination dans la réalisation de ces projets m'ont poussé à aller de l'avant par émulation.

Je remercie fortement Marie-Françoise Loubressac, Laurence Bénini, Françoise Laurent et Véronique Bawedin qui ont été d'une efficacité et d'une patience modèles dans toutes les démarches liées à l'organisation de mes nombreux déplacements, ma navigation dans les méandres administratives et les petites choses de tous les jours.

Un grand merci aussi à Cristian Maxim pour avoir été particulièrement patient et à l'écoute de mes demandes lors des fastidieuses phases d'expérimentations avec le simulateur CAN et aussi à Rob Davis pour avoir pris le temps de m'écouter et de

me débloquer lors de mes études de simulation et d'analyse pour les réseaux CAN.

Je souhaite remercier mes collègues et amis au LORIA qui ont contribué à la bonne ambiance de l'équipe et du laboratoire : Olivier Bouré, Dorin Maxim, Cristian Maxim, Sylvain Raybaud, Pierre Caserta, Adrien Guénard, Code Lo, Christian Gillot, Bilel Nefzi, Fabrice Vergnaud, Hugo Cruz Sanchez, Luca Santinelli, Patrick Meumeu-Yomsi et Dominique Bertrand. Leur bonne humeur et les instants que nous avons partagés ensembles m'ont apporté beaucoup de joie.

De même, je souhaite remercier mes collègues de PSA Peugeot Citroën: Frédéric Mangonneaux, Vincent De Flaugergues, Matthieu Donain, Cécile Nocquet, Huy Cuong Nguyen, Ahmed Harrar et Didier Jampi. J'ai passé de bons moments en leur compagnie dans les bureaux de PSA Peugeot Citroën à Vélizy.

Merci beaucoup à Alain Girault et Laurent Georges qui m'ont fait l'honneur d'être rapporteurs de ma thèse ainsi qu'à Jean-Charles Fabre pour avoir accepté de présider le jury de thèse. Je remercie aussi chaleureusement Pierre-Etienne Moreau, mon référent interne au LORIA pour avoir accepté de faire parti du jury de thèse et d'apporter un oeil extérieur à l'informatique embarquée.

A Lucien Lecocq, Marie Lepoutre, Sylvain Le Net, Audrey Dot, Alexandre Hucher, Christophe Sigaud, Cyrille Chopelet, Maude Liotard, Charlotte Rosak, Diana Dos Santos, Etienne Friedli, Cédric Favre, Ksenia et Michael Wahler, Lucas Bonfort et ceux qui se reconnaîtront, merci pour les bon moments passés avant et pendant ma thèse, malgré les distances.

Enfin, un grand merci du fond du cœur à ma famille, en particulier à mes parents pour leur soutien infaillible à tous les points de vue pendant toute la durée de mes études culminant avec ce doctorat.

#### Résumé

Les systèmes électroniques embarqués dans les véhicules ont une complexité sans cesse croissante. Cependant, il est crucial d'en maîtriser le comportement temporel afin de garantir la sécurité ainsi que le confort des passagers. La vérification des contraintes temporelles de bout-en-bout est donc un enjeu majeur lors de la conception d'un véhicule. Dans le contexte de l'architecture logicielle AUTOSAR standard dans les véhicules, nous décomposons la vérification d'une contrainte de bout-en-bout en sous-problèmes d'ordonnancement sur les calculateurs et sur les réseaux de communication que nous traitons ensuite séparément.

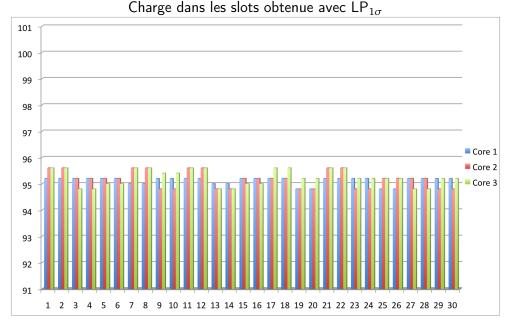

Dans un premier temps, nous présentons une approche permettant d'améliorer l'utilisation des calculateurs exécutant un grand nombre de composants logiciels, compatible avec l'introduction progressive des plateformes multi-coeurs. Nous décrivons des algorithmes rapides et efficaces pour lisser la charge périodique sur les calculateurs multi-coeurs en adaptant puis en améliorant une approche existant pour les bus CAN. Nous donnons également des résultats théoriques sur l'efficacité des algorithmes dans certains cas particuliers. Enfin, nous décrivons les possibilités d'utilisation de ces algorithmes en fonction des autres tâches exécutées sur le calculateur.

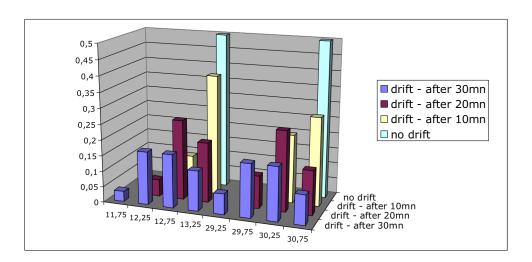

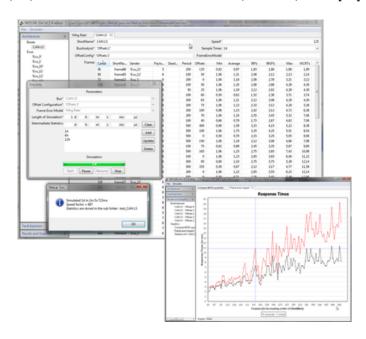

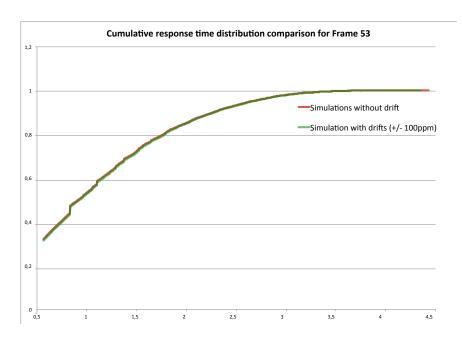

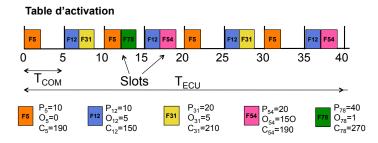

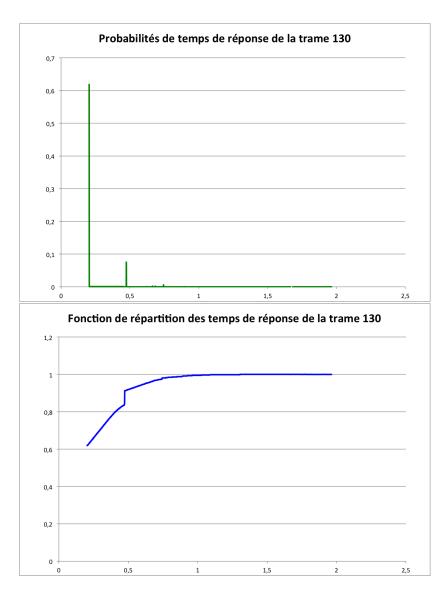

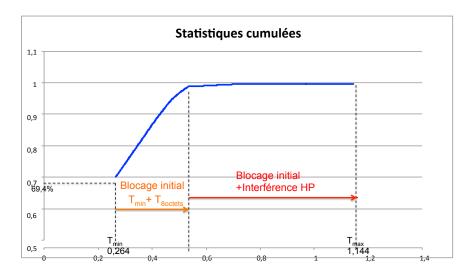

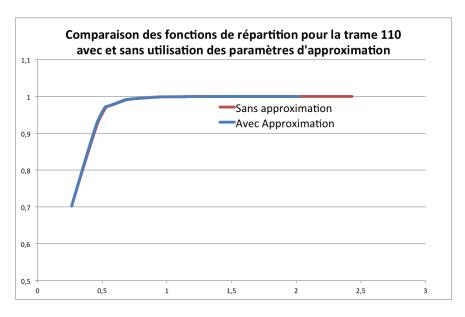

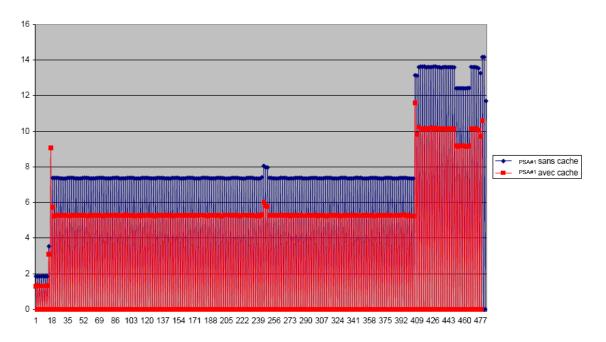

La suite des travaux est consacrée à l'étude des distributions de temps de réponse des messages transmis sur les bus CAN. Dans un premier temps nous présentons une approche de simulation basée sur la modélisation des dérives d'horloges des calculateurs communicant sur le réseau. Nous montrons que nous obtenons des distributions de temps de réponse similaires en réalisant une longue simulation avec des dérives d'horloge ou en faisant un grand nombre de courtes simulations sans dérives d'horloge. Nous présentons enfin une technique analytique pour évaluer les distributions de temps de réponse des trames CAN. Nous présentons différents paramètres d'approximation permettant de réduire le nombre très important de calculs à effectuer en limitant la perte de précision. Enfin, nous comparons expérimentalement les résultats obtenus par analyse et simulation et décrivons les avantages et inconvénients respectifs de ces approches.

Mots-clés: systèmes temps-réel, électronique embarquée, AUTOSAR, ordonnancement, calculateurs multi-cœurs, réseaux CAN, offsets, lissage de charge, distribution de temps de réponse, dérive d'horloge

#### **Abstract**

The complexity of electronic embedded systems in cars is continuously growing. Hence, mastering the temporal behavior of such systems is paramount in order to ensure the safety and comfort of the passengers. As a consequence, the verification of end-to-end real-time constraints is a major challenge during the design phase of a car. The AUTOSAR software architecture drives us to address the verification of end-to-end real-time constraints as two independent scheduling problems respectively for electronic control units and communication buses.

First, we introduce an approach, which optimizes the utilization of controllers scheduling numerous software components that is compatible with the upcoming multicore architectures. We describe fast and efficient algorithms in order to balance the periodic load over time on multicore controllers by adapting and improving an existing approach used for the CAN networks. We provide theoretical result on the efficiency of the algorithms in some specific cases. Moreover, we describe how to use these algorithms in conjunction with other tasks scheduled on the controller.

The remaining part of this research work addresses the problem of obtaining the response time distributions of the messages sent on a CAN network. First, we present a simulation approach based on the modelisation of clock drifts on the communicating nodes connected on the CAN network. We show that we obtain similar results with a single simulation using our approach in comparison with the legacy approach consisting in numerous short simulation runs without clock drifts. Then, we present an analytical approach in order to compute the response time distributions of the CAN frames. We introduce several approximation parameters to cope with the very high computational complexity of this approach while limiting the loss of accuracy. Finally, we compare experimentally the simulation and analytical approaches in order to discuss the relative advantages of each of the two approaches.

**Key-words:** real-time embedded systems, AUTOSAR, scheduling, multicore controllers, CAN network, offsets, load balancing, response time distribution, clock drift

# Table des matières

| 1 | Intro | Introduction                                                |                                                                                                                                                              |                                              |  |  |  |

|---|-------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

|   | 1.1   | Conte                                                       | xte de la thèse                                                                                                                                              | 12                                           |  |  |  |

|   |       | 1.1.1                                                       | Systèmes embarqués dans le domaine automobile                                                                                                                | 12                                           |  |  |  |

|   |       | 1.1.2                                                       | Les grands challenges                                                                                                                                        | 13                                           |  |  |  |

|   |       | 1.1.3                                                       | Normes et standards                                                                                                                                          | 14                                           |  |  |  |

|   | 1.2   | Une a                                                       | pproche système du véhicule                                                                                                                                  | 19                                           |  |  |  |

|   |       | 1.2.1                                                       | Contrainte de temps de bout-en-bout                                                                                                                          | 19                                           |  |  |  |

|   |       | 1.2.2                                                       | Décomposition au niveau fonctionnel                                                                                                                          | 20                                           |  |  |  |

|   |       | 1.2.3                                                       | Architecture opérationnelle                                                                                                                                  | 21                                           |  |  |  |

|   |       | 1.2.4                                                       | Transformation en architecture logicielle AUTOSAR                                                                                                            | 22                                           |  |  |  |

|   |       | 1.2.5                                                       | Partage de ressources et ordonnancement                                                                                                                      | 24                                           |  |  |  |

|   |       | 1.2.6                                                       | Contraintes issues du processus de conception dans l'indus-                                                                                                  |                                              |  |  |  |

|   |       |                                                             | trie automobile                                                                                                                                              | 25                                           |  |  |  |

|   | 1.3   | Vérific                                                     | cation des contraintes de bout-en-bout                                                                                                                       | 27                                           |  |  |  |

|   |       | 1.3.1                                                       | Techniques de vérification temporelle                                                                                                                        | 27                                           |  |  |  |

|   |       | 1.3.2                                                       | Contributions                                                                                                                                                | 28                                           |  |  |  |

|   |       |                                                             |                                                                                                                                                              |                                              |  |  |  |

| 2 | Ord   |                                                             | cement de runnables sur les calculateurs AutoSar                                                                                                             | 31                                           |  |  |  |

|   | 2.1   |                                                             | ption des calculateurs embarqués dans l'automobile                                                                                                           | 33                                           |  |  |  |

|   |       | 2.1.1                                                       | Contexte                                                                                                                                                     |                                              |  |  |  |

|   |       | $^{0.1}$                                                    |                                                                                                                                                              | 33                                           |  |  |  |

|   |       | 2.1.2                                                       | Principaux cas usages des processeurs multi-cœurs                                                                                                            | 33<br>34                                     |  |  |  |

|   |       | 2.1.2                                                       | Travaux existants                                                                                                                                            | 34<br>36                                     |  |  |  |

|   |       |                                                             | · · · · · · · · · · · · · · · · · · ·                                                                                                                        | 34<br>36<br>37                               |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4                                              | Travaux existants                                                                                                                                            | 34<br>36                                     |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4                                              | Travaux existants                                                                                                                                            | 34<br>36<br>37                               |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4<br>Modèl                                     | Travaux existants                                                                                                                                            | 34<br>36<br>37<br>39                         |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4<br>Modèl<br>2.2.1                            | Travaux existants                                                                                                                                            | 34<br>36<br>37<br>39                         |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4<br>Modèl<br>2.2.1<br>2.2.2                   | Travaux existants                                                                                                                                            | 34<br>36<br>37<br>39<br>39<br>40             |  |  |  |

|   | 2.2   | 2.1.3<br>2.1.4<br>Modèl<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Travaux existants  Contributions  e du calculateur  Caractéristiques des runnables  Tâches séquenceurs  Hypothèses de travail                                | 34<br>36<br>37<br>39<br>39<br>40<br>41       |  |  |  |

|   |       | 2.1.3<br>2.1.4<br>Modèl<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Travaux existants  Contributions  e du calculateur  Caractéristiques des runnables  Tâches séquenceurs  Hypothèses de travail  Conditions d'ordonnançabilité | 34<br>36<br>37<br>39<br>39<br>40<br>41<br>42 |  |  |  |

#### Table des matières

|   | 2.4  | Lissage        | e de la charge sur une tâche séquenceur                   | 45<br>45       |

|---|------|----------------|-----------------------------------------------------------|----------------|

|   |      |                | Enoncé du problème                                        | 45<br>46       |

|   |      | 2.4.2          | Algorithme "Least Loaded" dans le cas harmonique          | -              |

|   |      | 2.4.3          | Algorithme "Lowest-Peak" pour le cas non harmonique       | 50             |

|   |      | 2.4.4          | Compléments sur les algorithmes de base                   | 52             |

|   | 2.5  | 2.4.5          | Expérimentations                                          | 54             |

|   | 2.5  |                | e de charge avec plusieurs tâches séquenceurs par cœur    | 56             |

|   |      | 2.5.1<br>2.5.2 | Modèle des tâches                                         | 56             |

|   |      |                |                                                           | 58             |

|   |      | 2.5.3          | Construction des tâches séquenceurs                       | 58             |

|   |      | 2.5.4          | Vérification des contraintes de temps - cas périodique    | 61             |

|   | 0.6  | 2.5.5          | Cas asynchrone                                            | 62             |

|   | 2.6  | Conclu         | sion                                                      | 63             |

| 3 |      |                | des systèmes de communication embarqués dans les vé-      |                |

|   | hicu |                |                                                           | 65             |

|   | 3.1  |                | térêt de la simulation dans la conception des systèmes de | c <del>-</del> |

|   |      |                | unications automobiles                                    | 67             |

|   |      | 3.1.1          | Contexte                                                  | 67             |

|   |      | 3.1.2          | Travaux existants                                         | 68             |

|   |      | 3.1.3          | Pourquoi simuler les dérives d'horloge?                   | 68             |

|   | 2.2  | 3.1.4          | Contributions                                             | 70             |

|   | 3.2  |                | tion des réseaux CAN avec dérive d'horloge                | 71             |

|   |      | 3.2.1          | Modélisation du réseau CAN                                | 71             |

|   |      | 3.2.2          | Détermination des distributions de temps de réponse       | 74             |

|   |      | 3.2.3          | Outillage logiciel                                        | 74             |

|   | 3.3  |                | du pire cas                                               | 75             |

|   |      | 3.3.1          | Trouver le scénario pire cas                              | 76             |

|   |      | 3.3.2          | Reproduire un scénario pire cas                           | 76             |

|   |      | 3.3.3          | Temps de réponse observé versus scénario pire cas         | 78             |

|   | 3.4  |                | utions de temps de réponses des messages                  | 81             |

|   |      | 3.4.1          | Impact de la durée de simulation                          | 81             |

|   |      |                | Impact des déphasages initiaux entre calculateurs         | 82             |

|   |      | 3.4.3          | Impact de la valeur des dérives                           | 85             |

|   |      | 3.4.4          | Cas avec des bornes de dérives réalistes                  | 86             |

|   |      | 3.4.5          | Comparaison avec l'approche sans dérive d'horloge         | 88             |

|   | 3.5  | Conclu         | sion                                                      | 90             |

| 4 | Éval | uation         | de la distribution de temps de réponse d'une trame CAN    | 93             |

|   | 4.1  | Analys         | e des distributions des temps de réponse des trames CAN   | 95             |

|   |      | <i>I</i> . 1 1 | Objectife des travaux                                     | 05             |

|    |                            | 4.1.2<br>4.1.3 | Travaux existants                                            | 95<br>96 |  |

|----|----------------------------|----------------|--------------------------------------------------------------|----------|--|

|    | 4.2                        |                | e et notations                                               | 96       |  |

|    |                            | 4.2.1          | Modélisation des trames CAN                                  | 96       |  |

|    |                            | 4.2.2<br>4.2.3 | Modélisation de l'activation des trames                      | 97<br>98 |  |

|    |                            | 4.2.3          | Messages caractéristiques                                    | 90       |  |

|    |                            | 4.2.4          | tition des temps de réponse                                  | 101      |  |

|    | 4.3                        | Právici        | on stochastique des distributions des temps de réponse des   | 101      |  |

|    | т.5                        |                |                                                              | 102      |  |

|    |                            | 4.3.1          | Analyse de résultats de simulation : existence de sauts dans | 102      |  |

|    |                            |                | les distributions de temps de réponse                        | 102      |  |

|    |                            | 4.3.2          | Présentation de l'approche                                   | 107      |  |

|    |                            | 4.3.3          | Occupation du bus au moment de l'instantiation d'une tram    |          |  |

|    |                            | 4.3.4          | Interférences locales                                        | 112      |  |

|    |                            | 4.3.5          | Interférences des autres stations                            | 112      |  |

|    |                            | 4.3.6          | Synthèse de l'approche                                       | 116      |  |

|    |                            | 4.3.7          | Paramètres d'approximation                                   | 118      |  |

|    | 4.4                        | Résulta        | its expérimentaux                                            | 120      |  |

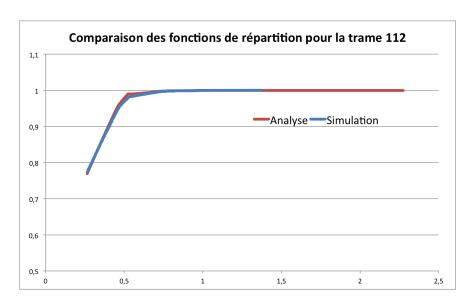

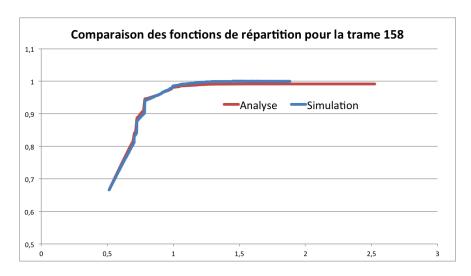

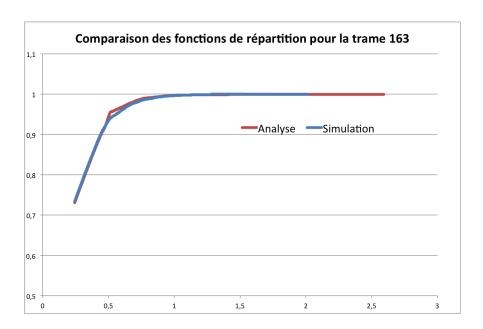

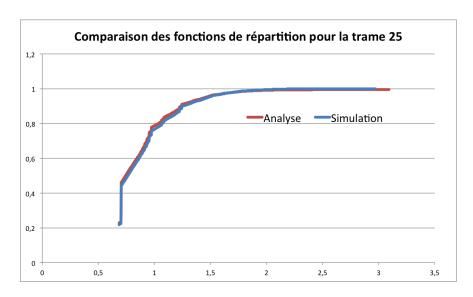

|    |                            | 4.4.1          | Comparaison avec la simulation                               | 120      |  |

|    |                            | 4.4.2          | Impact des paramètres d'approximation                        | 124      |  |

|    |                            | 4.4.3          | Avantages et inconvénients de l'analyse et de la simulation  | 129      |  |

|    | 4.5                        | Conclu         | sion                                                         | 130      |  |

| 5  | Con                        | clusion        |                                                              | 133      |  |

| Ar | nexe                       | es             |                                                              | 138      |  |

| ^  | N 4                        |                | CAN                                                          | 120      |  |

| Α  | ivies                      | sageries       | s CAN utilisées                                              | 139      |  |

| В  | Éval                       | uation         | de l'outil aiT d'AbsInt pour le calcul de WCET               | 143      |  |

| С  | Descriptif des brevets     |                |                                                              |          |  |

| D  | Publications et brevets 18 |                |                                                              |          |  |

# Chapitre 1

# Introduction

| Sommaire |                      |                                                                           |    |

|----------|----------------------|---------------------------------------------------------------------------|----|

| 1.1      | Contexte de la thèse |                                                                           |    |

|          | 1.1.1                | Systèmes embarqués dans le domaine automobile                             | 12 |

|          | 1.1.2                | Les grands challenges                                                     | 13 |

|          | 1.1.3                | Normes et standards                                                       | 14 |

| 1.2      | Une a                | pproche système du véhicule                                               | 19 |

|          | 1.2.1                | Contrainte de temps de bout-en-bout                                       | 19 |

|          | 1.2.2                | Décomposition au niveau fonctionnel                                       | 20 |

|          | 1.2.3                | Architecture opérationnelle                                               | 21 |

|          | 1.2.4                | Transformation en architecture logicielle AUTOSAR                         | 22 |

|          | 1.2.5                | Partage de ressources et ordonnancement                                   | 24 |

|          | 1.2.6                | Contraintes issues du processus de conception dans l'industrie automobile | 25 |

| 1.3      | Vérific              | eation des contraintes de bout-en-bout                                    | 27 |

|          | 1.3.1                | Techniques de vérification temporelle                                     | 27 |

|          | 1.3.2                | Contributions                                                             | 28 |

#### 1.1 Contexte de la thèse

#### 1.1.1 Systèmes embarqués dans le domaine automobile

Depuis l'invention du premier véhicule par Joseph Cugnot en 1769, l'introduction de l'électronique dans les véhicules fait incontestablement partie des ruptures technologiques majeures dans l'histoire automobile. La première utilisation d'un système embarqué dans une voiture afin de commander le système d'injection de carburant en 1967 marque le début d'une nouvelle ère dans l'industrie automobile. Progressivement, de nouvelles fonctionnalités reposant sur l'électronique ont été intégrées dans les véhicules afin de remplacer, assister ou piloter des systèmes mécaniques ou hydrauliques. L'arrivée de composants électronique embarqués dans les voitures a permis progressivement de rendre les véhicules plus sûrs (ABS, ESP), plus efficaces (contrôle de l'injection, véhicules hybrides), et plus confortables (climatisation automatique, lève-vitre, régulateur de vitesse, GPS). La voiture, une invention thermique et mécanique, est devenue à présent un vrai ordinateur sur roues dont la puissance de calcul dépasse par plusieurs ordres de magnitude celle du système de guidage utilisé par la NASA lors de la mission Apollo sur la Lune.

Naturellement, l'intégration des systèmes embarqués dans les voitures s'est faite progressivement. Ainsi, aux débuts de l'électronique embarquée dans les véhicules, chaque calculateur électronique était dédié à une fonction et chaque calculateur était produit par une seule entité, que ce soit le constructeur automobile ou un fournisseur. Ensuite, avec l'émergence de nouvelles fonctions pilotées par électronique, certains calculateurs se sont vus en charge de l'exécution de plusieurs de ces fonctions afin d'éviter la prolifération de calculateurs dans les véhicules. Dans un premier temps, la conception entière de chaque calculateur était encore réalisée par le constructeur ou par un équipementier. Cependant, avec la multiplication de nouvelles fonctions reposant sur l'électronique embarquée, ce modèle a dû évoluer de manière à pouvoir intégrer au sein d'un même calculateur des fonctions réalisées par plusieurs partenaires distincts. Un grand nombre de ces fonctions requiert la mise-en-oeuvre de sous-modules répartis sur plusieurs calculateurs qui doivent alors communiquer entre eux. Afin de limiter le nombre de connexions filaires point à point entre les calculateurs et les capteurs, les automobiles intègrent des systèmes de communications multiplexés qui permettent à un ensemble de calculateurs de s'échanger des messages via un bus commun. Avec le temps, l'architecture électronique des voitures est ainsi devenue très complexe et nécessite la collaboration d'un grand nombre de partenaires différents afin de concevoir et réaliser le matériel et les composants logiciels nécessaires au bon fonctionnement de l'ensemble.

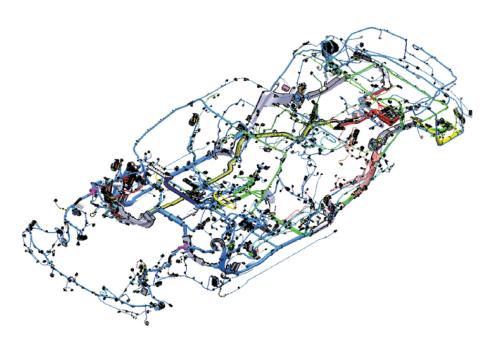

L'électronique embarquée est un enjeu majeur dans l'industrie automobile. De nos jours, une voiture sortant d'usine comporte plusieurs dizaines de calculateurs, appelés "Electronic Control Unit" (ECU), distribués dans tout le volume du véhicule et communicants entre eux via plusieurs bus de communication de type CAN

Figure 1.1 – Schéma du câblage électronique dans une BMW série 7 [25]

(Controller Area Network). D'autres protocoles de communication sont parfois utilisés dans les véhicules comme par exemple : LIN une alternative bas-coût à CAN, FlexRay dans certains véhicules haut de gamme ou MOST pour des applications multimédia. Cependant, les réseaux CAN sont prédominants dans les architectures électroniques des véhicules avec 750 millions de calculateurs capable de communiquer sur CAN vendus en 2010. La figure 1.1 montre le schéma d'implantation des faisceaux électroniques dans un véhicule haut de gamme. On estime que 40% du coût de production d'un véhicule est lié aux composants matériels électroniques et aux composants logiciels. De plus, 90% des innovations faites dans le domaine automobile reposent sur l'électronique embarquée. Dans cette mesure, les constructeurs automobiles mettent beaucoup d'effort à maîtriser la complexité de l'architecture électronique de leur voiture afin de garantir son bon fonctionnement ainsi qu'à l'optimiser et la simplifier afin de réduire les coûts de production.

#### 1.1.2 Les grands challenges

Le nombre de composants électroniques embarqués dans les voitures de nos jours soulèvent ainsi quelques grands défis pour les constructeurs automobiles :

l'inter-opérabilité entre les composants électroniques. Le problème se pose entre autre sur les plans logiciels et matériels ainsi que pour l'adéquation entre logiciel et matériel. Un des problèmes importants est l'inter-opérabilité entre

- composants logiciels provenant de différentes sources mais c'est précisément pour cela qu'AUTOSAR (présenté en 1.1.3) est en train d'être déployé.

- la sûreté fonctionnelle des composants électroniques. Il s'agit d'un problème compliqué au regard de la complexité des systèmes utilisés. En particulier, il peut être difficile d'évaluer la sûreté de fonctionnement d'un calculateur ayant une architecture matérielle moderne et un nombre très importants de composants logiciels multi-sources. C'est pour répondre à ce défi que l'ISO 26262 a été définie.

- l'optimisation. Il s'agit d'un challenge qui intervient à différents niveaux d'échelle et à de nombreux composants d'un véhicule. L'enjeu principal derrière le souci d'optimisation est la réduction des coûts. Les architectures logicielles et matérielles doivent être dimensionnées au plus juste au moment de la conception car elles impactent des millions de véhicules pour les constructeurs généralistes. Ainsi, il est primordial de pouvoir faire plus avec le même matériel ou alors de pouvoir choisir une plateforme avec moins de mémoire ou un processeur moins cher lorsque les conditions le permettent.

- la vérification des performances temporelles dès les premières phases de conception des fonctions pilotées par les systèmes électroniques. Il est important de maîtriser les temps de réponse des fonctions liées à la sécurité du véhicule mais aussi pour les fonctions de confort pour lesquelles l'agrément de l'utilisateur peut être une source d'avantage concurrentiel. Cela implique d'étudier de nombreux sous-problèmes dans différents domaines que ce soit la traçabilité des exigences temporelles lors de la conception, la prédiction et l'évaluation temporelle des différents composants ou le calcul de temps de réponse dans le cas de ressources partagées.

Ce dernier challenge est transverse aux trois premiers. En effet, l'inter-opérabilité se pose aussi au niveau temporel lorsque plusieurs composants sont associés; certains aspects de sûreté fonctionnelle peuvent reposer sur les performances temporelles de certains composants; l'optimisation et le dimensionnement des composants électroniques nécessitent aussi de pouvoir valider les performances temporelles des systèmes étudiés. Les travaux de cette thèse ont donc pour sujet cette dernière problématique.

#### 1.1.3 Normes et standards

Avec l'importance croissante des systèmes électroniques dans les voitures, diverses initiatives de normalisation et standardisation ont vu le jour. Dans le contexte de cette thèse, il convient en particulier de mentionner la norme ISO26262 [3], le consortium AUTOSAR [1] (AUTomotive Open System ARchitecture) et les projets TIMMO/TIMMO-2-USE. La première est une norme de sûreté de fonctionnement spécifique aux systèmes embarqués dans les voitures. Le second est un partena-

riat entre constructeurs automobiles, équipementiers et autres entreprises spécialisées dans ce domaine visant à établir un standard pour l'architecture logicielle des calculateurs automobiles et leur développement. Enfin, le projet TIMMO et sa seconde itération TIMMO-2-USE [2] abordent des aspects temporels non traités dans AUTOSAR. Les résultats de ces projets seront en parties réutilisées dans les mises-à-jour du standard AUTOSAR.

#### ISO 26262

L'ISO 26262 est l'application spécifique aux véhicules routiers de la norme générique CEI 61508 qui traite de la sécurité fonctionnelle des systèmes électriques et électroniques programmables. Elle définit des niveaux d'intégrité pour les composants des systèmes embarqués dans les véhicules qui prennent en compte, dans l'analyse des risques, aussi bien les aspects quantitatifs que qualitatifs. Ces niveaux d'intégrité, appelés ASIL (Automotive System Integrity Level) sont au nombre de quatre : ASIL A à D, respectivement du plus bas au plus haut niveau de criticité. Il existe également un niveau QM (Quality Management) dans le cas d'un système non influent sur la sécurité. Ces niveaux tiennent en compte la probabilité d'un risque, sa sévérité (gravité des blessures, et sa contrôlabilité par un conducteur moyen. Ces différents niveaux sont associés à différentes exigences de vérification des composants afin d'être certifiés. L'objectif de la norme est de standardiser les pratiques de test et de vérification des composants électroniques dans l'industrie automobile. Le tableau 1.1 donne les niveaux ASIL suivant les valeurs des différents paramètres.

| Sévérité       | Fréquence            | Contrôlabilité (par un conducteur moyen) |                |               |

|----------------|----------------------|------------------------------------------|----------------|---------------|

| Sevente        | par an d'utilisation | Simple (>99%)                            | Normale (>90%) | Incontrôlable |

|                | f < 0,1%             | QM                                       | QM             | QM            |

| Pas de blessés | 0,1% < f < 1%        | QM                                       | QM             | QM            |

| ras de biesses | 1% < f < 10 %        | QM                                       | QM             | ASIL A        |

|                | 10 % < f             | QM                                       | ASIL A         | ASIL B        |

|                | < 0,1%               | QM                                       | QM             | QM            |

| Blessés légers | 0,1% < f < 1%        | QM                                       | QM             | ASIL A        |

| Diesses legers | 1% < f < 10 %        | QM                                       | ASIL A         | ASIL B        |

|                | 10 % < f             | ASIL A                                   | ASIL B         | ASIL C        |

|                | < 0,1%               | QM                                       | QM             | ASIL A        |

| Blessés graves | 0,1% < f < 1%        | QM                                       | ASIL A         | ASIL B        |

| Diesses graves | 1% < f < 10 %        | ASIL A                                   | ASIL B         | ASIL C        |

|                | 10 % < f             | ASIL B                                   | ASIL C         | ASIL D        |

Table 1.1 – Niveaux d'intégrité ASIL

La mise en oeuvre imminente de cette norme entraîne certains choix de conception comme l'isolation de composants logiciels provenant de différentes sources comme nous le verrons dans le chapitre 2.

#### **AUTOSAR**

AUTOSAR [1] est né, entre autres raisons, de la volonté des différents acteurs dans le domaine de l'électronique automobile de faciliter le développement de systèmes intégrant des composants provenant de partenaires différents et de permettre la réutilisation de composants logiciels. Cet effort a donné lieu à la définition d'architectures, de briques de base logicielles et d'interfaces standardisées. Cela permet de garantir l'inter-opérabilité des composants logiciels répondant aux spécifications du standard tout en gardant un aspect concurrentiel sur l'implémentation des différentes briques logicielles. Depuis le début du projet en 2003 jusqu'à présent, le standard a connu plusieurs révisions dont la version le plus récente est la 4.0.3 publiée en janvier 2012.

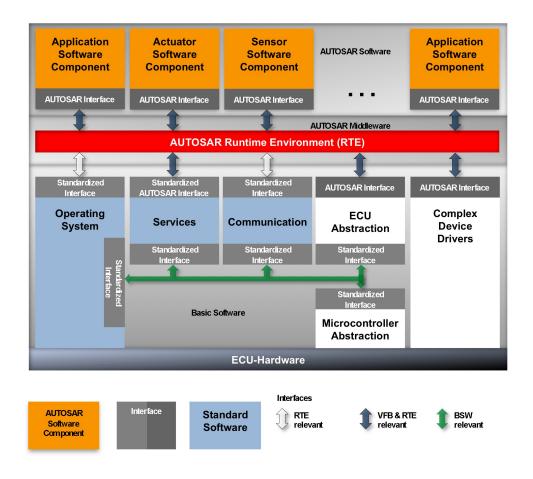

Le standard repose sur une approche d'ingénierie logicielle à base de composants et spécifie une méthodologie à suivre pour concevoir un calculateur conforme au standard. L'architecture logicielle, présentée en figure 1.2 se décompose en trois grandes couches permettant de découpler les aspects fonctionnel et matériel :

- la couche "Basic Software" qui contient l'OS (AUTOSAR OS héritier de OSEK/VDX [60]) et divers services de bas-niveau comme la communication. Certains des composants logiciels de cette couche ("Basic Software Components" ou BSW Components), comme par exemple les drivers, sont dépendants de la plateforme matérielle sur laquelle ils sont exécutés. Cette couche doit donc être développée en accord avec la plateforme d'exécution mais permet précisément aux couches supérieures d'être indépendantes du matériel.

- la couche "Application Software" qui contient le logiciel spécifique aux composants fonctionnels ("Application Software Components" ou ASW Components). C'est ici que se situe le code mettant en oeuvre les fonctions exécutés sur la plateforme. Cette couche est indépendante de la plateforme matérielle sous-jacente.

- la couche "Runtime Environment" (RTE) qui sert à faire communiquer les composants applicatifs (ASW) entre eux ou avec les composants de la couche inférieure (BSW)

La couche RTE sert de tampon entre la couche applicative et indépendante de la plateforme et les services de bas niveau, spécifiques à la plateforme. De ce fait, l'exécution des composants logiciels et applicatifs et l'envoi des messages contenant les données entrantes et sortantes des fonctions distribuées sur un réseau sont indépendants et asynchrones. Cela permet de séparer les problèmes et donc faciliter la conception. En revanche, il n'est pas possible de faire d'hypothèse précise

Figure 1.2 – Architecture logicielle d'un calculateur AUTOSAR. Figure extraite de [1]

sur les délais d'attente pour qu'une information traverse cette couche si ce n'est une hypothèse pire cas pessimiste. Ceci motivera à séparer les travaux de thèse en deux parties : une première s'intéressant aux composants logiciels dans les calculateurs et une seconde s'intéressant aux messages communiqués sur les réseaux.

#### TIMMO et TIMMO-2-USE

Bien qu'AUTOSAR soit utilisé depuis plusieurs années, le standard actuel ne couvre toujours pas l'ensemble des informations et des besoins nécessaires au processus de développement complet d'une automobile. En particulier, la maîtrise des aspects temporels dans le processus de développement sont devenues cruciales pour la conception de systèmes automobiles distribués. Contrairement aux aspects purement fonctionnels et à la fiabilité, les contraintes temporelles sont généralement considérées tard dans le cycle de développement (typiquement lors de l'intégration) et ce, sans qu'il existe une approche standardisée. De plus, le comportement temporel est généralement appréhendé plus sous l'angle de la mesure et du test que des approches formelles et de l'analyse. En conséquence, les fonctions innovantes ne sont pas implémentées, ou ne sont pas implémentées de façon efficace du point de vue de l'optimisation des coûts et des temps de développement.

Plusieurs initiatives ont été lancées pour capturer et modéliser une variété de facettes des architectures électroniques automobiles, on peut citer DECOS, EASIS, StepX, GraForSys, GeneralStore, EAST-ADL2. Néanmoins, le temps n'a jamais été considéré ou il l'a été de façon simplifiée sans considérer les contraintes d'intégration chez les constructeurs de collaboration entre les différents acteurs ou les contraintes liées à la distribution des applications sur les réseaux.

Le standard AUTOSAR est certainement un pas en avant pour gérer la complexité des systèmes automobiles et il a été une première fois étendu dans la dimension temporelle dans sa dernière version (V4.0). Ces extensions ont été élaborées en coopération étroite avec le projet TIMMO qui visait à modéliser et analyser les aspects temporeles dans l'électronique embarquée dans les véhicules.. Suite à ce premier projet, une seconde itération sur ces travaux a été lancée sous la forme du projet TIMMO-2-USE [2] qui vise à améliorer et optimiser les résultats du premier projet en travaillant entre autre à rendre l'approche plus facilement utilisable comme par exemple en renforçant les aspects d'automatisation dans la méthodologie issue de ces travaux.

Les travaux de cette thèse s'inscrivent dans ces efforts pour maîtriser les contraintes temporelles dans le processus de développement des systèmes électroniques embarqués dans le véhicule. Ainsi les approches et algorithmes résultants de cette thèse sont utilisables afin de répondre à certains cas d'usage de TIMMO-2-USE qui couvre un domaine beaucoup plus large. En effet, les aspects méthodologiques, comme par exemple la traçabilité des exigences temporelles d'un niveau de modélisation à un

autre ou la négociation de budget temporels entre les différents intervenants, ne sont pas spécifiquement traités dans cette thèse car cela a déjà été fait dans les projets TIMMO et TIMMO-2-USE.

## 1.2 Une approche système du véhicule

Dans le contexte de cette thèse, nous nous intéressons aux "fonctions pilotées", c'est à dire aux fonctions mises en oeuvre par des composants électroniques embarqués dans la voitures (capteurs, actionneurs, calculateurs et réseaux). Nous étudions en particulier les problématiques de contraintes de temps de bout-en-bout associées à ces fonctions pilotées. Après avoir présenté le concept de contrainte de temps de bout-en-bout, nous détaillons comment cette contrainte se décompose dans le contexte du processus de conception des fonctions pilotées pour finalement s'intéresser à l'ordonnancement des composants logiciels sur les calculateurs et des messages sur les réseaux de communication.

#### 1.2.1 Contrainte de temps de bout-en-bout

La conception d'une fonction pilotée chez un constructeur automobile suit une méthodologie classique de type cycle en V. Ainsi, une des premières étapes consiste à spécifier les besoins. Lors de cette étape, les concepteurs rédigent un document listant un certain nombre d'exigences à réaliser dans différents domaines parmi lesquelles on trouve généralement

- des exigences fonctionnelles, qui expriment ce que réalise la fonction,

- des exigences d'intégration, qui assurent la compatibilité avec l'existant,

- des exigences de sûreté de fonctionnement, qui expriment les besoins de fiabilité, de sécurité et des autres aspects de ce domaine,

- des exigences temporelles, qui expriment les besoins en performances temporelles des fonctions.

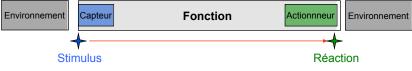

Dans le cadre des travaux de thèse, c'est à ces dernières que nous nous intéressons sous la forme de "contrainte de temps de bout-en-bout". Ici, le terme "de bout-en-bout" exprime que nous nous intéressons à ce qu'il se passe entre le stimulus, qui initie la fonction étudiée, et la réaction, à la fin de l'exécution de la fonction. Ainsi, dans le contexte de l'utilisation d'une voiture, nous étudions ce qu'il se passe temporellement dans l'architecture électronique embarquée dans le véhicule depuis un capteur jusqu'à un actionneur. Ces exigences portent généralement sur des délais de réponse entre le stimulus et la réaction et peuvent se modéliser comme représenté sur la figure 1.3.

Les contraintes de temps de bout-en-bout sont utilisées par le constructeur pour traduire les besoins de performances qui servent en particulier à deux aspects très importants pour les clients : la sécurité et l'agrément des utilisateurs. Pour une

Le délai entre le stimulus et la réaction doit être inférieur ou égale à x ms

Figure 1.3 – Contrainte de temps de bout-en-bout. Le point de départ est situé à l'interface environnement/capteur et le point d'arrivée à l'interface actionneur/environnement.

même fonction sera alors détaillée une liste d'exigences de performances. Voici deux exemples de contraintes de bout-en-bout liées traduisant une exigence de sécurité pour la fonction responsable du freinage du véhicule :

- "Le délai maximum entre une pression sur la pédale de frein et l'allumage des feux stop doit être inférieur ou égal à 50 ms"

- "Le délai maximum entre une pression sur la pédale de frein et l'instant où les plaquettes de frein entrent en contact avec le disque du frein doit être inférieur ou égal à 20 ms"

Les fonctions pilotées sont généralement distribuées, c'est à dire qu'elles mettent en oeuvre plusieurs capteurs, calculateurs et actionneurs répartis dans le véhicule et communiquant entre eux. Comme montré dans l'exemple précédent, les différentes contraintes de temps de bout-en-bout d'une même fonction peuvent être associées à des stimuli et réactions différentes. Ainsi, les flux de donnée correspondant à ces différentes contraintes vont suivre des chemins différents. Dans le contexte de l'étude des contraintes de temps, ces chemins sont appelés "chaînes temporelles". Lors de l'étude de ces contraintes, il faut donc s'intéresser à ces chaînes une par une.

#### 1.2.2 Décomposition au niveau fonctionnel

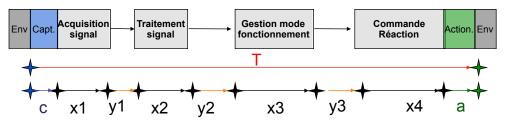

Lors de l'étape suivante du développement d'une fonction pilotée, les concepteurs procèdent au raffinement de la fonction pilotée étudiée en la décomposant en sous-fonctions. Ainsi lors de la phase de conception d'architecture fonctionnelle, la fonction est décomposée jusqu'à obtenir des blocs fonctionnels atomiques. Cette décomposition est finie lorsque les blocs fonctionnels correspondent au niveau de granularité des composants logiciels élémentaires. A ce deuxième niveau de description, il est alors possible de décomposer une contrainte de bout-en-bout en plusieurs sous-contraintes associées à chacun des éléments de la chaîne temporelle. La figure 1.4 montre un exemple de chaîne temporelle une fois la décomposition de l'architecture fonctionnelle réalisée.

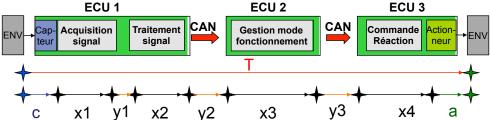

Dans cet exemple, pour une contrainte sur un délai de bout-en-bout de valeur  $\mathsf{T}$ , on a la décomposition suivante en sous-contraintes auxquelles on associe les délais intermédiaires de valeurs suivantes : c pour le capteur,  $x_i$  pour les blocs fonctionnels atomiques,  $y_i$  pour communiquer entre ces blocs et a pour l'actionneur. La contrainte sera respectée si la somme de ces valeurs est inférieure à  $\mathsf{T}$ .

#### Architecture fonctionnelle

Figure 1.4 – Exemple de chaîne temporelle associée à une décomposition fonctionnelle. La chaîne temporelle est décomposée en sous-segment pour chacun des blocs fonctionnels. Pour assurer la cohérence, il faut que  $c+x1+y1+x2+y2+x3+y3+x4+a \le T$

Dans le cas général, les blocs fonctionnels ont plusieurs signaux (données) en entrée et peuvent avoir également plusieurs signaux en sortie. En conséquence, la décomposition strictement fidèle d'une contrainte de bout-en-bout en contraintes intérmédiaires n'est pas nécessairement linéaire comme dans le cas de notre exemple. Dans la pratique, les concepteurs de la fonction étudiée savent identifier un chemin critique lors de la décomposition au niveau fonctionnel. Cette connaissance est nécessaire et utilisée afin d'obtenir une décomposition en contraintes intermédiaires linéaires.

#### 1.2.3 Architecture opérationnelle

De manière courante, la conception de l'architecture matérielle, c'est à dire la liste des calculateurs et leur topologie est réalisée en parallèle du développement de chacune des fonctions pilotées. Ainsi, une fois la phase de conception de l'architecture fonctionnelle réalisée, les concepteurs procèdent à la réalisation de l'architecture opérationnelle qui correspond à l'allocation des blocs fonctionnels sur l'architecture matérielle. Ceci est possible car le niveau de granularité de l'architecture fonctionnelle assure que les sous-fonctions correspondent à des blocs logiciels. En revanche, cela peut nécessiter la définition de nouveaux messages échangés sur les réseaux pour transférer les informations entre les fonctions réparties sur des calculateurs différents.

La figure 1.5 montre la décomposition de la chaîne temporelle étudiée au niveau

de l'architecture opérationnelle. Les différents blocs fonctionnels sont distribués sur trois calculateurs distincts communicant via un bus CAN. De plus, les deux premières sous-fonction de la chaîne sont situés sur le même calculateur. Suivant le fonctionnement des capteurs et des actionneurs, différentes décompositions peuvent être effectuées en ajoutant ou non un délai entre ceux-ci et les sous-blocs fonctionnels qui leur sont connectés. Ici, on considère que le capteur fonctionne de manière synchrone avec le bloc fonctionnel "acquisition signal". En conséquence la décomposition reste la même.

## Architecture opérationnelle

Figure 1.5 – Description de l'exemple de chaîne temporelle étudié au niveau opérationnel lequel fait apparaître l'allocation des composants fonctionnels sur l'architecture matérielle.

#### 1.2.4 Transformation en architecture logicielle AUTOSAR

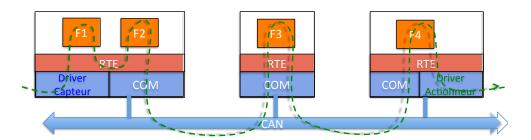

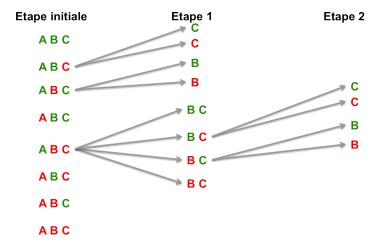

Une fois l'architecture opérationnelle décrite, la transformation pour avoir l'architecture logicielle AUTOSAR est directe. En effet, chaque bloc fonctionnel correspond à un composant logiciel atomique de type "Atomic Software Component" (A-SWC). Ces A-SWC sont mis en oeuvre sous la forme de "runnables" qui sont des composants logiciels élémentaires ayant un flot d'exécution séquentiel. Un A-SWC peut être implémenté par un ensemble de plusieurs runnables mais pour la clareté de l'exemple, nous faisons l'hypothèse que chaque bloc fontionnel ne nécessite qu'un runnable. Si on considère que les runnables F1, F2, F3 et F4 sont les runnables qui mettent en oeuvre les quatre sous-fonctions, la flèche verte en pointillés dans la figure 1.6 montre alors le chemin suivi par le signal dans l'architecture AUTOSAR correspondant à notre exemple.

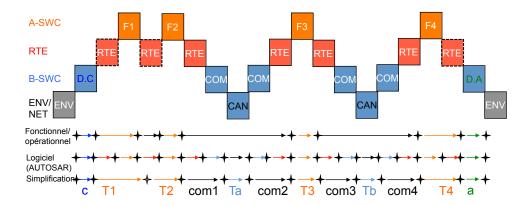

Sur la base de cette architecture, il est alors possible de décomposer encore une fois la chaîne temporelle en segmentant le chemin parcouru par le signal couche par couche comme illustré dans la figure 1.7. Chaque segment correspond au délai entre l'instant ou l'information est transmise par la couche précédente à l'instant ou le signal est transmis à la couche suivante. La vérification de la contrainte de

Figure 1.6 – Description de l'exemple de chaîne temporelle étudié sur une architecture logicielle de type AUTOSAR. La flèche pointillée en vert montre le trajet du signal du capteur à l'actionneur à travers l'architecture logicielle.

bout-en-bout nécessite d'étudier les délais sur chacun des segments. Néanmoins, il est possible de faire quelques simplifications pour certains de ces segments en s'appuyant sur le fonctionnement d'un calculateur. Ainsi, les échanges de données entre composants logiciels situés sur le même calculateur se font généralement sous la forme de variables écrites sur une mémoire partagée dont les accès en lecture et écriture sont fait de manière synchrone lors de l'exécution des runnables correspondants. Dans notre exemple, on peut donc négliger le passage par le RTE entre F1 et F2 c'est à dire l'ancien segment y1. Pour les mêmes raisons, les accès au capteur et à l'actionneur via le RTE sont faits respectivement pendant l'exécution de F1 et F4. Les délais de fonctionnement du capteur et de l'actionneur sont gardés de manière explicite mais pourraient être intégrés aux temps T1 et T4.

Figure 1.7 – Décomposition de la chaîne temporelle étudiée en fonction du parcours à travers les couches de l'architecture AUTOSAR. Les blocs représentés dans cette figure correspondant aux intervalles de temps passés dans chacune des couches et incorporent les éventuels temps d'attente (asynchronismes, ordonnancement...)

Nous avons donc quatre types de segments une fois arrivé à ce niveau de description :

- les délais de fonctionnement des organes physiques (capteurs et actionneurs),

ici c et a.

- les temps de réponse des composants logiciels (les runnables), ici T1, T2, T3 et T4.

- les temps de transition du signal entre la couche applicative et la couche de communication, ici com1, com2, com3 et com4.

- le temps de réponse des messages émis sur les réseaux, ici Ta et Tb.

En ce qui concerne le premier type de segment, les délais de fonctionnement des actionneurs et des capteurs ne seront pas étudiés ici. Il est supposé que ces informations sont obtenues par mesure ou par le fournisseur du composant. Les autres types de segment par contre nécessitent de regarder de plus près ce qu'il se passe au niveau de l'exécution de runnable, ainsi qu'au niveau de la transmission de messages sur les réseaux et enfin aux transitions entre la couche logicielle applicative et la couche responsable de la communication situées de part et d'autre du RTE.

#### 1.2.5 Partage de ressources et ordonnancement

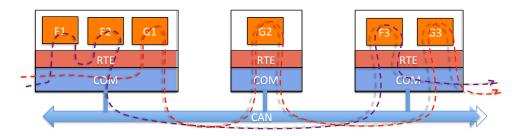

A présent, prenons l'exemple de deux chaînes temporelles correspondant à deux contraintes temporelles de bout-en-bout F et G. Ces deux contraintes pourraient être associées à des fonctions pilotées différentes ou à deux exigences de performance pour une seule fonction pilotée. Ces deux contraintes se décomposent chacune en trois sous-fonctions, respectivement F1, F2, F3 et G1, G2, G3 dont les runnables correspondant sont distribués comme indiqué dans la figure F3, F4, F5, F5,

Si en général, on étudie les fonctions pilotées de manière isolée ainsi que chacune des contraintes temporelles qui leur sont associées, la vérification des propriétés temporelles sur les segments correspondant au niveau applicatif et des segments correspondant à la transmission des messages sur les réseaux requiert d'étudier leur ordonnancement. Sur les calculateurs les plus évolués embarqués dans les véhicules, plusieurs centaines de runnables sont exécutés. De même, plusieurs milliers de signaux sous la forme de centaines de messages sont transmis sur les bus CAN. Ainsi, une fois que l'ensemble des runnables et l'ensemble des messages transmis sur les réseaux sont connus, il devient possible de valider deux autres types de segment.

Figure 1.8 – Exemple de deux chaînes temporelles en concurrence sur des ressources partagées. L'obtention des temps de réponse des segments correspondant au niveau applicatif et des segments correspondant à la transmission des messages nécessite d'utiliser des approches d'ordonnancement.

## 1.2.6 Contraintes issues du processus de conception dans l'industrie automobile

Lors du processus de conception des fonctions pilotées par l'électronique embarquée dans un véhicule, les conceptions de l'architecture matérielle, des messageries réseaux (l'ensemble des paramètres des messages transmis sur les bus CAN) et des différentes fonctions logicielles sont réalisées en parallèle afin de raccourcir le temps de mise sur le marché d'un nouveau véhicule. Cela est rendu possible grâce à une forte réutilisation des composants existants d'une architecture matérielle sur l'autre, ainsi que grâce à l'utilisation de messagerie "souches" (génériques) qui sont ensuite adaptées à chaque configuration véhicule. Dans certains cas, la conception d'une nouvelle fonction peut nécessiter l'introduction d'un nouveau calculateur auquel cas une coopération plus rapprochée est mise en place entre les équipes impliquées. Cependant, dans les cas les plus courants, les concepteurs fonctionnels peuvent s'appuyer sur les composants et l'architecture existants.

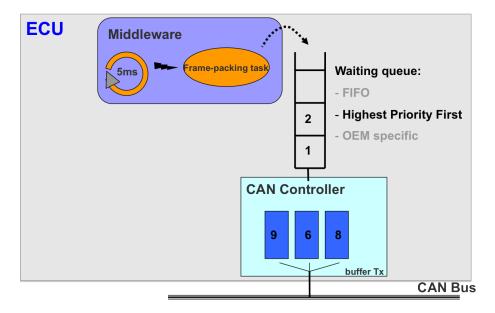

Ce processus de conception est permis grâce à la séparation au niveau logiciel de la couche applicative et des "basic software components" en charge de la communication par la couche RTE. Ces deux niveaux fonctionnent de manière asynchrones ce qui permet de limiter l'impact des évolutions incrémentales qui peuvent être faites sur l'une au l'autre couche. La souplesse ainsi gagnée dans le processus de conception se paie en revanche au niveau des performances, car on ne contrôle pas cette transition. Lors de l'analyse des performances, il est en conséquent difficile de modéliser finement ce qu'il se passe au niveau du dernier type de segment qui fait l'interface entre la couche applicative et la couche responsable de la communication. Il n'est possible que de donner une valeur pire cas pour ces segments. Dans le cas typique d'un comportement périodique de la tâche logicielle responsable de la communication, le délai sera donc au plus égal à la somme de la période de cette tâche et de son temps d'exécution pire cas, cette situation survenant quand

l'information à transmettre est disponible juste après le début de l'exécution de la tâche la consommant.

La décomposition d'une contrainte de bout-en-bout en une chaîne temporelle linéaire est aussi source d'imprécisions. En effet, une description exhaustive des blocs (fonctionnels ou logiciels) nécessiterait de décrire le nombre important de données consommées et produites par chacun de ces blocs. Ainsi, au niveau logiciel, certaines variables partagées peuvent être utilisées par un grand nombre de runnables lors de leur exécution. Dans ces travaux, nous faisons l'hypothèse que les concepteurs sont capables d'identifier un chemin critique de données, entre le capteur et l'actionneur, pertinent pour la contrainte de bout-en-bout considérée. Dans le processus de conception, un grand nombre de variables utilisées pour les calculs mais non présentes sur les chemins étudiées ne sont pas considérées pour la vérification des contraintes temporelles. De fait, certains problèmes de dépendance entre runnables (à cause de variables partagées), de fraîcheur de donnée et de fréquence d'échantillonage ne sont pas couverts dans les travaux de cette thèse.

Une autre cause d'imprécision dans l'étude des contraintes temporelles est le cas des calculateurs de type "boîte noire". En effet, si le constructeur conserve l'exclusivité du développement de certains calculateurs critiques, la plupart des autres calculateurs sont achetés à des fournisseurs qui réaliseront l'intégration. Par exemple, le constructeur conserve généralement la responsabilité du contrôleur habitacle appelé chez PSA "Boîtier de Servitude Intelligent", positionné de manière centrale et responsable de l'exécution d'un grand nombre de tâches en plus de faire passerelle entre les réseaux les plus importants. C'est aussi souvent le cas pour le calculateur en charge du contrôle moteur. En revanche, il est courant pour un constructeur d'acheter les calculateurs multimédia ou responsable de la correction de trajectoire chez un équipementier spécialisé. Il existe également un cas intermédiaire où le constructeur peut demander à un fournisseur d'intégrer des composants logiciels développés en interne auquel cas le constructeur peut avoir une idée plus précise sur le temps d'exécution du code confié au fournisseur. On parle alors de "boîte grise".

L'existence de ces boîtes noires, la conception parallèle et disjointe des applications et des réseaux ainsi que la complexité générale des architectures électroniques interdisent de pouvoir attaquer la vérification des contraintes de bout-en-bout de manière holistique, c'est à dire en considérant le système dans son ensemble. Pour ces raisons, une approche plus raisonnable consiste à décomposer les contraintes de bout-en-bout comme expliqué précédemment avant de travailler sur chacun des segments en procédant organe par organe, c'est à dire en étudiant successivement le comportement temporel au niveau des différents calculateurs "boîte blanche" et des réseaux. Alors que la problématique initiale consiste à suivre le chemin d'un signal de bout-en-bout, l'approche utilisée prend une direction orthogonale en étudiant localement, au niveau de chaque calculateur traversé et chaque réseau emprunté,

les interactions avec les autres signaux correspondant aux autres fonctions mises en oeuvre concurremment dans le véhicule .

#### 1.3 Vérification des contraintes de bout-en-bout

Dans une architecture électronique automobile de type AUTOSAR, les contraintes de sûreté de fonctionnement des fonctions pilotées de criticité croissante (contrôle de la dynamique du véhicule) exigent une connaissance précise du comportement temporel du système afin notamment d'estimer de manière réaliste les temps de réponse de bout-en-bout. Ce problème est un enjeu de conception majeur sur lequel se mobilisent des acteurs industriels et académiques. Dans les travaux de thèse, nous nous situons dans le contexte de fonctions de niveau de criticité élevé pour lesquelles des garanties sur les performances temporelles de bout-en-bout sont requises. La connaissance des temps de réponse de bout-en-bout pourra alors être utilisée pour évaluer différentes solutions de conception, et ainsi optimiser l'architecture matérielle (choix du débit des réseaux, puissance des calculateurs) au regard des objectifs de performances et de sûreté de fonctionnement.

#### 1.3.1 Techniques de vérification temporelle

On distingue classiquement trois approches de vérification temporelle adaptées pour les systèmes embarqués critiques :

- Le model-checking d'automates temporisés, qui fournit des résultats exacts mais, qui, généralement, ne passe pas à l'échelle sur des systèmes de taille industrielle. Au cours des 25 dernières années, des progrès significatifs ont été réalisés sur les algorithmes comme sur les outils, le logiciel en utilisation libre Uppaal [30] est par exemple aujourd'hui une référence dans le domaine. Néanmoins le model-checking souffre intrinsèquement du problème de l'explosion combinatoire de l'espace des états du système, et ne peut être a priori envisagé comme solution unique pour la vérification des systèmes de grande taille comme peuvent l'être ceux dans un véhicule où les calculateurs exécutent des centaines de runnables et où des centaines de messages sont échangés sur chaque bus.

- Le Calcul Réseau, ou Network Calculus, est une théorie développée pour déterminer des bornes supérieures sur les temps de transmission dans les réseaux [15, 16]. Le calcul réseau se base sur une algèbre particulière pour calculer et propager des contraintes exprimées sous forme d'enveloppes. Ces enveloppes définissent la quantité de travail à réaliser au cours du temps (ex : pour exécuter une tâche de façon périodique) et la quantité de travail offerte par les ressources (puissance de calcul d'un processeur ou débit

d'un réseau). Le calcul réseau offre plusieurs avantages par rapport aux analyses d'ordonnançabilité traditionnelles. En premier lieu, il repose sur des fondements mathématiques qui permettent de réaliser les calculs de façon algébrique, donc sans recourir à des analyses ad-hoc dont la validité est plus difficile à vérifier. D'autre part, le calcul réseau passe très bien à l'échelle et est adapté pour des systèmes de très grande taille (plusieurs dizaines de milliers de flux de données échangés par plusieurs centaines de calculateurs). Pour ces raisons, le calcul réseau est utilisé en certification dans l'avionique depuis une dizaine d'année (par exemple sur l'A380). Un de ses désavantages est d'être généralement plus pessimiste que le model-checking et que les analyses d'ordonnançabilité traditionnelles, et donc potentiellement de conduire à un surdimensionnement des ressources matérielles. Si depuis, des progrès théoriques sont réalisés et les différences avec les autres approches s'amenuisent [39], cette approche est moins pertinente pour notre problèmatique car nous étudions individuellement les différents calculateurs et réseaux. Le périmètre des systèmes étudiées (un calculateur ou un réseau CAN) ne justifie pas d'employer le calcul réseau afin de faire face à la taille du système.

– L'ordonnancement temps réel est une discipline très active depuis le début des années 70 avec un grand nombre de résultats adaptés à des contextes technologiques variés. L'approche est ici, non pas d'explorer exhaustivement l'espace des états du système, mais de construire et d'analyser un sous-ensemble de trajectoires que l'on peut prouver défavorables d'un point de vue temporel. La plupart des résultats concernent l'ordonnancement des processeurs mais des extensions ont été rapidement réalisées, par exemple l'approche holistique développée à York dans [31], pour les systèmes distribués puis les approches à base de trajectoire [43, 41]. Plus récemment, des avancées ont été faites vers des modèles compositionnels, que ce soit dans le cas centralisé [27] ou dans le contexte de systèmes distribués [65] ou encore l'approche développée à la T.U. Braunschweig, utilisée dans le logiciel commercial Symta/S [26].

Dans le contexte de la vérification des contraintes de bout-en-bout lors de la conception d'une fonction pilotée pour une voiture, cette dernière approche est plus adaptée au regard de la complexité du système et du choix fait d'étudier séparément les temps de réponses sur les calculateurs et les réseaux.

#### 1.3.2 Contributions

En raison des contraintes liées au processus de conception considéré dans le cadre de cette thèse, nous avons fait le choix de passer d'une étude globale à une étude basée sur une décomposition hiérarchique. Ainsi, nous contribuons séparément à la vérification des contraintes de bout-en-bout au niveau de l'ordonnancement des composants logiciels sur les calculateurs et des messages sur les réseaux

CAN. En effet, la présence de boîtes noires et le développement en parallèle, du matériel, du logiciel et des réseaux rend impossible la validation des contraintes en les considérant de bout-en-bout. De plus, l'indisponibilité d'un certain nombre d'information ainsi que l'impossibilité de saisir toutes les interactions entre les fonctions dû à la complexité générale de l'ensemble de l'architecture électronique d'une voiture rend stérile toute tentative d'optimisation globale des performances temporelles du système.

Les contributions de cette thèse sont présentées dans les trois chapitres suivants et correspondent respectivement aux questions suivantes.

Comment garantir un respect des contraintes de temps sur les calculateurs AutoSar en optimisant leur utilisation? La grande majorité des composants logiciels et des messages émis ont un comportement de type périodique avec échéance sur requête (leur échéance est égale à la date de leur prochaine activation), entre autres raisons à cause du grand nombre de fonctions de contrôlecommande. Dans cette mesure, des améliorations sur les comportements temporels pire cas des différents composants peuvent être obtenues via un effort de lissage de la charge périodique sur les différents calculateurs et réseaux en utilisant des offsets pour décaler leurs dates d'activation. L'application de cette approche sur les réseaux CAN [24] a permis de réduire considérablement les temps de réponse des messages et permet d'utiliser de manière plus efficace la puissance de calcul des processeurs ou la bande passante des réseaux. Ceci est très intéressant du point de vue industriel car cela permet d'être robuste vis-à-vis de la charge apériodique critique, de monter plus haut en charge sur ces différents organes et de pouvoir ajouter de nouvelles fonctionnalités sur une architecture existante sans changer le support matériel. Par ailleurs, de plus en plus de calculateurs multi-cœurs sont intégrés dans les véhicules pour monter en puissance alors que les montées en fréquence des processeurs commence à montrer leurs limites en fiabilité. Dans le chapitre 2, nous démontrons comment appliquer cette technique sur des calculateurs multi-cœurs.

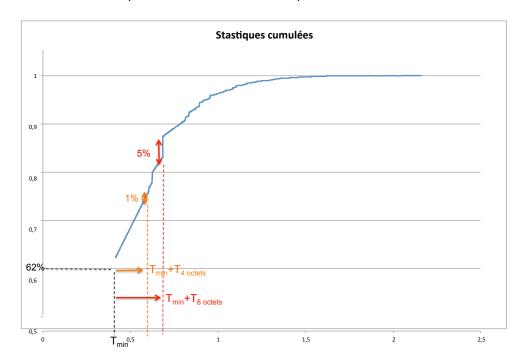

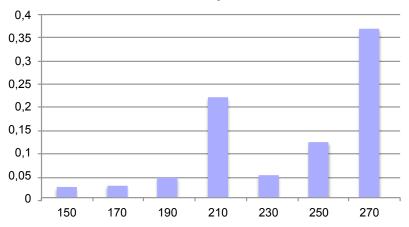

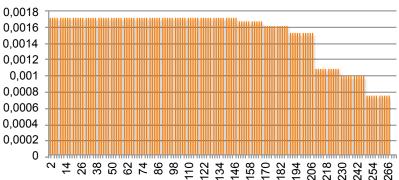

CAN en modélisant les dérives d'horloge sur les stations émettrices? Nous cherchons à modéliser le phénomène de dérive d'horloge et étudier leur influence sur les distributions de temps de réponse obtenues par simulation. Par opposition aux temps de réponse pire cas qui étaient les seules informations que les concepteurs pouvaient typiquement obtenir par analyse, les distributions de temps de réponses sont incomparablement plus riches en information. Leur connaissance peut permettre entre autre de dimensionner l'architecture matérielle plus finement en utilisant des critères quantitatifs basés sur les probabilités de défaillance (par exemple, défaillances par heure) dans le contexte où l'on associe le dépassement du temps de réponse d'un message par rapport à une valeur seuil (l'échéance) comme

une faute. Cela permet alors de considérer des temps de réponses sensiblement plus faibles en comparaison des valeurs pire cas traditionnellement utilisées. Dans le chapitre 3, nous étudions comment conduire des simulations avec dérives d'horloge pour obtenir des résultats pertinents pour différents horizons de simulation : des courtes simulations pour étudier ce qu'il se passe localement dans des scénarios pire cas et des longues simulations pour étudier le comportement sur le long terme (durée de vie du véhicule) des messageries CAN.

Comment obtenir par analyse une estimation de la distribution de temps de réponse d'une trame CAN? Toutes les trames sur un réseau n'ont pas le même niveau de criticité. Il est donc important d'avoir un modèle fin du comportement donné d'une trame critique, généralement de haute priorité, et d'exhiber des évaluations de ses temps de réponse. Pour traiter ce problème, nous avons adopté une approche probabiliste qui permet d'avoir une estimation de la distribution de temps de réponse d'une trame émise sur un réseau CAN. Nous calculons des estimations car la complexité des calculs augmente considérablement au fur et à mesure que sont étudiés des messages de moins en moins prioritaires. En revanche, si certaines approximations sont tout le temps appliquées, l'approche que nous présentons dans le chapitre 4 incorpore plusieurs paramètres contrôlés par l'utilisateur permettant de jouer sur la précision des résultats obtenus.

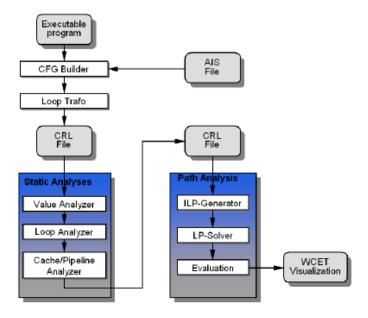

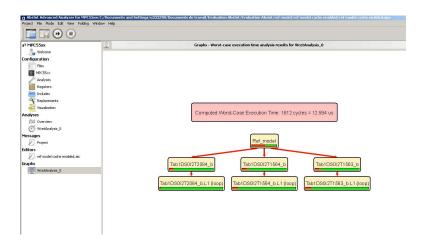

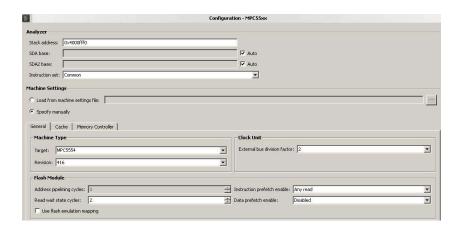

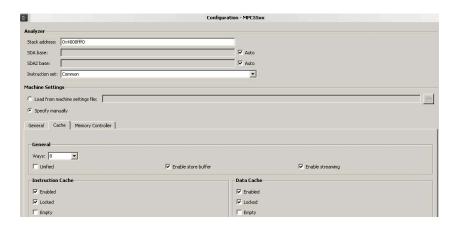

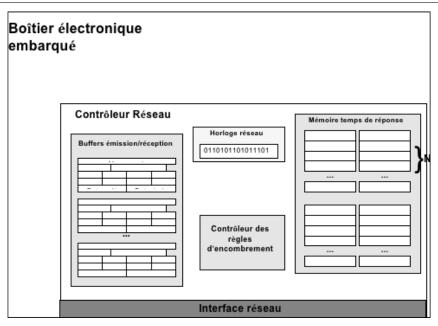

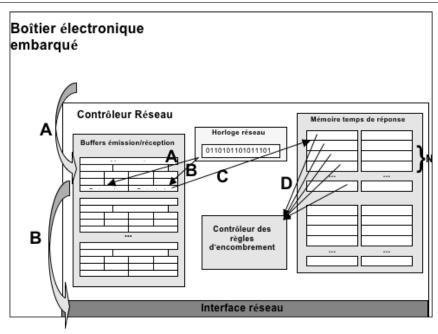

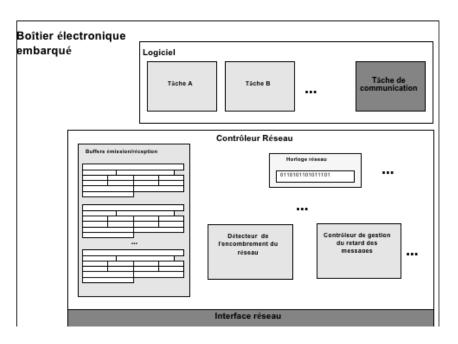

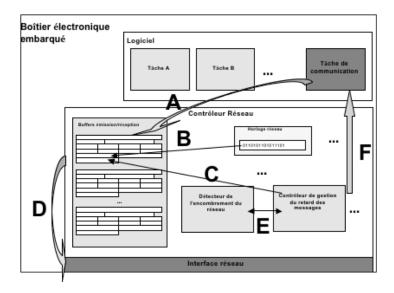

Ce mémoire comporte également en annexe deux autres contributions réalisées dans le cadre de cette thèse. Ces contributions s'inscrivent dans le contexte industriel de la thèse et nous avons fait le choix de les séparer du corps du mémoire pour lequel nous nous sommes restreint aux travaux de recherche. L'annexe B décrit l'évaluation d' "aiT" de la société AbsInt, un outil logiciel permettant d'estimer des bornes sur les pire-temps d'exécution de composants logiciels. Cette étude est en lien avec les travaux de chapitre 2 pour lesquels la connaissance précise des temps d'exécution des runnables est importante. En effet, il est de pratique courante d'utiliser une évaluation "gros grain" basée sur le retour d'expérience et l'expertise des concepteurs des fonctions, par exemple sous la forme d'une valeur de 1 à 10 représentant grossièrement le temps d'exécution d'un runnable. Utiliser un outil d'analyse statique du code permet effectivement d'avoir une connaissance plus fine des temps d'exécution relatifs des différents composants logiciels qui seront exécutés sur les calculateurs avant le développement du matériel. Enfin, l'annexe C comporte la description de dispositifs intégrés aux contrôleurs de communication visant à détecter et résoudre les situations d'encombrement des réseaux CAN. Ces travaux ont été réalisés suite à des observations faites sur les résultats présentés dans le chapitre 3 et ont donné lieu à trois brevets [7, 8, 9].

## Chapitre 2

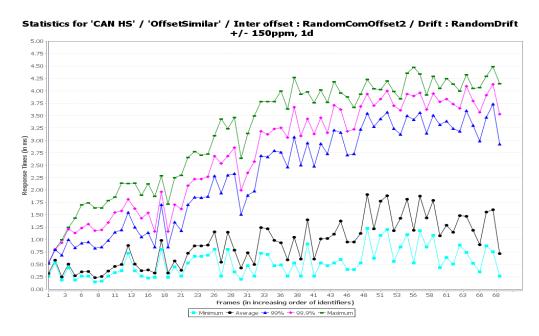

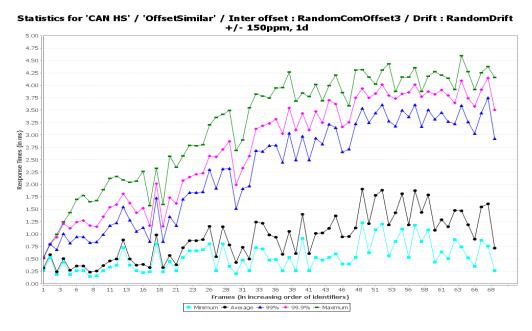

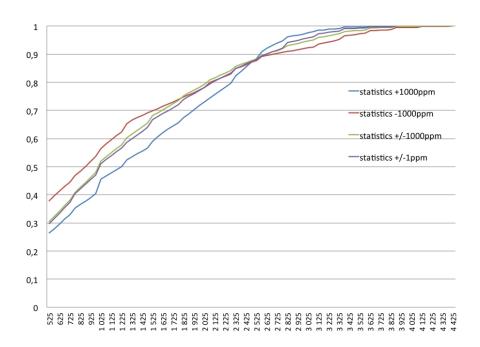

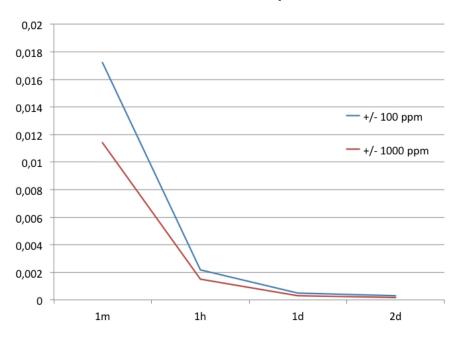

# Ordonnancement de runnables sur les calculateurs AutoSar