## Caractérisation, analyse et modélisation du MOSFET de puissance en carbure de silicium

Dinh-Lam Dang

#### ▶ To cite this version:

Dinh-Lam Dang. Caractérisation, analyse et modélisation du MOSFET de puissance en carbure de silicium. Energie électrique. Université de Lorraine, 2019. Français. NNT: 2019LORR0052. tel-02328690

### HAL Id: tel-02328690 https://hal.univ-lorraine.fr/tel-02328690

Submitted on 23 Oct 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

#### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

# **THÈSE**

Présentée à

#### L'Université de Lorraine

En vue de l'obtention du

#### DOCTORAT DE L'UNIVERSITÉ DE LORRAINE

Spécialité: Génie Electrique

par

#### Dinh Lam DANG

Master diplôme de L'Institut polytechnique de Hanoï

# Caractérisation, analyse et modélisation du MOSFET de puissance en carbure de silicium

Soutenue publiquement le 04 juillet 2019 devant le jury composé de :

Président Corinne ALONSO Professeure, Université Toulouse-III-Paul-Sabatier

Rapporteurs Nadir IDIR Professeur, Université de Lille

Stéphane LEFEBVRE Professeur, Conservatoire National des Arts et Métiers

Directeurs de thèse Stéphane RAEL Professeur, Université de Lorraine

Matthieu URBAIN Maître de conférences, Université de Lorraine

# **THESIS**

Presented at

#### The University of Lorraine

to obtain the

#### DOCTORATE OF THE UNIVERSITY OF LORRAINE

**Specialty: Electrical Engineering**

# by **Dinh Lam DANG**

Master degree of Hanoi University of Science and Technology

# Characterization, analysis and modeling of silicon carbide power MOSFET

Publicly defended on July 04<sup>th</sup> 2019 in front of the jury composed of:

President Corinne ALONSO Professor, University Toulouse-III-Paul-Sabatier

Reporters Nadir IDIR Professor, University of Lille

Stéphane LEFEBVRE Professor, The C.N.A.M Paris

Supervisors Stéphane RAEL Professor, University of Lorraine

Matthieu URBAIN Associate Professor, University of Lorraine

#### Acknowledgements

First of all, I would like to express my profound gratitude to my supervisor, Prof. Stéphane RAEL, for his guidance with a lot of patience, his encouragement and his invaluable support that made this thesis possible. I am extremely grateful for all the time and everything he has done for me on both academic and personal aspects.

I wish to express my sincere gratitude to my co-supervisor, Assoc. Prof. Matthieu URBAIN, for his helpful and constructive comments, our fruitful discussions, his enthusiastic encouragement and continuous support during these years. Without him, this thesis could not be finished.

I would like to thank Prof. Corrine ALONSO, Prof. Nadir IDIR and Prof. Stephane LEFEBVRE for having accepted to be members of my committee. I am very grateful for their precious time and their brilliant comments and suggestions.

I would like to extend my sincere thanks to all the people in the laboratory GREEN at the University of Lorraine, including current and former people that I have had chance to interact with, for the pleasant atmosphere and for their kindness. A special thank goes to Mrs Latifa ZOUA, Mrs Sylvie COLINE, Mrs Sophie GUICHARD, Prof. Bernard DAVAT, Prof. Noureddine TAKORABET the great support.

I am greatly thankful to my friends for their encouragement and support during my studying. Special thanks are dedicated to my Vietnamese friends who have been with me to share memorable moments during my stay in France, family of Hoai Le NGUYEN, family of Van Duy TRAN, family of Dinh Hoan TRINH, family of Si Hung NGUYEN HO, family of Tan My LAM, family of Manh Tuyen TRINH, family of Phi Linh NGUYEN, Tan Binh PHAN, Thao PHAN, Vinh Thanh HO, Ha Son NGO, Thuong Huyen MA, Thuy TRAN, Nguyen Ha QUACH, Duc Trung NGUYEN, and many others. In addition, I would like to thank all my friends who once helped me in completion of this work in so many ways.

Additionally, and much importantly, I am greatly thankful the funding sources that helped my PhD dissertation possible: 911-fellowship of Vietnam Ministry of Education and Training (MOET) and GREEN/University of Lorraine grant.

Last but definitely not least, I am especially indebted to my parents and my family for their selfless love and unwavering belief in me, during the pursuit of my degree. Con cảm ơn bố mẹ đã dành những thứ tốt đẹp nhất cho con, luôn tin tưởng, ủng hộ, động viên con. Cảm ơn em gái, em rể và hai cháu đã luôn bên cạnh, động viên, giúp đỡ anh trong cuộc sống. Xin dành lời cảm ơn đến các bác, cậu, dì, các anh, chị, em luôn dành tình cảm và động viên con từ ngày con sang Pháp.

Cho tình yêu của bố mẹ Cho giấc mơ của con....

To my beloved parents

#### **Abstract**

Silicon carbide (SiC) has actively been emerged as the most viable candidate of the wide band gap (WBG) semiconductors to replace silicon (Si) in the near future. Due to its inherent properties, SiC enables the development of new generation semiconductor devices that offer great performance improvements, resulting in more efficient and compact designs in various power electronics applications. The 1.2 kV SiC MOSFETs, which are by far the most important devices in the SiC family, have been quickly used as the replacement of Si IGBTs in many applications due to their superior characteristics. However, at an early stage of development, SiC MOSFETs come with their own list of technical and economic issues which have somehow limited their widespread implementation for power electronics applications.

The characterization and modeling, in particular on-state of the SiC MOSFET, have been investigated in this dissertation to develop insight of the unique characteristics along with the effects on the design of power converters.

In such a way, the characterization test benches for high voltage power MOSFETs have been developed. The device is characterized using appropriate methods, which allows the junction temperature to remain constant during the measurement. The characteristics are then analyzed and compared to these of Si counterpart to provide further understanding of SiC MOSFETs. Subsequently, a novel compact model has been developed for circuit simulation, taking into account physical phenomena including interface traps, short-channel, intrinsic JFET and temperature effects. As a modified version of the Shichman Hodges, the model employs a few adjustment parameters, which are mostly derived from curve fitting of experimental data, using optimization tool software. The proposed model with fairly simple current equation thus is expedient to represent the DC behavior of power MOSFET for a wide range of operation conditions. In the end, the thermal characterization of SiC MOSFETs is examined. The on-resistance has been proposed as a temperature-sensitive electrical parameter (TSEP) to estimate the junction temperature. In the presence of the interface traps, the dedicated test benches have been developed for SiC MOSFET temperature measurement based on TSEP. 3D Finite element (FEM) simulation is performed to investigate thermal distribution inside the module. By comparing with the experiments, the electro-thermal model is validated with acceptable accuracy.

Keywords: SiC, MOSFET, I-V characteristics, modeling, thermal measurement, TSEP

#### Résumé

Le carbure de silicium (SiC) semble être actuellement le candidat le plus viable des semi-conducteurs à large bande interdite pour remplacer le silicium (Si) dans un avenir proche. En raison de ses propriétés intrinsèques, le SiC permet de développer des dispositifs à semi-conducteurs aux caractéristiques supérieures offrant de grandes améliorations de performances, et se traduisant également par des conceptions plus efficaces et compactes dans diverses applications de l'électronique de puissance. Les MOSFET de 1,2 kV SiC, de loin les composants les plus répandus de la famille pour équiper les sources de puissance, ont rapidement été déployés pour remplacer les modules IGBT Si en raison de leur résistance à l'état passant faible et de leurs excellentes performances de commutation dans toutes les plages de température. Cependant, encore à un stade précoce de développement, les MOSFET SiC présentent leurs problèmes techniques et économiques propres, lesquels problèmes ont freiné leur expansion en électronique de puissance.

La caractérisation et la modélisation, en particulier l'état de fonctionnement du MOSFET SiC, ont été examinées dans le cadre de cette thèse afin de mettre en lumière les spécificités et les conséquences qui en découlent sur la conception des convertisseurs de puissance.

C'est ainsi qu'une méthodologie de caractérisation statique pour les MOSFET à haute tension a été développée. Les caractéristiques ont été mesurées par méthodes appropriées permettant à la température de la jonction de rester constante pendant la mesure. Les résultats expérimentaux ont été analysés et comparés à ceux relatifs aux dispositifs conventionnels en Si. Ensuite, un nouveau modèle compact du module MOSFET SiC a été mis au point sur le logiciel Saber pour des simulations orientées circuit. Ce modèle prend en compte les phénomènes physiques observés, notamment les effets des pièges d'interface, le comportement JFET intrinsèque, le canal court et la température. En tant que version modifiée de Shichman Hodges, le modèle utilise un nombre raisonnable de paramètres d'ajustement, lesquels sont principalement extraits par identification des courbes de données expérimentales à l'aide d'un logiciel d'optimisation, et pour les autres étant basés sur les données disponibles dans la fiche technique du composant étudié. Finalement, nous avons abordé la caractérisation électro-thermique des MOSFET de SiC. Pour remédier à la présence de pièges d'interface, des bancs de test dédiés ont été développés pour la mesure de la température MOSFET au SiC sur la base du TSEP. Une simulation par éléments finis 3D (FEM) est réalisée pour étudier la distribution thermique à l'intérieur du module. En comparant avec les expériences, le modèle électro-thermique a été validé avec une précision acceptable.

Mots-clés: SiC, MOSFET, caractéristiques I-V, modélisation, mesure thermique, TSEP

# **Table of contents**

| Acknowledgements                                                    | i   |

|---------------------------------------------------------------------|-----|

| Abstract                                                            | v   |

| Résume                                                              | vi  |

| List of Figures                                                     | xi  |

| List of Tables                                                      | xiv |

| List of Abbreviations and Symbol                                    | xv  |

| Introduction générale                                               | 1   |

| Contexte de l'étude                                                 | 1   |

| Résultats et contributions essentiels                               | 2   |

| General Introduction                                                | 8   |

| Background                                                          | 8   |

| Outline of this work                                                | 9   |

| Chapter 1 Fundamentals of wide band gap power devices               | 11  |

| 1.1. Background                                                     | 11  |

| 1.2. Band gap energy                                                | 12  |

| 1.3. Electric characteristics of wide band gap semiconductors       | 13  |

| 1.3.1. Wide band gap energy and low intrinsic carrier concentration | 13  |

| 1.3.2. High breakdown electric field                                | 14  |

| 1.3.3. Other properties                                             | 15  |

| 1.4. Emerging trends in WBG devices                                 | 16  |

| 1.4.1. Wafers                                                       | 16  |

| 1.4.2. Structures                                                   | 17  |

| 1.4.3. SiC power devices                                            | 18  |

| 1.5. Technical issues in power SiC devices                          | 19  |

| 1.5.1. Metallization                                                | 19  |

| 1.5.2. Metal-Oxide-Semiconductor in SiC                             | 20  |

| 1.6. SiC power diodes                                               | 21  |

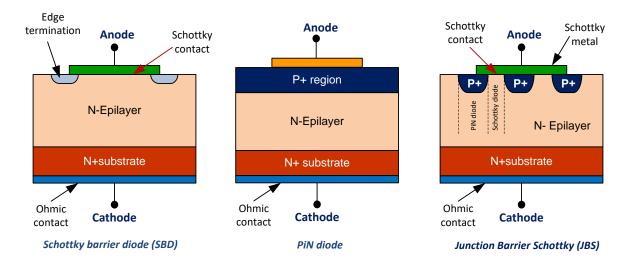

| 1.6.1. Schottky Barrier Diode (SBD)                                 | 22  |

| 1.6.2. SiC PiN                                                      | 23  |

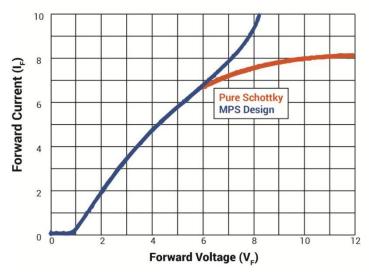

| 1.6.3. SiC JBS                                                      | 24  |

| 1.7. SiC unipolar transistors                                       | 25  |

| 1.7.1. SiC JFET                                                     | 25  |

| 1.7.1. SiC MOSFET                                               | 26 |

|-----------------------------------------------------------------|----|

| 1.8. SiC bipolar transistors                                    | 26 |

| 1.9. Conclusions                                                | 27 |

| Chapter 2 High voltage 4H-SiC power MOSFET technical discussion | 29 |

| 2.1. Structure of SiC MOSFET                                    | 29 |

| 2.1.1. Overview                                                 | 29 |

| 2.1.2. Structure of planar gate SiC MOSFET                      | 30 |

| 2.2. The modes of operation                                     | 31 |

| 2.2.1. The threshold voltage and the formation of channel       | 31 |

| 2.2.2. The first quadrant operation                             | 34 |

| 2.2.3. The third quadrant operation                             | 37 |

| 2.2.4. Forward off state (blocking)                             | 38 |

| 2.3. SiC MOSFET gate oxide challenges                           | 40 |

| 2.3.1. Gate oxide growth                                        | 40 |

| 2.3.2. Gate oxide reliability                                   | 41 |

| 2.3.3. Interface traps                                          | 42 |

| 2.3.4. Oxide charges                                            | 43 |

| 2.4. SiC MOSFET technical issues                                | 44 |

| 2.4.1. Threshold voltage                                        | 44 |

| 2.4.2. Channel mobility                                         | 45 |

| 2.4.3. On-resistance                                            | 47 |

| 2.5. Conclusion                                                 | 50 |

| Chapter 3 SiC MOSFET on-state characterization                  | 51 |

| 3.1. Pulsed DC measurement and self-heating constraint          | 51 |

| 3.2. Threshold voltage V <sub>TH</sub>                          | 53 |

| 3.3. Output characteristics                                     | 55 |

| 3.3.1. Test bench                                               | 55 |

| 3.3.2. Principles of measurement                                | 55 |

| 3.3.3. Results and discussions                                  | 57 |

| 3.4. Transfer characteristics                                   | 59 |

| 3.4.1. Test bench                                               |    |

| 3.4.2. Principle of measurement                                 | 60 |

| 3.4.3. Results and discussions                                  | 61 |

| 2.5. Zoro amp on resistance                                     | 62 |

|    | 3.5.1. Measurement methods                                | 63  |

|----|-----------------------------------------------------------|-----|

|    | 3.5.2. Test bench                                         | 64  |

|    | 3.5.3. Results and discussions                            | 65  |

|    | 3.6. Conclusion.                                          | 67  |

| Cł | napter 4 SiC MOSFET on-state modeling                     | 68  |

|    | 4.1. The MOSFET model overview                            | 68  |

|    | 4.1.1. The MOSFET model classification                    | 68  |

|    | 4.1.2. Parameter extraction                               | 69  |

|    | 4.2. Power SiC MOSFET modeling                            | 70  |

|    | 4.2.1. Shichman-Hodges model                              | 70  |

|    | 4.2.2. Interface traps and their effects in SiC modeling  | 72  |

|    | 4.2.3. Survey of related works in SiC MOSFET modeling     | 75  |

|    | 4.3. Interface traps effect on threshold voltage          | 76  |

|    | 4.4. Current gain and R <sub>DS(ON)</sub> modeling        | 78  |

|    | 4.4.1. R <sub>DS(ON)</sub> modeling with temperature      | 79  |

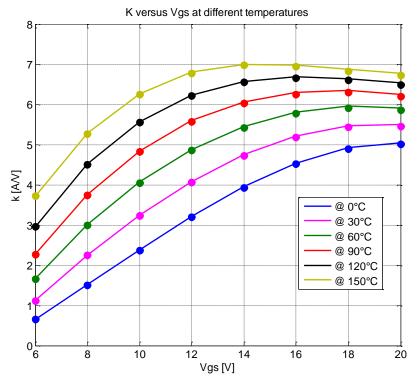

|    | 4.4.2. K determination and R <sub>DS(ON)</sub> validation | 82  |

|    | 4.5. SiC MOSFET DC modeling                               | 85  |

|    | 4.5.1. The coefficient $\alpha$ and short-channel problem | 86  |

|    | 4.5.2. JFET effect in SiC MOSFET                          | 86  |

|    | 4.5.3. Channel voltage                                    | 87  |

|    | 4.6. Parameter extraction and model validation            | 88  |

|    | 4.6.1. Parameter extraction                               | 88  |

|    | 4.6.2. Simulation in Saber                                | 91  |

|    | 4.8. Conclusion.                                          | 92  |

| Cł | napter 5 Thermal measurements and model validation        | 93  |

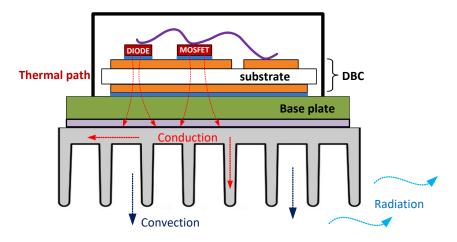

|    | 5.1. Thermal issues in power semiconductor devices        | 93  |

|    | 5.1.1. Power semiconductor device package                 | 93  |

|    | 5.1.2. Thermal management                                 | 94  |

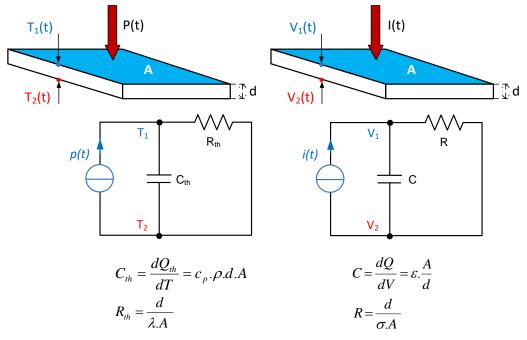

|    | 5.2. Device electro-thermal characterization              | 95  |

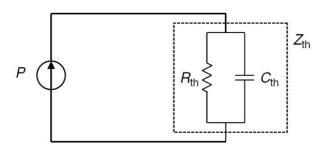

|    | 5.2.1. Electrical analogy for thermal modeling            | 95  |

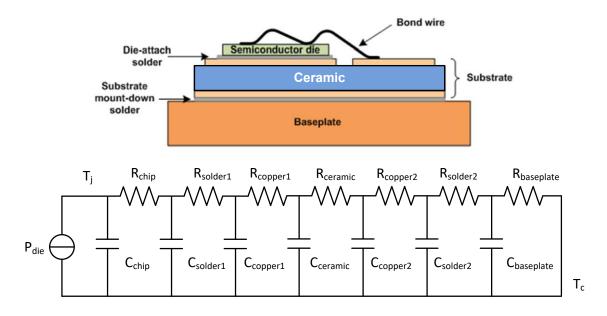

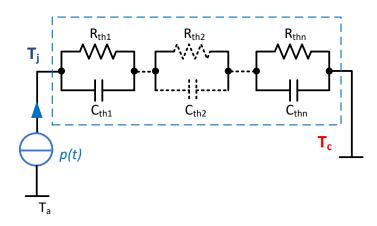

|    | 5.2.2. Thermal equivalent circuit                         | 97  |

|    | 5.2.3. Thermal impedance                                  | 98  |

|    | 5.2.4. Thermal resistance                                 | 99  |

|    | F.2. Thormal resistance measurement                       | 100 |

| 5.3.1. Principle of measurement                                             | 100 |

|-----------------------------------------------------------------------------|-----|

| 5.3.2. Estimation of junction temperature                                   | 101 |

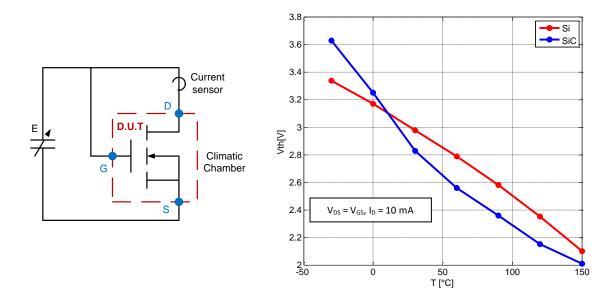

| 5.3.3. Identifying the TSEP                                                 | 101 |

| 5.3.4. Principle of TSEP                                                    | 102 |

| 5.4. Calibration for SiC MOSFET electro-thermal characterization            | 103 |

| 5.4.1. Selection of TSEP for SiC MOSFET                                     | 103 |

| 5.4.2. Calibration                                                          | 103 |

| 5.4.3. Discussion                                                           | 105 |

| 5.5. Measurement of the self-heating thermal resistance                     | 106 |

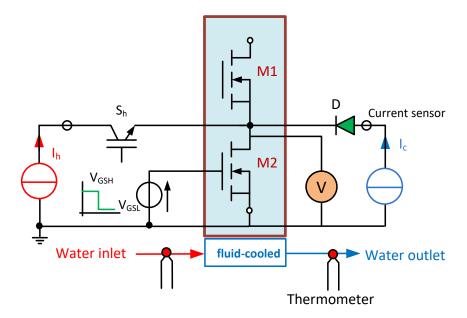

| 5.5.1. Principle and experimental setup                                     | 106 |

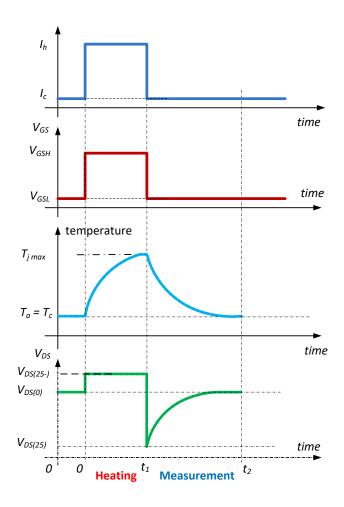

| 5.5.2. Experimental procedure                                               | 108 |

| 5.5.3. Results and discussion                                               | 109 |

| 5.6. Measurement of the mutual thermal resistance                           | 111 |

| 5.6.1. Thermal phenomena in a multichip structure                           | 111 |

| 5.6.2. Experimental setup and measurement procedure                         | 112 |

| 5.6.3. Results and discussion                                               | 113 |

| 5.7. Evaluation of self-heating thermal resistance through thermal modeling | 113 |

| 5.8. Conclusion                                                             | 116 |

| General Conclusions and Perspectives                                        | 117 |

| References                                                                  | 119 |

### List of Figures

| Figure 1.1. Power electronics system structure                                                      | 11 |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 1.2. Orbital model of some atoms and simplified energy band diagram                          | 12 |

| Figure 1.3. Leakage current in a PN junction                                                        |    |

| Figure 1.4. Electric field in an abrupt one-sided PN junction                                       | 15 |

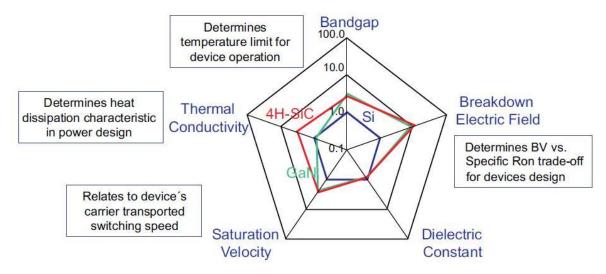

| Figure 1.5. Impact of different physical parameters of semiconductor on devices                     | 16 |

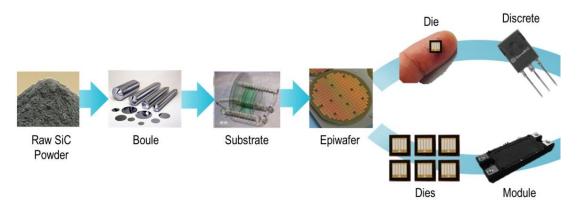

| Figure 1.6. SiC manufacturing process                                                               | 17 |

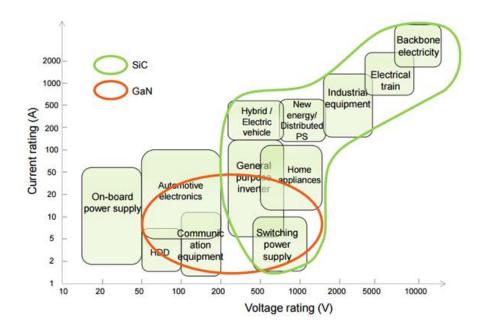

| Figure 1.7. Application of SiC and GaN devices by the power                                         | 18 |

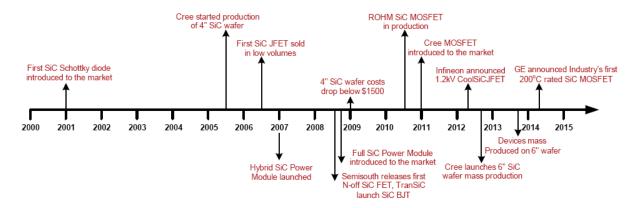

| Figure 1.8. The development process of SiC semiconductor devices                                    | 19 |

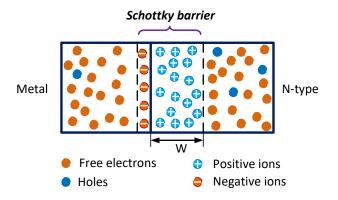

| Figure 1.9. Metal-semiconductor junction with Schottky barrier at thermal equilibrium               | 19 |

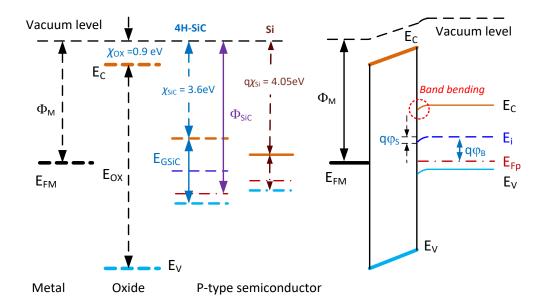

| Figure 1.10. Band diagram at the MOS interface after and before contact                             | 21 |

| Figure 1.11. Cross sections of power diodes                                                         |    |

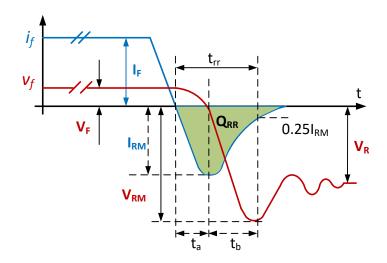

| Figure 1.12. Reverse recovery waveform of a diode                                                   |    |

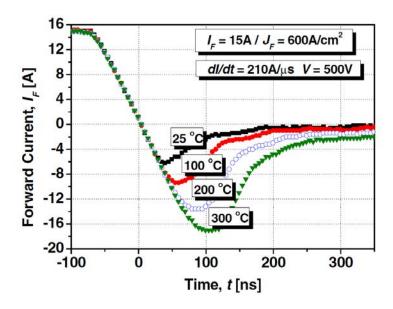

| Figure 1.13. Turn-off switching waveform of the SiC PiN [39]                                        |    |

| Figure 1.14. Forward bias characteristics of a SiC MPS diode and a SBD                              |    |

| Figure 1.15. Cross-sectional view of SiC vertical JFET                                              |    |

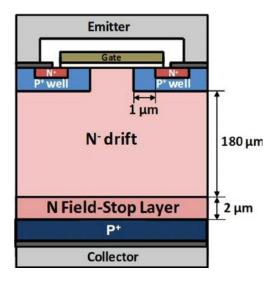

| Figure 1.16. Cross section of 22kV 4H-SiC N-IGBT                                                    | 27 |

|                                                                                                     |    |

| Figure 2.1. Planar versus trench gate MOSFET unit cell comparison                                   |    |

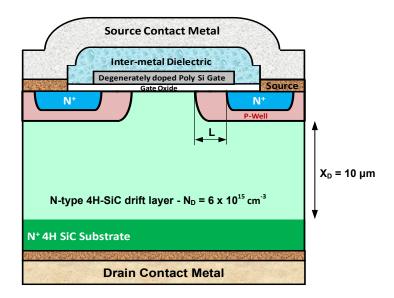

| Figure 2.2. Cellular design of the 1.2 kV 4H-SiC DMOSFET                                            |    |

| Figure 2.3. Internal layout of SiC MOSFET CAS100H12AM1 module                                       | 31 |

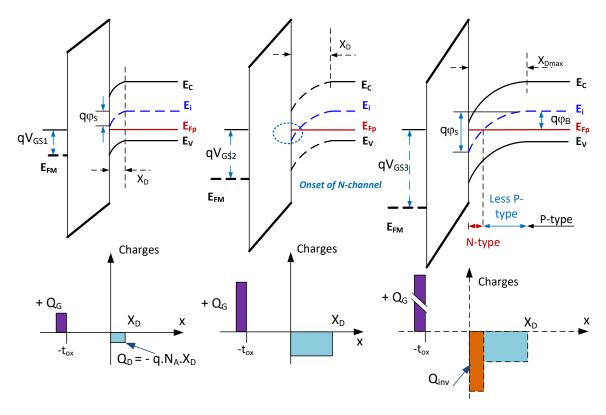

| Figure 2.4. Energy-band diagrams for an N-channel MOSFET under different conditions                 | 32 |

| Figure 2.5. Charges and potentials of MOSFET with different gate bias                               |    |

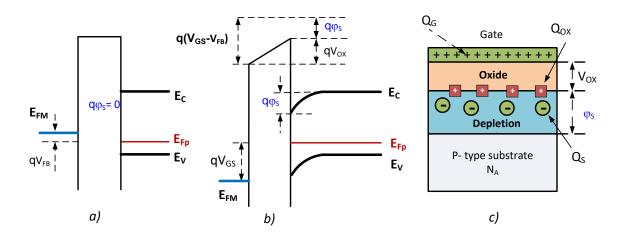

| Figure 2.6. Inversion layer thickness vs V <sub>DS</sub>                                            |    |

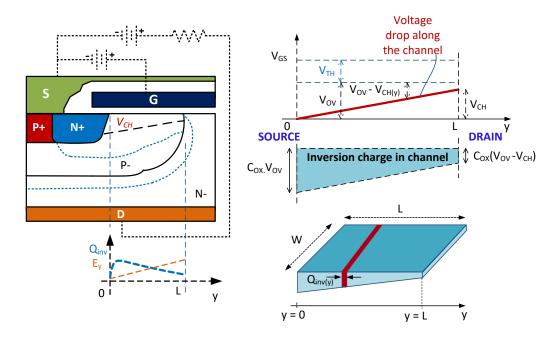

| Figure 2.7. The inversion layer after pinch-off                                                     | 36 |

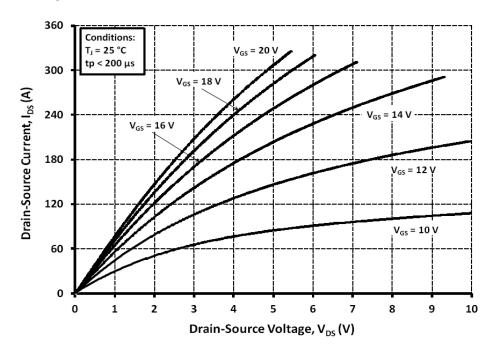

| Figure 2.8. Forward output characteristics of 120 A – 1.2 kV SiC MOSFET at 25°C                     |    |

| Figure 2.9. Current in reverse conduction                                                           | 37 |

| Figure 2.10. Output characteristics curves                                                          | 38 |

| Figure 2.11. Electric fields in the VDMOSFET in the blocking state                                  |    |

| Figure 2.12. Reach-through and P-base doping                                                        | 39 |

| Figure 2.13. Second breakdown from the parasitic NPN bipolar transistor                             | 40 |

| Figure 2.14. A schematic of SiO <sub>2</sub> growth by thermal oxidation of SiC                     | 41 |

| Figure 2.15. Planar gate VDMOSFET oxide reliability                                                 | 41 |

| Figure 2.16. Schematic energy distribution and contributions to the SiO <sub>2</sub> interface      | 42 |

| Figure 2.17. Oxide charges in SiC-SiO <sub>2</sub>                                                  | 43 |

| Figure 2.18. Band diagram of N-channel MOSFET in different gate bias                                | 44 |

| Figure 2.19. Drift velocity for electrons in SiC                                                    | 47 |

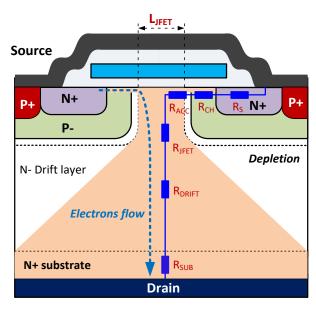

| Figure 2.20. The internal resistances in a power MOSFET                                             | 48 |

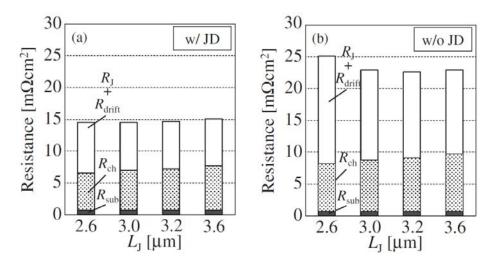

| Figure 2.21. JFET length and doping dependence of specific on-resistance of 3.3 kV MOSFET           | 49 |

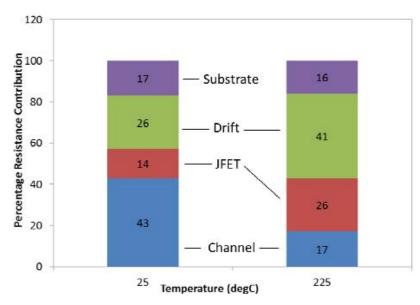

| Figure 2.22. The shares of the particular parts of the resistance $R_{DS(ON)}$ of SiC MOSFET 1.7 kV | 50 |

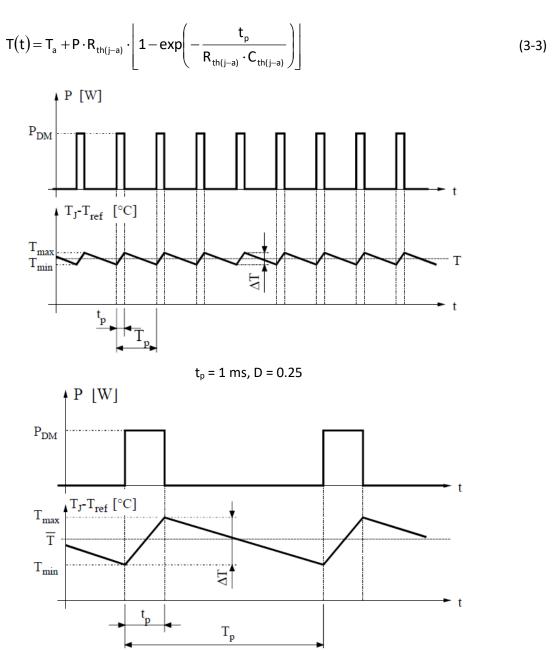

| Figure 3.1. Electrical circuit equivalence thermal impedance                                        | 51 |

| Figure 3.2. Device temperature T <sub>j</sub> vs. time for periodic pulse operation                    | 52 |

|--------------------------------------------------------------------------------------------------------|----|

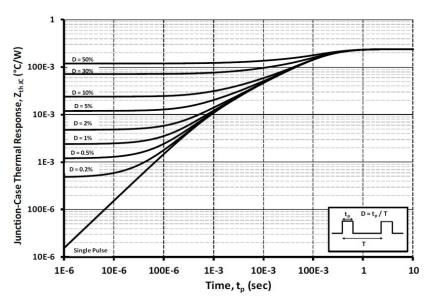

| Figure 3.3. Transient thermal impedance of the SiC MOSFET CAS100H12AM1                                 | 53 |

| Figure 3.4. V <sub>TH</sub> measurement circuit and results obtained                                   | 54 |

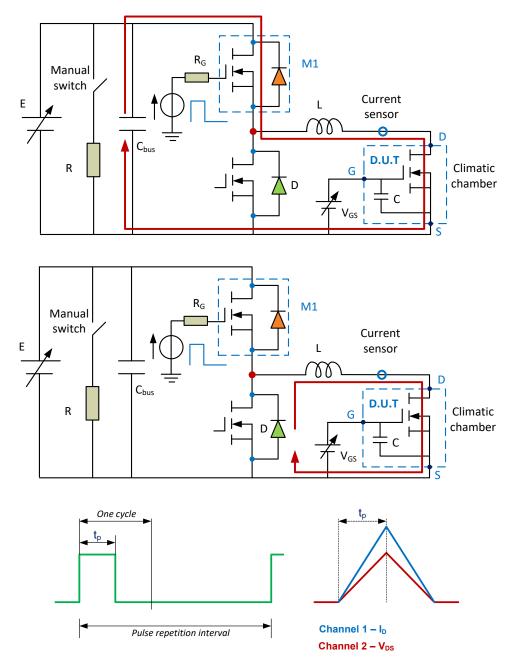

| Figure 3.5. Schematic of output characterization test bench                                            | 55 |

| Figure 3.6. Operation of circuit and waveforms                                                         | 56 |

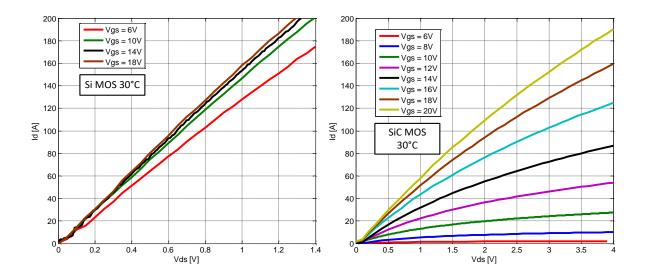

| Figure 3.7. Output characteristics of MOSFETs at 30 °C.                                                | 57 |

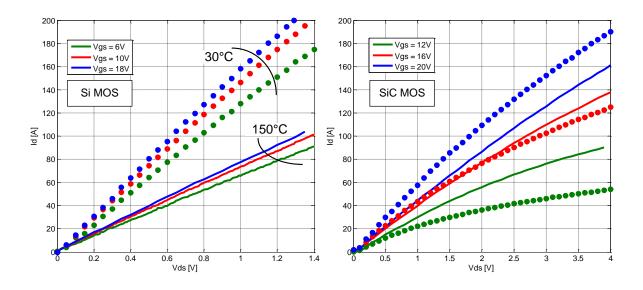

| Figure 3.8. Output characteristics of MOSFETs at 30 °C and 150 °C                                      | 58 |

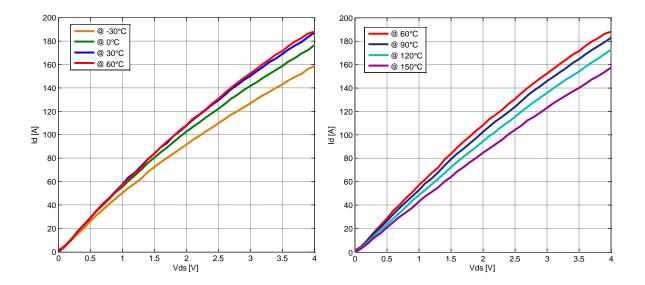

| Figure 3.9. SiC MOSFET output characteristics for different junction temperatures at $V_{GS}$ = 20 $V$ |    |

| Figure 3.10. Output characteristics of SiC MOSFET (CAS100H12AM1) at $V_{GS}$ = 10 V and Tj = 60 °C     | 59 |

| Figure 3.11. Schematic of the transfer characterization test bench                                     | 60 |

| Figure 3.12. Gate bias V <sub>GS</sub> waveform                                                        | 60 |

| Figure 3.13. MOSFET transfer characteristics for different temperatures.                               | 61 |

| Figure 3.14. Transfer characteristics of Si and SiC MOSFETs at $V_{DS}$ = 10 V and $T_j$ = 30 °C       | 62 |

| Figure 3.15. R <sub>DS(ON)</sub> and static bias points at 30°C.                                       | 63 |

| Figure 3.16. Pulse method to measure on-state resistance                                               | 63 |

| Figure 3.17. Method to measure zero-amp on-state resistance                                            | 64 |

| Figure 3.18. Zero-amp on-resistance vs V <sub>GS</sub>                                                 | 65 |

| Figure 3.19. Zero-amp on-resistance versus temperature at low gate bias                                | 66 |

| Figure 3.20. SiC MOSFET zero-amp on resistance versus temperature at low gate bias                     | 67 |

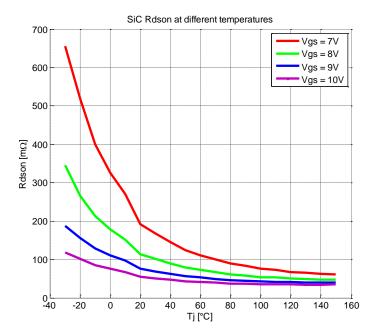

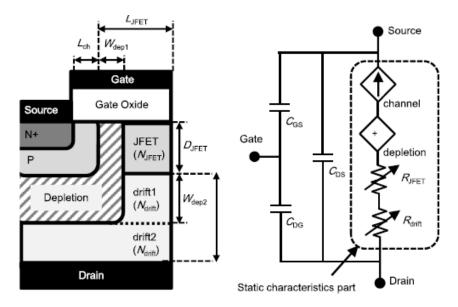

| Figure 4.1. Half structure of the reference device and analytical model for short channel MOSFET       |    |

| Figure 4.2. Macro behavioral MOSFET model                                                              |    |

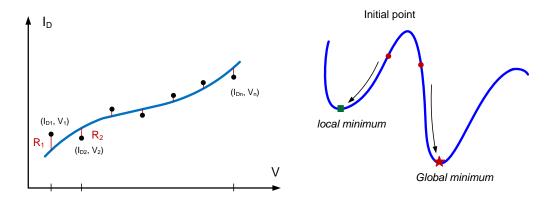

| Figure 4.3. Parameters extraction using the minimum sum of least square deviations                     |    |

| Figure 4.4. Four series components of voltage drop in VDMOSFET                                         |    |

| Figure 4.5. The models for a power MOSFET                                                              |    |

| Figure 4.6. Electrons trapping in acceptor-like states in N-channel SiC MOSFET                         |    |

| Figure 4.7. N <sub>inv</sub> and N <sub>it</sub> as a function of gate voltage and temperatures        |    |

| Figure 4.8. Mobility and field for 4H-SiC sample                                                       |    |

| Figure 4.9. Mobility scattering vs the temperature at small gate bias                                  |    |

| Figure 4.10. Energy-band diagram of a MOS structure in the inversion condition                         |    |

| Figure 4.11. SiC MOSFET V <sub>TH</sub> measurement and simulation comparison (I <sub>D</sub> = 50 mA) |    |

| Figure 4.12. The curve fitting to measurement at V <sub>GS</sub> =16V                                  |    |

| Figure 4.13. The curve fitting to measurement at 30°C                                                  |    |

| Figure 4.14. Model for k with gate bias and temperatures                                               |    |

| Figure 4.15. The curve fitting to measurement at different temperatures                                |    |

| Figure 4.16. The curve fitting to measurement at different gate bias                                   |    |

| Figure 4.17. On-resistance of VDMOSFET at different drain voltage                                      |    |

| Figure 4.18. Measurement and simulation output characteristic at 30°C                                  |    |

| Figure 4.19. Output characteristic using full model at different temperatures                          |    |

| Figure 4.20. SiC MOSFET output characterization in Saber at temperature of 90°C                        |    |

| Figure 4.21. Output simulation curves and experiments at 90 °C                                         | 92 |

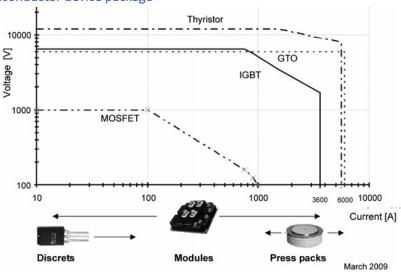

| Figure 5.1. Power range vs package types of power semiconductor device                                 |    |

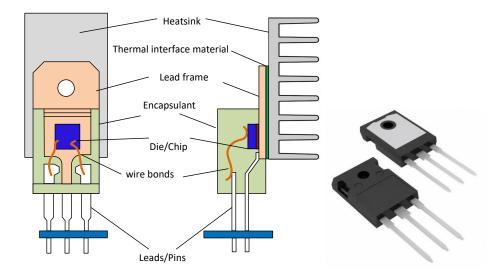

| Figure 5.2. Power discrete device package                                                              |    |

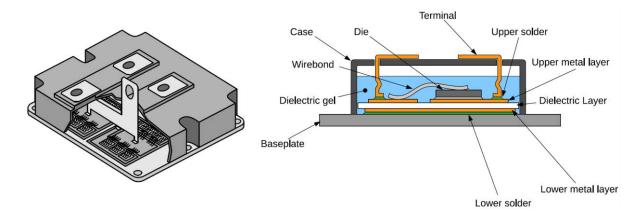

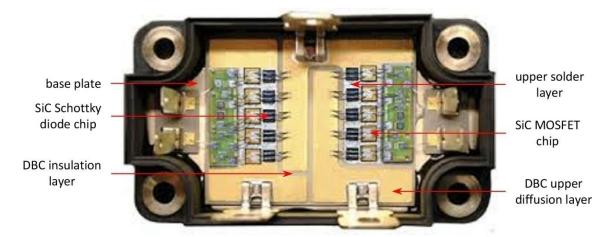

| Figure 5.3. Internal layout of and cross-sectional structure of the module                             | 94 |

| Figure 5.4. Heat transfer mechanisms in power device                                             | 95    |

|--------------------------------------------------------------------------------------------------|-------|

| Figure 5.5. The equivalence between thermal and electrical quantities                            | 97    |

| Figure 5.6. Cross-section layers and Cauer thermal model of semiconductor device                 | 97    |

| Figure 5.7. Foster thermal model of semiconductor device                                         | 98    |

| Figure 5.8. T <sub>j</sub> vs. time for periodic pulse excitation of thermal impedance           | 99    |

| Figure 5.9. The transient thermal response for a single pulse                                    | 101   |

| Figure 5.10. Approximation of $V_{\scriptscriptstyle F}$ and temperature range                   | 102   |

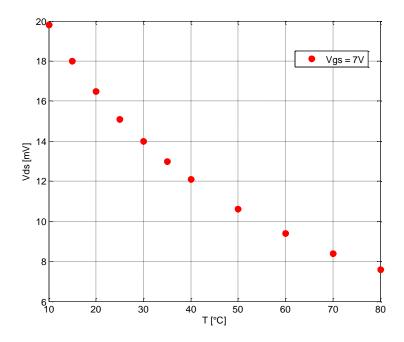

| Figure 5.11. The calibration curves of 1200 V-100 A SiC MOSFET (CAS100H12AM1) at $I_c$ = 1 A     | 104   |

| Figure 5.12. The calibration curves of 1200 V-100 A SiC MOSFET (CAS100H12AM1) at $I_c$ = 100 m   | าA105 |

| Figure 5.13. Multiple junction calibration curves                                                | 106   |

| Figure 5.14. Circuit diagram of the measurement setup                                            | 107   |

| Figure 5.15. Experimental test bench                                                             | 107   |

| Figure 5.16. Time diagram of self-heating measurement method                                     | 109   |

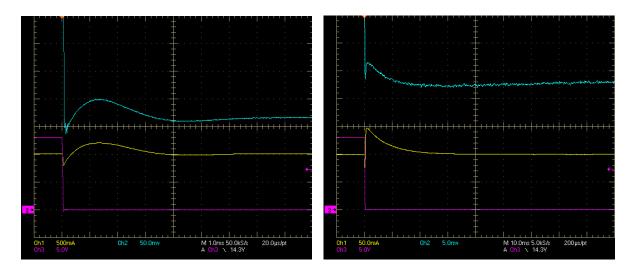

| Figure 5.17. Measured waveforms obtained after the heating switching off                         | 110   |

| Figure 5.18. Measured waveforms obtained for $I_c$ = 1 A at ambient temperature ( $T_a$ = 10 °C) | 111   |

| Figure 5.19. Circuit diagram of thermal coupling measurement                                     | 112   |

| Figure 5.20. Internal top view of the CAS100H12AM1 power module                                  | 114   |

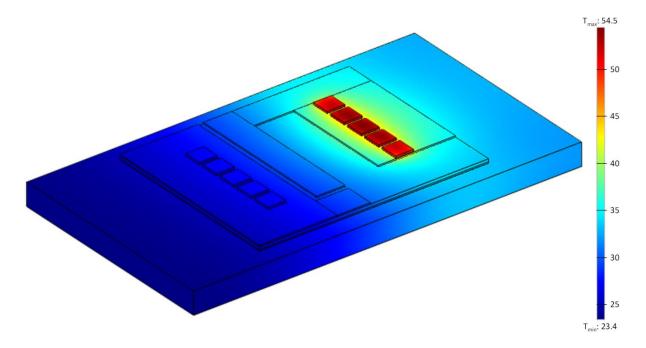

| Figure 5.21. Temperature field of the CAS100H12AM1 module                                        | 115   |

### List of Tables

| Table 1.1. Electrical properties of semiconductors at room temperature          | 13  |

|---------------------------------------------------------------------------------|-----|

| Table 1.2. Measured barrier heights for metal-semiconductor junctions on N-type | 20  |

| Table 2.1. Blocking voltage and N-drift structure                               | 30  |

| Table 2.2. Breakdown occurs in a MOSFET by some effects                         | 40  |

| Table 2.3. Oxide charges and effects                                            | 44  |

| Table 4.1. Threshold voltage parameters                                         | 78  |

| Table 4.2. Extracted value of k                                                 | 82  |

| Table 5.1. Analogy between thermal and electrical phenomena                     | 96  |

| Table 5.2. Data for $I_c$ = 1 A, $T_a$ = 10 °C                                  | 110 |

| Table 5.3. Data for $I_c$ = 100 mA, $T_a$ = 10 °C                               | 110 |

| Table 5.4. Data for I <sub>c</sub> = 1 A, T <sub>a</sub> = 10 °C                | 113 |

| Table 5.5. Experimental and modeling results                                    | 116 |

#### List of Abbreviations and Symbol

N The doping density (cm<sup>-3</sup>)

$N_A$  Acceptor doping concentration (cm<sup>-3</sup>)  $N_D$  Donor doping concentration (cm<sup>-3</sup>) q The electronic charge (1.6 × 10<sup>-19</sup> C)  $K_B$  Boltzmann's constant (1.38066·10<sup>-23</sup> J/K)

T Temperature (°C)

n<sub>i</sub> Intrinsic carrier concentration (cm<sup>-3</sup>)

A Area (cm<sup>2</sup>)

$\begin{array}{ll} C_{OX} & \text{Oxide capacitance (F)} \\ t_{OX} & \text{Oxide thickness (mm)} \\ \text{BJT} & \text{Bipolar junction transistor} \end{array}$

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal oxide semiconductor field effect transistor

JFET Junction Field Effect Transistor

SBD Schottky barrier diodes

D<sub>it</sub> Density of interface traps (cm<sup>-2</sup> eV<sup>-1</sup>) E<sub>BR</sub> Breakdown electric field (MV/cm)

$\begin{array}{lll} E_C & & Conduction band (eV) \\ E_V & & Valence band (eV) \\ E_G & & Energy band gap (eV) \\ E_F & & Fermi level (eV) \\ \chi & & Electron affinity (eV) \\ \Phi_B & & Schottky barrier (eV) \\ \Phi_M & & Metal work function (eV) \end{array}$

$\Phi_{S}$  Semiconductor work function (eV)

$\Phi_{MS}$  Difference between metal and semiconductor work functions (eV)

Surface potential (V) φs Fermi potential (V) Φs Drain-source voltage (V)  $V_{DS}$  $V_{\text{GS}}$ Gate-source voltage (V)  $V_{FR}$ Flat-band voltage (V) Threshold voltage (V)  $V_{\mathsf{TH}}$ Transconductance (S)  $g_{\mathsf{m}}$ Drain-source current (A)  $I_{DS}$

$\begin{array}{lll} I_{DSsat} & Saturation drain-source current (A) \\ L & Length of the MOSFET channel (\mu m) \\ W & Width of the MOSFET channel (\mu m) \\ \epsilon_0 & Vacuum permittivity (8.85 \times 10-14 \ F/cm) \\ \epsilon_S & Dielectric constant of the semiconductor \\ \epsilon_{Si} & Dielectric constant of the silicon (11.7 \times \epsilon_0) \\ \epsilon_{OX} & Dielectric constant of gate oxide (3.97 \times \epsilon_0) \end{array}$

$\mu_e$  Electron mobility (cm<sup>2</sup>/Vs)

| $\mu_p$ Hole mobil | ity ( | [cm <sup>2</sup> /Vs] | ) |

|--------------------|-------|-----------------------|---|

|--------------------|-------|-----------------------|---|

$\begin{array}{ll} \mu_{inv} & \quad \text{Inversion layer mobility (cm}^2/\text{Vs)} \\ \nu & \quad \text{Electron drift mobility (cm/s)} \end{array}$

$\rho \qquad \qquad \text{Resistivity ($\Omega$cm)}$

$\begin{array}{ll} \theta & & \text{Thermal conductivity (W/cmK)} \\ X_D & & \text{Width of drift region (cm)} \end{array}$

W<sub>D</sub> Width of depletion region (cm)

# Introduction générale

#### Contexte de l'étude

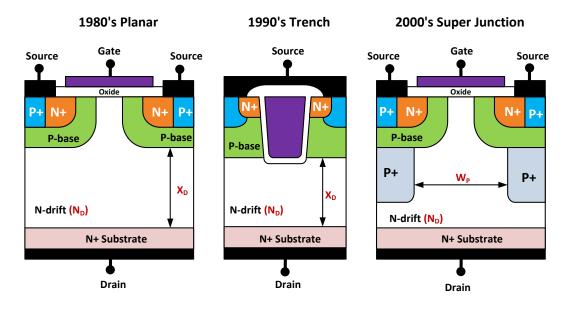

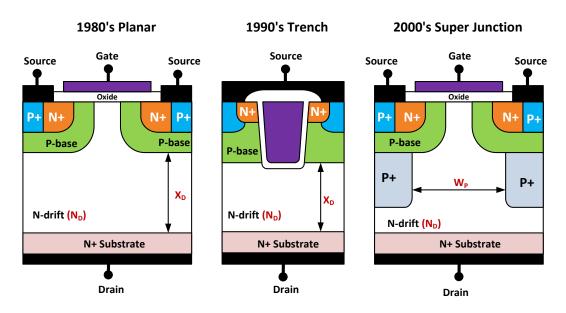

De principe similaire au MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) de signal, le MOSFET de puissance présente une géométrie différente avec une structure verticale où la source et le drain sont placés respectivement au-dessus et en dessous de la matrice de silicium. La première génération de MOSFET de puissance a été commercialisée au début des années 1980 par International Rectifier. Cette technologie, désignée par DMOS, met en œuvre une procédure de fabrication par double diffusion et une grille planaire, elle offre des capacités de blocage jusqu'à 300V. Dans les années 1990 est apparue la structure à grille en tranchée. Connue comme étant la seconde génération de MOSFET de puissance, elle a été commercialisée sous l'appellation TrenchFET par l'entreprise Vishay Siliconix. Le TrenchFET présente une nette supériorité sur le DMOS en terme de résistance à l'état passant et de charge de grille pour les produits spécifiquement en deçà de 100V. La superjonction CoolMOS, désignée comme la troisième génération de MOSFET de puissance, a été mise au point par Siemens (désormais Infineon) en 1999. Celui-ci apporte des avancées considérables par la mise en œuvre d'une nouvelle structure permettant de bloquer des tensions de 600V.

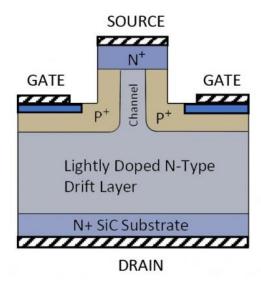

Figure 1. Comparaison des structures MOSFET à grille planaire, à grille en tranchée et superpjonction

Le MOSFET de puissance exhibe plusieurs avantages au premier rang desquels une haute impédance d'entrée, des commutations rapides et un bon rendement (sous l'effet de faible pertes par commutation et par conduction). Ces caractéristiques bénéfiques ont favorisé son introduction en électronique de puissance dans les applications de fréquences allant de 300 kHz à 2 MHz (convertisseurs DC/DC, onduleurs...). Quand bien même la technologie MOSFET de puissance a été en constante amélioration durant 30 ans sur de nombreux aspects, la tenue en tension est néanmoins restée limitée à la plage 100 V à 600 V. Par conséquent, les IGBT (Insulated Gate Bipolar Transistors) représentent l'alternative au MOSFET pour les tensions supérieures à 600 V.

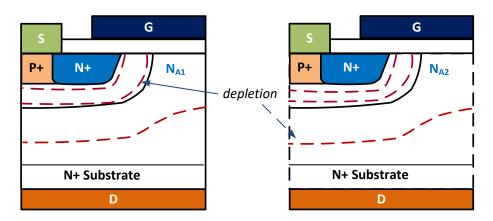

Une vue en coupe des trois générations de MOSFET de puissance est présentée schématiquement en Figure 1, il est clairement observable que la capacité de blocage du composant repose sur la combinaison de deux paramètres de la région épitaxiée N, l'épaisseur ( $X_D$ ) d'une part et le dopage ( $N_D$ ) d'autre part. La résistance spécifique (i.e. résistance par unité de surface)  $R_{ON,sp}$  est quant à elle déterminée pour une certaine tension de claquage  $V_{BR}$  selon l'expression (0-1).  $R_{ON,sp}$  augmente avec  $V_{BR}$  à la puissance 2.4, de là découle un compromis entre tenue en tension et perte à l'état passant, lequel constitue le frein majeur à l'entrée du MOSFET de puissance dans le domaine des hautes tensions. La version superjonction ouvre la voie à un gain substantiel par l'augmentation de la tenue en tension tout en maintenant une résistance à l'état passant raisonnable. La dépendance de  $R_{ON,sp}$  vis-à-vis de  $V_{BR}$  n'étant plus qu'une relation linéaire, il apparaît des bénéfices évidents en termes de pertes à l'état passant.

$$R_{ON,sp} = 8.9 \times 10^{-19} \times V_{BR}^{2.4} \quad (\Omega \cdot cm^2)$$

(0-1)

$$R_{\text{ON,sp(SJ)}} = 0.198 \times W_{\text{P}}^{5/4} \times V_{\text{BR}} \quad (\Omega \cdot \text{cm}^2)$$

(0-2)

Des innovations technologiques tant au niveau de la structure planaire que de la structure superjonction ont permis l'amélioration des performances. Néanmoins le taux d'amélioration du MOSFET de puissance à base de silicium a diminué au fur et à mesure de la convergence vers la valeur théorique.

Le MOSFET de puissance a cependant connu un regain d'attention dernièrement pour les futures applications en électronique de puissance grâce à la mise en œuvre du carbure de silicium (SiC). Combinant les excellentes propriétés du carbure de silicium avec les avantages potentiels du MOSFET, le MOSFET SiC a très nettement dépassé les limites théoriques du MOSFET Si, en atteste sa capacité de blocage de tensions allant de 1.2 kV à 1.7 kV. Le MOSFET SiC de puissance présente une plus faible résistance à l'état passant, des pertes moindres en commutation et des potentialités de fréquence de découpage plus élevées eu égard aux IGBT de calibre en tension équivalent. En tant que composant naturellement ouvert, le MOSFET SiC tout autant que l'IGBT Si peut donc être mis à profit pour la conception de convertisseur d'électronique de puissance.

#### Résultats et contributions essentiels

Quand bien même le MOSFET SiC s'annonce prometteur, il n'est pas encore arrivé à pleine maturité de développement technologique, il soulève encore des inquiétudes en terme de fiabilité et ses performances pratiques n'ont toujours pas rejoint les valeurs théoriques. Les MOSFET SiC et Si sont fabriqués et dimensionnés selon des principes similaires, cependant le MOSFET SiC présente des propriétés comportementales qui lui sont propres. Par conséquent, il est nécessaire d'identifier clairement ces particularités de sorte à tirer le meilleur parti du MOSFET SiC lors de son implémentation dans un environnement d'électronique de puissance. Par ailleurs, la disponibilité d'un modèle précis est de première importance pour réaliser des simulations numériques et des prédictions quelle que soit l'application envisagée. Par conséquent un travail préalable de caractérisation expérimentale et de modélisation est nécessaire et il fait actuellement l'objet de nombreux programmes de recherche aussi bien académiques que de la part des acteurs du secteur industriel.

Le présent document est composé de cinq chapitres traitant respectivement de l'état de l'art sur les composants à large bande interdite, du MOSFET de puissance, de sa caractérisation, de sa modélisation électrique puis thermique. Le détail de chaque chapitre est abordé dans les sections suivantes.

Le chapitre 1 est un état de l'art sur les composants à large bande interdite, il aborde les aspects technologiques des composants à base de carbure de silicium. Le chapitre débute avec les particularités des matériaux à large bande interdite et il souligne les avantages que l'on peut en extraire pour en faire des composants de puissance en électronique de puissance. Ce chapitre montre que les propriétés physiques de ces composants leurs permettent d'opérer à haute température, à tension élevée et à haute fréquence. Pour des raisons économiques et technologiques, les composants SiC ont connu un meilleur essor que leurs homologues GaN. C'est la raison pour laquelle les composants SiC dominent actuellement le marché. Les composants essentiels de l'électronique de puissance sont passés en revue pour dégager les propriétés spécifiques des composants SiC. Les composants unipolaires ont été commercialisés récemment, lesquels exhibent des performances électriques intéressantes avec de faibles pertes par commutation et conduction. Malheureusement les composants SiC rencontrent encore des difficultés technologiques qui limitent leur mise en œuvre dans des systèmes exigeant une fiabilité irréprochable. Eu égard à la métallisation du SiC, la majorité des contacts métal semi-conducteur N sont des contacts Schottky. En outre, il est difficile de concevoir un contact ohmique avec le SiC, en particulier avec les dopages P. Les composants de type MOS à large bande interdite rendent plus basse la barrière que les électrons doivent franchir pour accéder à l'oxyde, ce qui conduit à de sérieuses difficultés en terme de fiabilité pour les applications à haute température.

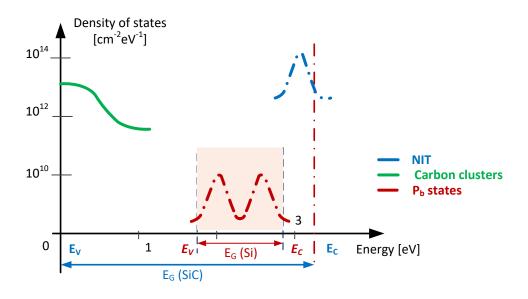

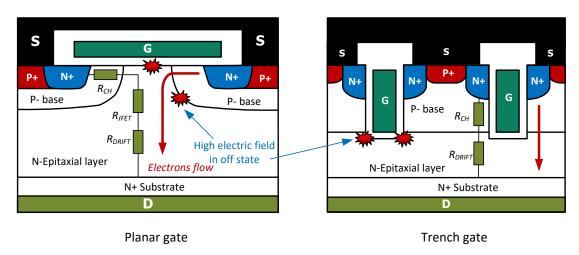

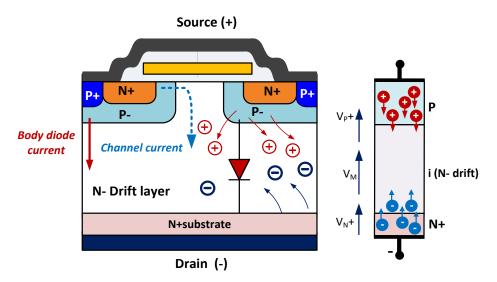

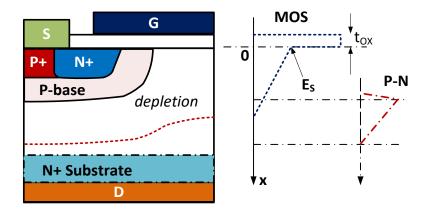

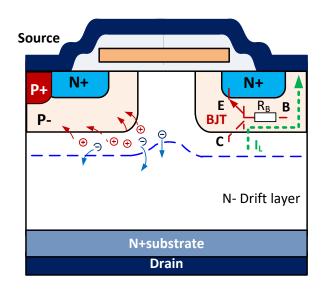

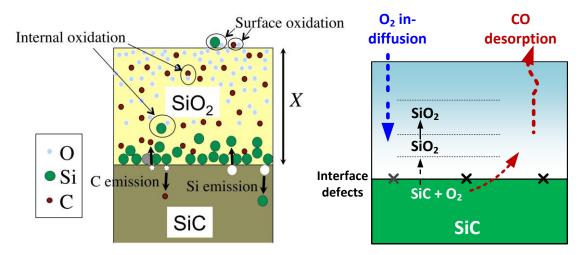

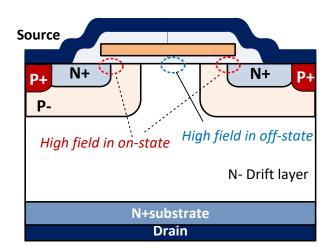

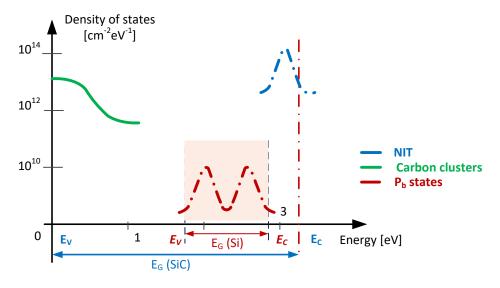

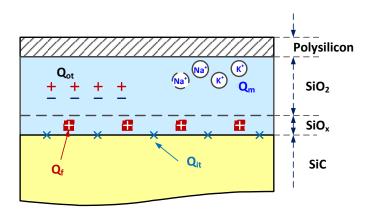

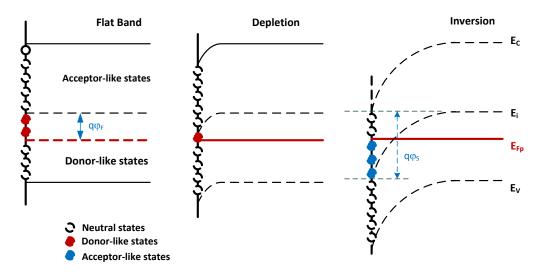

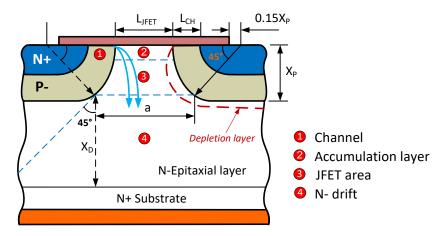

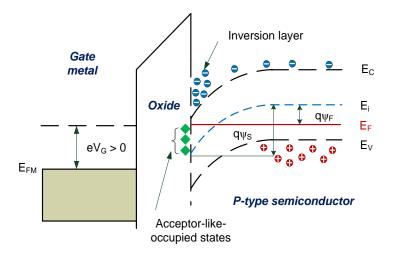

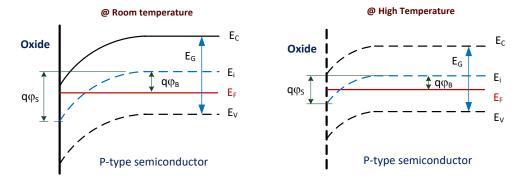

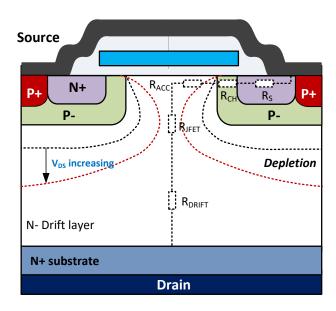

Le chapitre 2 est entièrement dédié au MOSFET de puissance. Il débute par une introduction à la physique et à la structure des deux modèles disponibles sur le marché, en l'occurrence les structures à grille planaire et à grille en tranchée. Le chapitre s'oriente ensuite vers une analyse détaillée des difficultés technologiques propres au MOSFET SiC à double implantation, lesquels présentent un principe d'opération et une procédure de fabrication pourtant similaire à leurs homologues Si. Les caractéristiques statiques aux états fermé et ouvert sont considérés en ce qui concerne la structure à grille planaire. La discussion porte ensuite sur les problèmes liés à l'oxyde de grille SiO<sub>2</sub>. La présence d'atomes de carbone dans le composé SiC induit une interaction entre les entités C, SiC et SiO<sub>2</sub> de façon complexe. La densité de défauts à l'interface semi-conducteur—oxyde de grille (SiC-SiO<sub>2</sub>) a été évaluée à des ordres de grandeur 2 à 3 fois supérieurs à ceux rencontrés dans l'interface SiC-SiO<sub>2</sub>. La densité D<sub>it</sub> en question est composée de trois type de pièges, (centres P<sub>b</sub>, groupes C et pièges de proche interface), elle est représentée sur la Figure 2. En particulier, la plus haute densité de piège est située à seulement 0.1 eV en dessous de la bande de conduction du semi-conducteur 4H-SiC, elle est à l'origine de la capture d'électrons et elle affecte significativement les caractéristiques en conduction du canal d'inversion sous la grille.

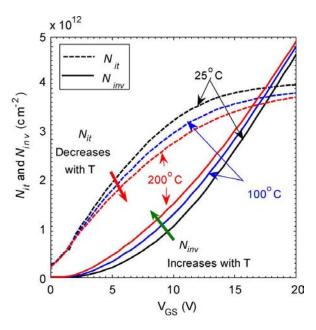

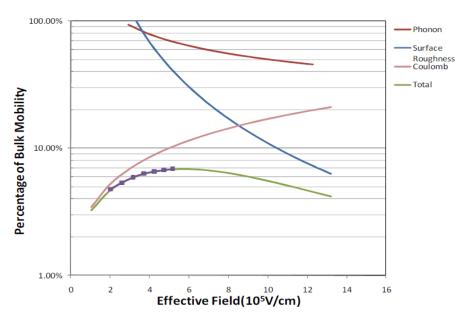

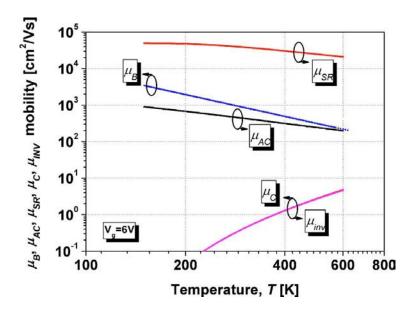

L'occupation des états d'interface, i.e. le nombre de charges piégées, dépend à la fois de la température et de la tension V<sub>GS</sub> appliquée sur la grille. Par conséquent, le nombre de porteurs libres dans le canal, la tension seuil et la mobilité doivent être considérés comme fonction de la température et de la tension V<sub>GS</sub>. Plusieurs clarifications et discussions sont développées dans le chapitre à ce sujet. Des précautions d'usage doivent être respectées pour tirer le meilleur parti des MOSFET SiC, par exemple la tension V<sub>GS</sub> doit atteindre 20V à l'état passant. Il peut malgré tout

subsister des instabilités de la tension seuil et une dégradation de la grille. La diode intrinsèque SiC présente une chute de tension significativement plus élevée que la diode intrinsèque Si, ce qui induit davantage de pertes à l'état passant en fonctionnement inverse malgré d'excellentes caractéristiques en commutation. A cet égard il est vivement recommandé d'employer une diode Schottky en parallèle.

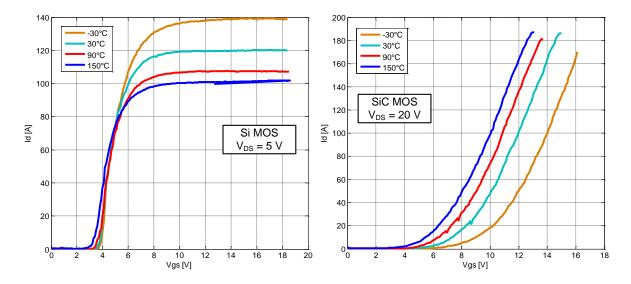

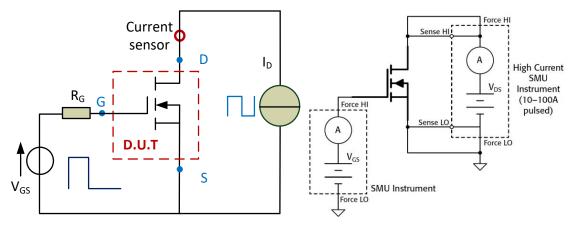

Figure 2. Représentation schématique des niveaux d'énergie en jeu dans l'interface SiC-SiO2

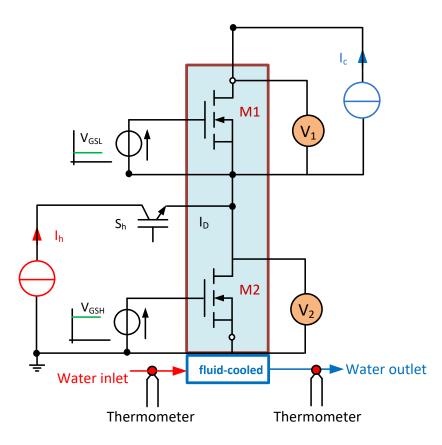

Le chapitre 3 est l'objet d'investigations en terme de caractéristiques statiques sur un composant 100 A – 1.2 kV, l'accent est mis sur les distinctions à observer entre les MOSFET Si et SiC. La température devient un facteur d'influence majeure dans les essais expérimentaux associés car elle affecte l'ensemble des paramètres et par suite le comportement du composant. Pour s'affranchir de cet inconvénient, il a été fait usage d'une enceinte thermique permettant de mettre à température désirée le composant, cette phase dure 12 heures et assure un parfait équilibre thermique du composant. Les composants MOSFET de puissance mettent en jeu des courants tels que l'auto échauffement n'est pas négligeable, c'est pourquoi des procédures expérimentales spécifiques sont requises et elles ont été décrites en détail. Les essais en question ont été réalisés par pas de 10°C de -30°C à 150°C.

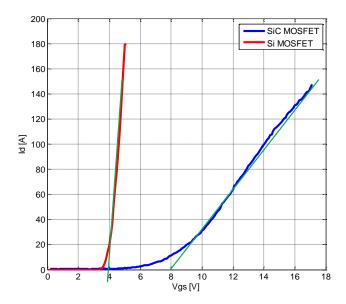

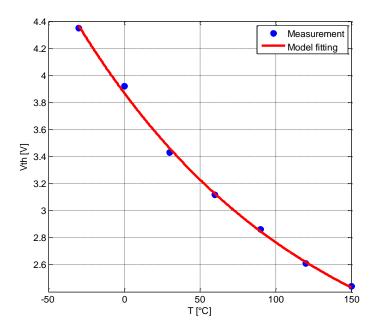

En ce qui concerne la tension seuil  $V_{TH}$ , elle a été mesurée par une méthode à courant constant. A l'instar des MOSFET Si, il a été observé que celle des MOSFET SiC diminue avec la température. Cependant la présence d'états d'interface implique une réduction non linéaire de  $V_{TH}$  avec la température, cette spécificité doit être prise en compte dans le modèle.

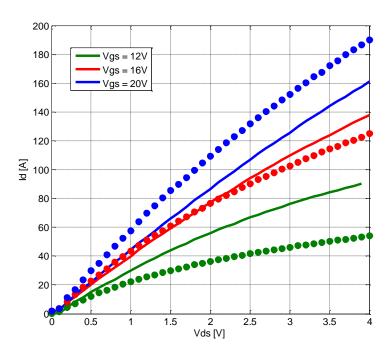

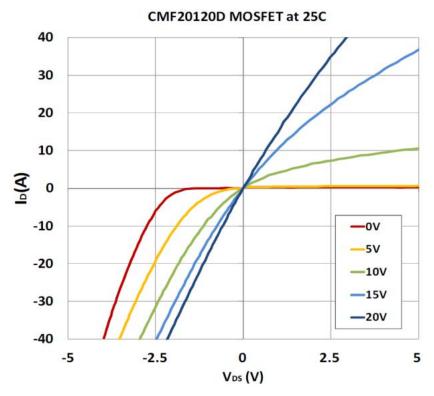

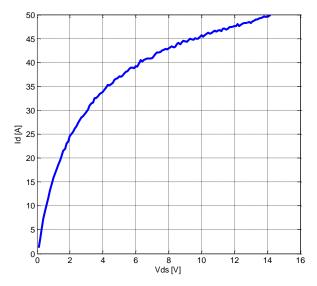

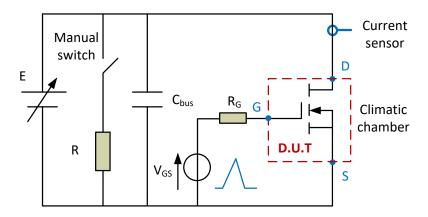

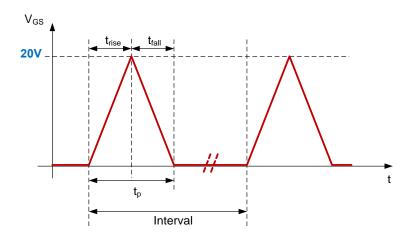

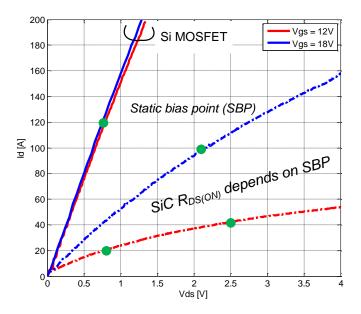

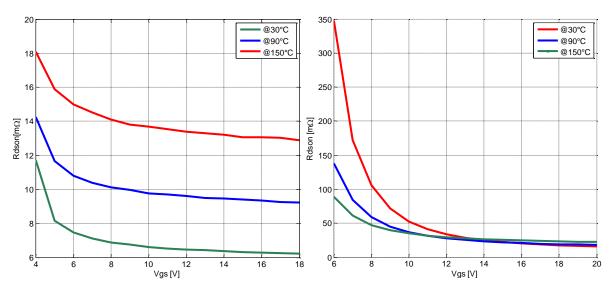

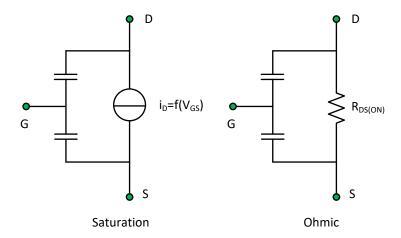

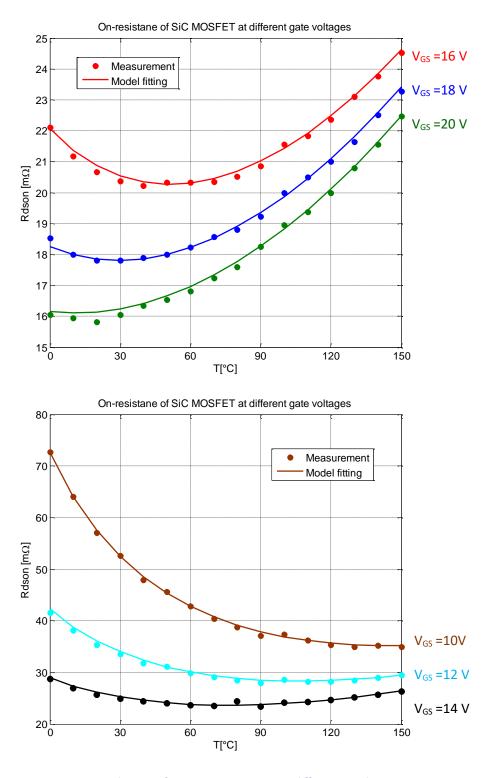

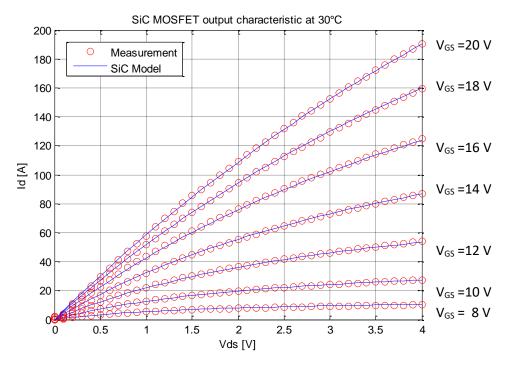

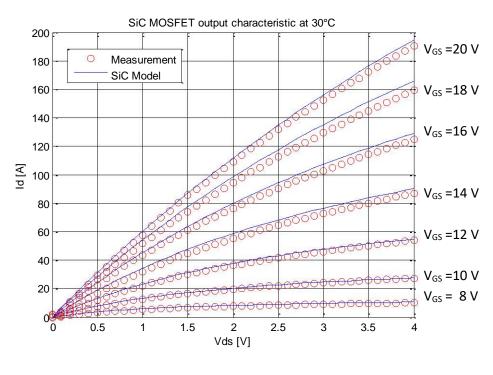

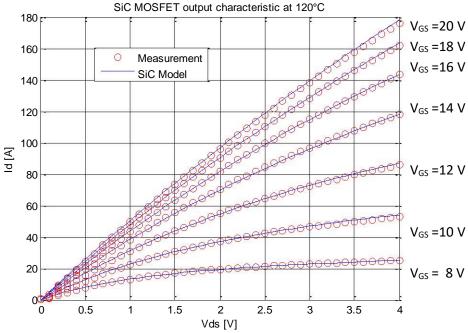

Les caractéristiques courant tension ( $I_D$  vs  $V_{DS}$ ) sont quant à elles obtenues par pulse de largeur 500 µs de sorte à éviter l'auto échauffement. Ces caractéristiques présentent une forte dépendance avec la tension de grille  $V_{GS}$ , ce qui souligne la forte contribution de la résistance de canal ( $R_{ch}$ ) dans la résistance totale à l'état passant. D'ailleurs le comportement thermo-électrique du MOSFET SiC dépend significativement de la tension  $V_{GS}$ , la Figure 3 en est l'illustration. Pour les tensions de grille élevées, par exemple  $V_{GS}$  = 20 V, le courant décroît avec la température. En revanche, pour des tensions de grille plus faibles, par exemple  $V_{GS}$  = 12 V, le courant augmente avec la température. Il convient de garder à l'esprit ce comportement particulier vis-à-vis de la stabilité thermique d'un

composants MOSFET d'une part, et de la distribution du courant sur plusieurs MOSFET connectés en parallèle d'autre part.

Figure 3. Caractéristique de sortie du MOSFET SiC 100A-1.2kV à 30°C (courbe continue) et à 150°C (courbe discontinue)

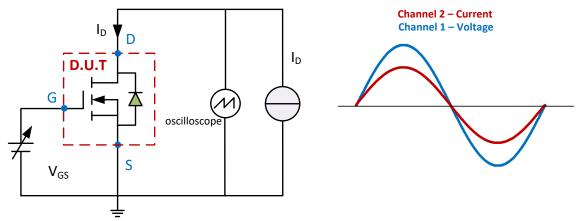

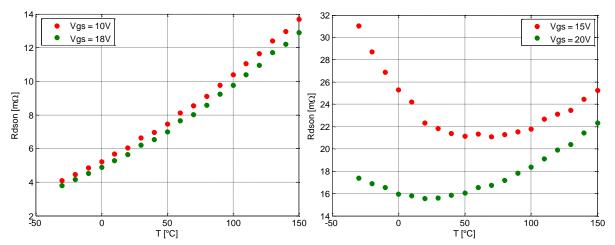

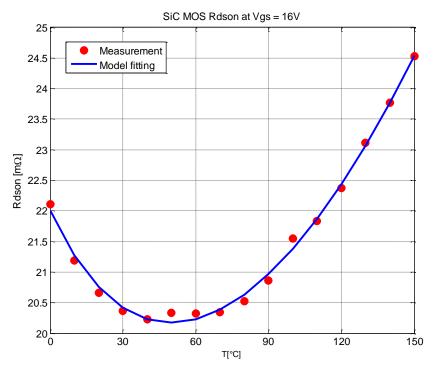

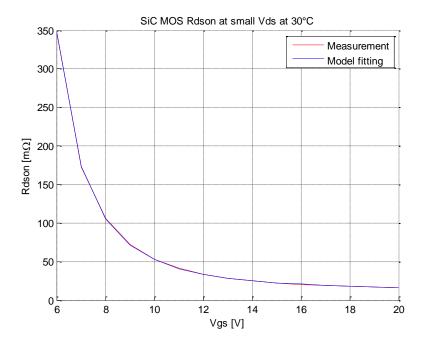

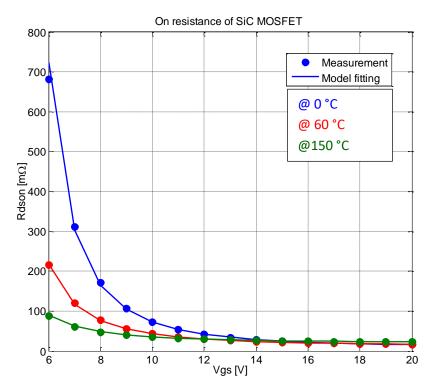

La résistance à l'état passant R<sub>DS(ON)</sub> a également été quantifiée et le rôle joué par la résistance de canal a été examiné. Pour éviter les problèmes d'auto échauffement ces recherches ont été menées par le biais de la spectroscopie d'impédance à 0 A. Les résultats ont permis d'identifier R<sub>DS(ON)</sub> comme un sérieux candidat en tant que paramètre électronique thermo-sensible (TSEP) en vue d'estimer la température de jonction du transistor. Suite à cette étude, les conditions optimales ont été identifiées, en l'occurrence l'application d'une faible tension de grille V<sub>GS</sub> pour améliorer la sensibilité de R<sub>ON</sub> vis-à-vis de la température. De plus amples détails sont fournis dans le chapitre 5.

Le chapitre 4 propose un nouveau modèle compact sur la base des résultats de caractérisation expérimentaux, lequel prend en compte les divers phénomènes physiques impliqués dans le fonctionnement du MOSFET SiC. L'influence des pièges d'interface est traitée en détail. Après avoir commenté les principaux modèles existants dans la littérature, le modèle proposé est développé et les paramètres intervenants sont déterminés par moindres carrés.

$$I_{D} = k_{(V_{GS},T)} \times \left[ (V_{GS} - V_{TH}) - \frac{\alpha}{2} \times \frac{a_{(V_{GS},T)} \times V_{DS}}{V_{DS} + b_{(V_{GS},T)}} \right] \times \frac{a_{(V_{GS},T)} \times V_{DS}}{V_{DS} + b_{(V_{GS},T)}}$$

(0-3)

Un modèle simplifié est mis en œuvre sur la base de la relation (0-3), lequel intègre l'effet des états d'interface par le biais du paramètre k, ainsi que la faible longueur du canal par le biais du facteur  $\alpha$ . Pour une tension de grille  $V_{GS}$  donnée, le courant de drain  $I_D$  augmente avec  $V_{DS}$ , et il tend progressivement vers l'état saturé. Ce comportement se traduit par le contrôle de la tension de canal  $V_{CH}$  au travers des paramètres a et b dans l'expression de  $I_D$ . Par conséquent les mécanismes de saturation du MOSFET SiC apparaissant dans la région dite JFET sont également pris en compte. La

dépendance thermo-électrique a également été traitée, incluant son effet sur la tension seuil, sur la mobilité dans la couche d'inversion, sur la résistance de drift et sur la résistance de canal.

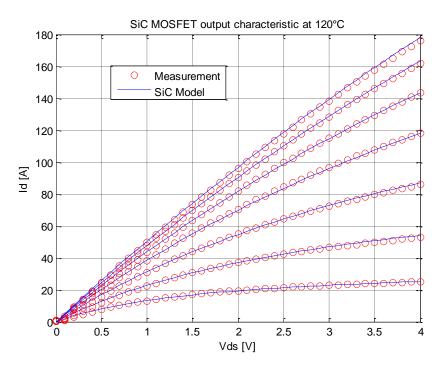

Le chapitre commence par traité les effets des états d'interface sur la tension seuil. Une loi polynomiale est mise en œuvre pour en rendre compte. Le chapitre se poursuit par la modélisation du gain en courant k sur la base des essais expérimentaux sur  $R_{ON}$  à OA. Celui-ci est représenté par une relation spécifiant son évolution avec deux paramètres, la tension de grille  $V_{GS}$  et la température. Enfin les paramètres a et b sont déterminés de sorte à corroborer l'ensemble des caractéristiques  $I_D$  vs  $V_{DS}$  expérimentales.

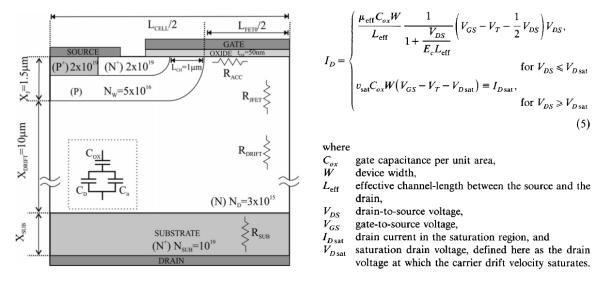

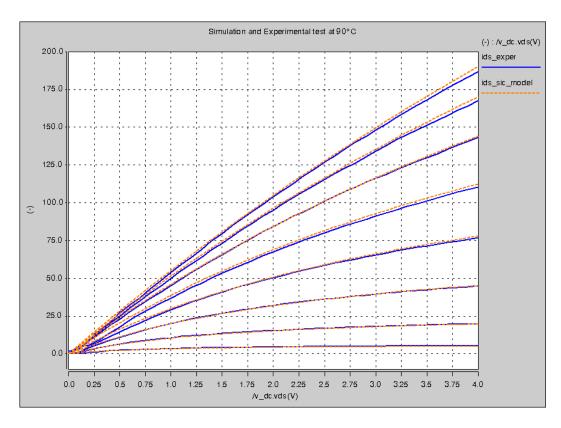

Figure 4. Caractéristiques I<sub>D</sub> vs V<sub>DS</sub>, comparaison du modèle (lignes) et des essais expérimentaux (cercles) à 120°C

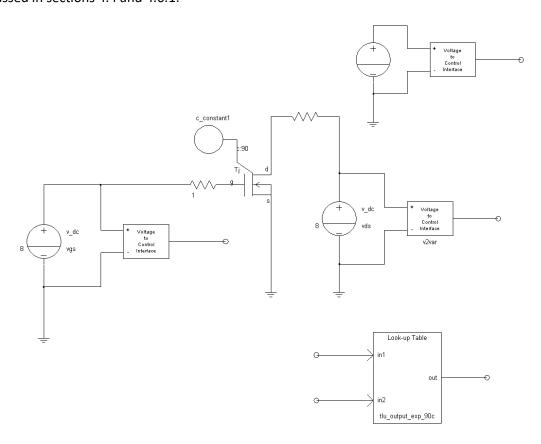

Les quatre paramètres (k,  $\alpha$ , a and b) nécessaires à ce modèle compact ont été extraits et le modèle se conforme bien au comportement expérimental, la figure 4 l'atteste. La procédure d'extraction des paramètres repose sur la mise en œuvre d'une outil d'optimisation du logiciel Matlab. Le modèle a également été implanté sur le logiciel SABER, lequel modèle prédit correctement le comportement du MOSFET pour divers modes d'opération.

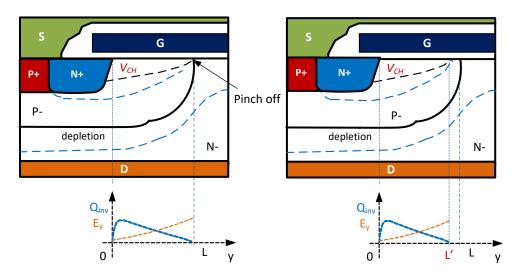

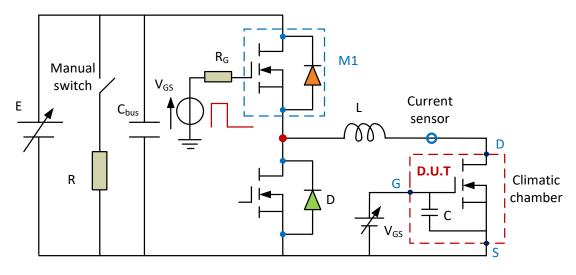

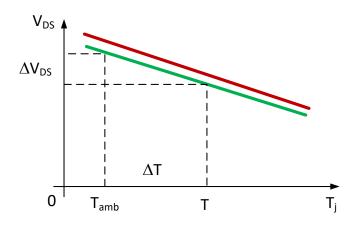

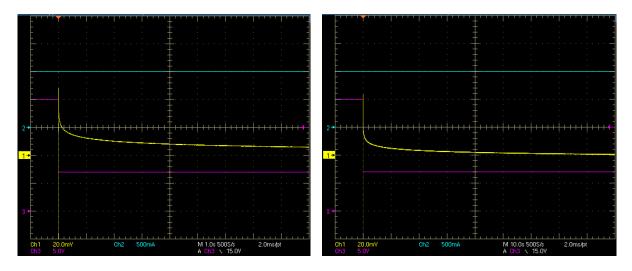

Le chapitre 5 est consacré à la caractérisation et à la modélisation thermique. La mesure de la résistance thermique requière la mise en œuvre d'un TSEP pour estimer la température de jonction. La méthode retenue repose sur la mesure d'un paramètre électrique du transistor qui évolue avec la température, en l'espèce la résistance à l'état passant  $R_{ON}$ . La méthode proposée comporte deux étapes, la calibration du TSEP d'une part, et l'enregistrement de la température au cours d'un cycle de dissipation de puissance d'autre part. La phase de calibration consiste à déterminer la relation entre la tension  $V_{DS}$  (ou la résistance  $R_{DSON}$ ) et la température de jonction. Nous avons montré qu'il est nécessaire d'appliquer un faible courant de calibration ( $I_C = 1$  A ou 100 mA) pour éviter l'autoéchauffement et qu'il convient d'imposer une faible tension de grille ( $V_{GS} = 7$  V) pour accroître la sensibilité. Nous avons expliqué comment éviter d'une partie des effets indésirables des états d'interfaces.

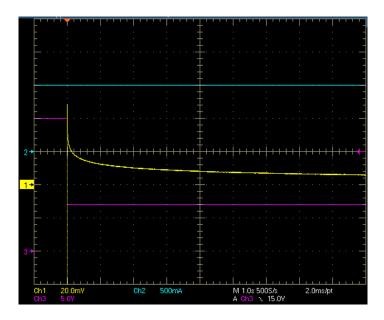

Figure 5. Formes d'ondes obtenues avec  $I_c$  = 1 A à 10°C au cours d'une transition de la tension de 20V à 7V.

Cependant, nous n'avons pas été en mesure de nous en affranchir complétement. La Figure 5 en est l'illustration, on y observe les formes d'ondes obtenues après la commutation de la tension de grille de 20 V à 7 V, le composant sous test étant parcouru par un courant constant. Il apparaît une forte surtension (40 mV) et un long transitoire (100 s) sur la tension V<sub>DS</sub> qui rend la mesure de température inexploitable. C'est pourquoi nous nous sommes alors tournés vers l'estimation non pas de la résistance thermique propre mais de la résistance thermique mutuelle. Avec bien plus de succès, nous avons développé une méthodologie et validé les résultats expérimentaux par le biais d'une modélisation tridimensionnelle par éléments finis sur le logiciel COMSOL. En outre, le modèle électrique développé dans le chapitre 4 voit sa précision confirmée en recoupant avec les essais thermiques du chapitre 5.

Les conclusions des travaux de recherche menés sont dressées et des propositions d'investigations futures sont également suggérées dans une dernière section.

## **General Introduction**

#### **Background**

Owing the same operation principle with its low power counterpart, the power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) has a modified geometry with a vertical structure where the source and drain electrodes are placed at the front and backside of silicon die. The first generation of power MOSFETs was commercially introduced into the market the early 1980s by International Rectifier. This technology uses the double-diffusion process with a planar gate structure, known as DMOS, offers the blocking voltage capability up to 300 V. In the 1990s, a vertical trench gate MOSFET structure, commercialized as TrenchFET®, was introduced by Vishay Siliconix as the second generation of power MOSFET. TrenchFET exhibits a clear superiority over DMOS in terms of on-resistance and gate charge for specific products lower than 100 V. The super-junction (SJ) CoolMOS®, also known as the third generation of power MOSFETs, was released by Siemens (Infineon now) in 1999s. The power SJ MOSFET breaks the limit line of silicon, employing a novel drain structure which adopts mainly for 600 V products.

Figure 6. Planar, trench and super-junction MOSFET unit cell comparison

The power MOSFETs have several distinct advantages including high input impedance, fast switching speed and high efficiency (low switching losses, low on-resistance). Thus, they have been widely used in high frequency (300 kHz to 2.0 MHz, or more) power electronics applications such as switch-mode power supplies (SMPS), DC to DC converters, and motor controllers. Although power MOSFET technology has been ceaselessly improved for over 30 years to satisfactorily serve many segments, they have been limited at voltage ranges from 100 V to 600 V. Consequently, IGBTs (Insulated Gate Bipolar Transistors) are primarily used as alternatives to MOSFETs for medium-to-high power applications above 600 V.

As shown in Figure 6, for conventional MOSFET, the voltage blocking capability of device is determined through the combination of thickness  $(X_D)$  and doping  $(N_D)$  of N-type epitaxial region. The specific on-resistance (on-resistance per unit area)  $R_{ON,sp}$  is determined for a given breakdown voltage

$V_{BR}$ , referred to "silicon limit", as expressed in equation (0-4).  $R_{ON,sp}$  increases approximately by the 2.4th power of the  $V_{BR}$ , which is a barrier to the inroads of power MOSFET in the high voltage arena. The SJ structure technology allows power MOSFET with substantial increasing of the blocking voltage while maintaining the low on-resistance. The great reduction of on-resistance offers obvious conduction loss benefits compared to conventional structure that creates new limit for vertical MOSFET as equation (0-5).

$$R_{\text{ON,sp}} = 8.9 \times 10^{-19} \times V_{\text{BR}}^{2.4} \quad (\Omega \cdot \text{cm}^2)$$

(0-4)

$$R_{\text{ON,sp(SJ)}} = 0.198 \times W_{\text{p}}^{5/4} \times V_{\text{BR}} \quad \left(\Omega \cdot \text{cm}^2\right)$$

(0-5)

The performance improvements have been witnessed with technology innovations from planar gate to trench gate and today's super-junction structure. However, the rate of improvement of the silicon-based power MOSFET has been slowed when they have asymptotically approached its theoretical maturity.

Recently, power MOSFETs with silicon carbide (SiC) technology have gained more attention as the promising devices for next-generation power electronics applications. Combining the excellent properties of SiC material with the potential advantages of MOSFET, SiC MOSFETs have far exceeded the theoretical limit of Si power counterparts to enter the medium applications in particular 1.2 kV - 1.7 kV voltage range. SiC MOSFETs exhibit lower on-resistance, lower switching loss, and higher frequency operation in compared with IGBTs at the similar voltage rating. SiC MOSFETs have the further major advantage of satisfactory operation at high temperatures. As normally-off and voltage-controlled device, designers can greatly leverage the design experience using Si MOSFETs and IGBTs. Thus, SiC MOSFETs are foreseen to replace Si IGBTs for emerging applications.

#### Outline of this work

Although promising, but being at a relatively immature technology, SiC MOSFETs have their own list of concerns that had slowed down their performance and reliability far from the theoretical potential of material. SiC MOSFETs are designed and essentially processed the same way of their Si counterparts. However, they exhibit quite different characteristics. Thus, understanding of the unique operating characteristics and their effects in design are required to fully utilize the advantages of SiC MOSFETs. The accurate device models are also needed in the circuit simulators to evaluate the potential utilization of SiC MOSFETs in different applications. Consequently, the characterization and modeling of SiC MOSFETs have received a great deal of attention from the aspect of power circuit and system designers.

The PhD dissertation is composed of 5 chapters dealing with the characterization and modeling of SiC MOSFETs. Details regarding the approach taken to achieve these goals and the results of the research are discussed in the following chapters.

Chapter 1 describes the background information about WBG materials and power devices. This chapter is presented starting from unique WBG materials properties to their advantages in power devices. Some key components in power electronic systems (power diodes and switches) are reviewed to emphasize distinctive characteristics of SiC devices.

Chapter 2 is entirely dedicated to SiC power MOSFETs. The chapter presents a detailed analysis of the technological problems of SiC MOSFETs double-implanted MOSFET (DiMOSFET) that have the same operating principle and manufacturing process as their counterpart's Si MOSFETs. It begins with the introduction of physics and device structures of the SiC MOSFET. Afterwards, the static characteristics including on-state and blocking mode are considered. A detail regarding the physics of SiC MOS-based devices with emphasis on gate oxide growth concerns is discussed in this chapter. Finally, a review of the SiC MOSFET technical issues related to interface charge traps is also presented.

Chapter 3 investigates the SiC MOSFET characterization where the difference of the characteristics between SiC and Si power MOSFETs is also discussed and clarified. The measurement setups are presented to characterize the device at different temperatures ranging from -30° to 150 °C. The threshold voltage and I-V characteristics are measured to identify the temperature dependence on the device performance. The static on-resistance is quantified, and the role of channel resistance is further investigated by impedance spectroscopy method.

Chapter 4 deals with the development of a new compact model, accounting for various physical phenomena of SiC MOSFET. The influence of interface trap on developing 4H-SiC MOSFET model is discussed in detail. For high voltage SiC MOSFET modeling, the existing works are then reviewed. The proposed model with a single set of equations is investigated that accurately predicts the device operation in variety of operating modes. The model parameters are extracted using fitting techniques by comparison the simulation to experimental results. The implementation of the model into Saber is also described.

Chapter 5 focuses on the thermal characterization of the power SiC MOSFET using thermal sensitive electrical parameter (TSEP). The fundamental theories for the thermal analysis of packaged semiconductor devices are presented. The TSEP for the SiC MOSFET has been identified. Due to the interface traps affects, a modified thermal resistance measurement is developed for the SiC MOSFET thermal characterization. From the measured results, the thermal distribution for the packaged SiC MOSFET using 3D finite element (FEM) method is carried out. The extracted results from the 3D FEM model are used in electrical model to validate the proposed device model with experiments.

The main conclusions of this dissertation and potential future work are presented at last section.

# Chapter 1 Fundamentals of wide band gap power devices

#### 1.1. Background

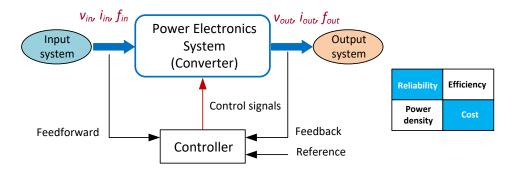

Power electronics is the application of solid-state electronic components to control and convert electrical power from the available input forms into the desired electrical output forms. As illustrated in Figure 1.1, the converters are constructed with semiconductor devices, passive components and control devices into different circuit topologies, to connect and control the power between two systems in the proper, reliable, and efficient manner. The power electronics has recently emerged as a complex and multidisciplinary technology, mainly concerning the field of semiconductor devices, converter configurations, and control techniques.

Figure 1.1. Power electronics system structure

With the widespread adoption of converters in many applications, the power electronics has already been anticipated to be a significant impact for efficient using and reducing overall energy consumption. As the intermediate stage, deployment of advanced power electronics in four major applications (buildings and lighting, power supplies, smart electricity grid, and industrial drives) can reduce the current electricity consumption in European Union by 25% [1].

As the heart of any power electronics converter, power semiconductor is the key in determining the efficiency of the conversion system. By far, silicon has been the predominant semiconductor used by most power electronics systems. However, the maturity in material, device and system has nearly reached the highest possible performance. Hence, the Si-based power devices fail to offer the cost and performance ratio to power efficient, especially for emerging applications with the stringent requirements (more compact, lower weight, higher temperature, and higher power density). Accordingly, new materials and devices structures are needed to fill this performance gap.

WBG semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) allow new power semiconductor devices for greater efficiency, smaller size, and lighter weight. Moreover, the new devices can operate at higher voltages, temperatures, and frequencies, which help significantly to reduce volume, decrease cooling requirements and passive components, contributing to overall efficiency of systems [2-4].

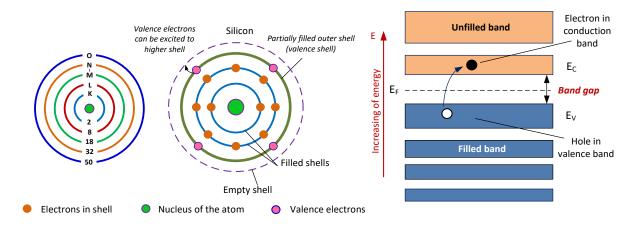

#### 1.2. Band gap energy

As illustrated in Figure 1.2, the electrons in the outermost shell of an atom are known as valence electrons which occupy series of energy levels within an energy band, referred as valence band  $E_V$ . The band above the  $E_V$  is denoted the conduction band  $E_C$  where electrons can move freely, enabling the flow of electricity. It should be noted that the bands below the  $E_V$  are normally completely filled and play no part in the conduction process. Hence, it is sufficient to consider only valence and conduction bands while discussing the electrical properties.

Figure 1.2. Orbital model of some atoms and simplified energy band diagram

The band gap  $E_G$  (eV) relates to the amount of energy required to promote an electron from the top of the  $E_V$  to the bottom of the  $E_C$  to serve as free charge carrier participating in current conduction. The band gap is a major factor to determine the electrical conductivity of substances. The materials with large  $E_G$  are referred as insulators, whereas conductors either have very small or none  $E_G$ . Most of the conventional semiconductors have band gap in the range 1-1.5 eV, whereas WBG materials are so-called due to a relatively high  $E_G$  in the range of 2-4 eV. In the case of diamond (C), though band gap of 5.5 eV is technically considered as insulator, it exhibits actually the ultimate semiconductor.

The band gap decreases slightly with temperature and introduction of impurities. It can be expressed for Si and other semiconductors in the form [5-7]:

$$E_{G}(T) = E_{G}(0) - \frac{\alpha \cdot T^{2}}{T + \beta}$$

(1-1)

$$\Delta E_{G}(N) = -\frac{3q^{2}}{16\pi\varepsilon_{s}} \cdot \sqrt{\frac{q^{2}N}{\varepsilon_{s}K_{B}T}}$$

(1-2)

where  $E_G(0)$  is the value of the band gap at 0 K,  $\alpha$  and  $\beta$  are constants chosen to obtain the best fit to experimental data.  $K_B$  is the Boltzmann constant; T is the absolute temperature. N is the doping concentration, q is the electronic charge,  $\epsilon_s$  is the dielectric constant of the semiconductor. The band gap narrowing is proportional to the square root of the doping concentration. From this expression, it can be found that the band gap shrinkage could typically be ignored for doping less than  $10^{18}$  cm<sup>-3</sup>.

#### 1.3. Electric characteristics of wide band gap semiconductors

The popular WBG materials in use today are compound semiconductors SiC and GaN. Among many different crystal structures (often referred as polytypes), 3C-SiC, 4H-SiC, and 6H-SiC are the most common SiC polytypes used for semiconductor applications. The characteristics for the most popular WBG semiconductors are shown in Table 1.1 and are explained in the following sections.

| Material                                                    | Diamond               | GaN                   | 4H-SiC               | 6H-SiC               | 3C-SiC                | GaAs                 | Si                   |

|-------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|-----------------------|----------------------|----------------------|

| Band gap E <sub>G</sub> (eV)                                | 5.45                  | 3.39                  | 3.26                 | 3                    | 2.2                   | 1.4                  | 1.1                  |

| Electron mobility $\mu_e$ (cm <sup>2</sup> /V·s)            | 2200                  | 1200                  | 850                  | 800                  | 900                   | 8500                 | 1400                 |

| Hole mobility $\mu_h$ (cm <sup>2</sup> /V·s)                | 1600                  | 150                   | 115                  | 90                   | 40                    | 400                  | 600                  |

| Breakdown electric field strength EBR (MV/cm)               | 10                    | 3.3                   | 2.5                  | 2.8                  | 1.2                   | 0.4                  | 0.3                  |

| Saturation velocity v <sub>sat</sub> (10 <sup>7</sup> cm/s) | 2.7                   | 2.7                   | 2.2                  | 1.9                  | 2                     | 2                    | 1                    |

| Intrinsic carrier concentration $n_i$ (cm <sup>-3</sup> )   | 1.6×10 <sup>-27</sup> | 1.9×10 <sup>-10</sup> | 8.2×10 <sup>-9</sup> | 2.3×10 <sup>-6</sup> | 6.9×10 <sup>-10</sup> | 1.8×10 <sup>-6</sup> | 1.5×10 <sup>10</sup> |

| Thermal conductivity $\lambda$ (W/cm·K)                     | 20                    | 2                     | 4.9                  | 4.9                  | 4.9                   | 0.5                  | 1.5                  |

| Dielectric constant ε                                       | 5.5                   | 9                     | 9.7                  | 9.7                  | 9.7                   | 12.8                 | 11.8                 |

| Bulk growth of substrate                                    | In                    | Difficult             | Available            | Available            | Difficult             | Easily               | Easily               |

|                                                             | research              | to obtain             |                      |                      | to obtain             | obtain               | obtain               |

| Direct/Indirect                                             | I                     | D                     | I                    | I                    | I                     | D                    | I                    |

Table 1.1. Electrical properties of semiconductors at room temperature [3, 4]

#### 1.3.1. Wide band gap energy and low intrinsic carrier concentration

An electron skips into the  $E_C$  and simultaneously leaves an empty space (hole) in the  $E_V$ . Thus,  $n_i$  intrinsic carrier concentration refers to either the electron in  $E_C$  or hole concentration in  $E_V$  in intrinsic materials. It exponentially decreases with the  $E_G$ , and increases with temperature [7]:

$$n_{i} = A \cdot T^{3/2} \cdot exp\left(-\frac{E_{G}}{2 \cdot K_{B} \cdot T}\right)$$

(1-3)

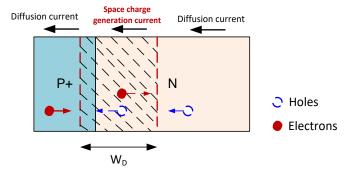

where A is a constant of material. The wider band gap makes an electron more difficult to cross the band gap. Fewer electrons crossing the gap translate to higher operation temperature and smaller leakage current [8]. In practical devices, for an abrupt  $P^+$ -N junction ( $N_A >> N_D$ ), the undesired junction reverse-bias leakage current can be expressed as [6, 7]:

$$j_{leakage} = j_s + j_{sc} = q \cdot \left( \frac{n_i^2}{N_D} \cdot \frac{L_p}{\tau_p} + \frac{n_i}{\tau_g} \cdot \sqrt{\frac{2 \cdot \epsilon \cdot (V_{bi} + V_r)}{q \cdot N_D}} \right)$$

(1-4)

where  $j_s$  is the minority carrier diffusion current density,  $j_{sc}$  the reverse current density generated in the depletion region (the space-charge generation).  $L_p$ ,  $\tau_p$  is diffusion length and lifetime of hole, respectively.  $\tau_g$  is the generation lifetime in the depletion region.  $V_{bi}$  is built-in voltage of the depletion.  $V_r$  is reversed voltage. It can be seen from the equation (1-4), the  $j_s$  is proportional to  $n_i^2$ , whereas the  $j_{sc}$  increases only linear with  $n_i$ . Particularly, the  $n_i$  for 4H-SiC is approximately  $8.2\times10^9$  cm<sup>-3</sup>, which is smaller by the order of  $10^{-18}$  compared to Si. Hence the leakage current is much small with WBG materials.

Depending upon the specific device, the smallest doped region of a semiconductor device is usually between  $10^{14}$  and  $10^{17}$  cm<sup>-3</sup>, thus, intrinsic carriers are negligible. In operating temperature range,

the conduction is controlled by the extrinsic dopant density. However, the  $n_i$  increases exponentially with temperature by the equation (1-3). When  $n_i$  reaches a value comparable with  $N_D$  in the equation (1-4), the P-N structure begins to be leveled out due to large leakage current. In theory, to keep  $n_i$  below  $N_D$ , the temperature must remain below about 190 °C for Si, about 800 °C for 4H-SiC [6].

Due to the larger band gap, WBG has a lower intrinsic carrier concentration, which allows the device to operate at higher temperatures without suffering from excessive leakage.

#### 1.3.2. High breakdown electric field

In most power devices, the reverse-bias voltage is supported within a depletion layer formed across a lightly doped P–N junction where avalanche breakdown is dominant.

Figure 1.3. Leakage current in a PN junction

As mentioned above, the leakage current is due to the space-charge generation or diffusion. Since the minority carriers enter the depletion layer, they are swept out by the electric field as shown in Figure 1.3. At high reverse voltage, the electric field in the depletion region increases, resulting in acceleration of the carriers to higher velocities. The carriers gain sufficient energies for creating additional electron-hole pairs via collisions with bound electrons, is referred to as the impact ionization. As the new carriers are swept into the depletion region, they too are accelerated. The process for the creation of further pairs of electron and hole repeats itself. Consequently, due to the carriers being transported through the depletion region, the leakage current rapidly increases, leading to an avalanche breakdown [3]. In device design, the onset of avalanche breakdown occurs when the electric field within the depletion approaches the critical electric field, as referred to breakdown electric field strength (EBR) [7, 9].

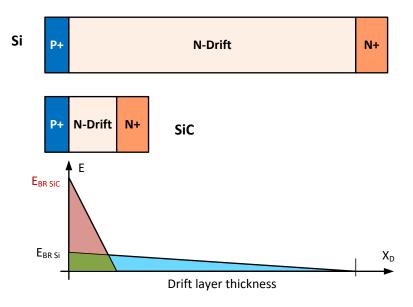

In a non-punch through PN junction, the low doped region N-drift is thick enough to accommodate the depletion. The electric field profile is then triangular as shown in Figure 1.4. E<sub>BR</sub> is used to determine the blocking voltage capability according to [17]:

$$V_{BR} = \frac{\varepsilon_{s} \cdot E_{BR}^{2}}{2 \cdot q \cdot N_{D}}$$

(1-5)

Particularly, the  $E_{BR}$  is about 10 times higher for SiC than for Si. Therefore, SiC devices have 100 times greater in  $V_{BR}$  than the one of a Si device for the same doping ( $N_D$ ). For the same blocking voltage, the SiC device can be structured with a 10 times thinner drift thickness ( $X_D$ ). The specific on-resistance  $R_{ON,sp}$  of the drift region is calculated, as [7]:

$$X_{D} = \frac{2 \cdot V_{BR}}{E_{RR}} \tag{1-6}$$

$$R_{ON,sp} = \frac{4 \cdot V_{BR}^2}{\varepsilon_s \cdot \mu_e \cdot E_{BR}^3} = \frac{X_D}{q \cdot \mu_e \cdot N_D}$$

(1-7)

$R_{ON,sp}$  varies as the square of the  $V_{BR}$  voltage, and is inversely proportional to the cube of  $E_{BR}$ . Thus,  $R_{ON,sp}$  of 4H-SiC drift theoretically gets 500 times smaller than comparable Si devices.

Figure 1.4. Electric field in an abrupt one-sided PN junction

From power device perspectives, the high critical field strength allows WBG devices operate at much higher breakdown voltages than Si-based devices. For a given blocking voltage, SiC devices are structured with a thinner drift layer with more heavily doped than Si, thereby reducing the on-state resistance as illustrated in Figure 1.4.

#### 1.3.3. Other properties

#### High thermal conductivity

Higher thermal conductivity, the lower the thermal resistance (the thermal resistance will be further investigated in the chapter 5) and easier to bring heat out of the junction to the environment, allows for increased power densities of device. Especially for high voltage devices, a thick drift layer can result in a high thermal resistance.

Indeed, SiC is an excellent thermal conductor with thermal conductivity  $\lambda$  (4H-SiC: 3.3 W.cm<sup>-1</sup>.K<sup>-1</sup>), close to Cu (3.97 W.cm<sup>-1</sup>.K<sup>-1</sup>). Thus, high thermal conductivity would make SiC a superior semiconductor material in terms of heat transfer for high power applications. This advantage can contribute to decrease the cooling equipments, and therefore to increase power density of system using WBG devices, compared to Si devices [9].

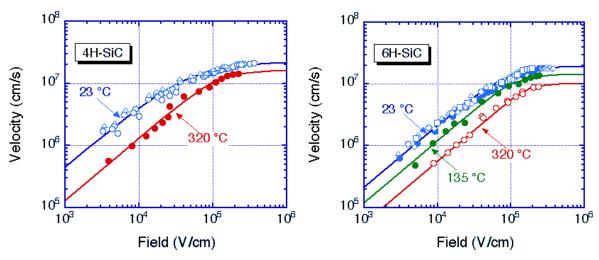

#### High saturated drift velocity

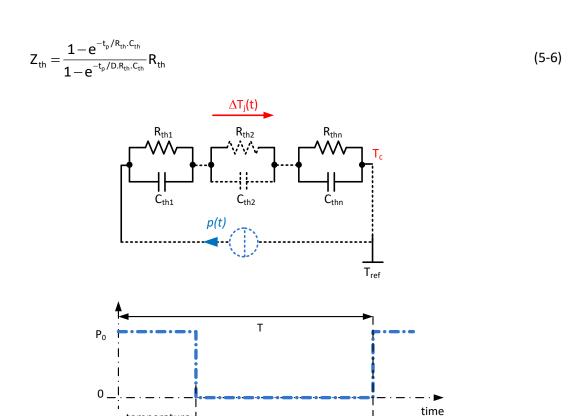

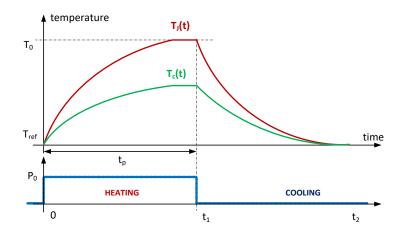

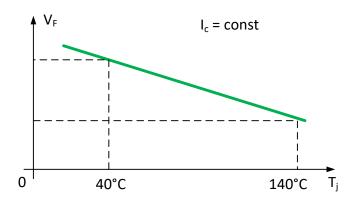

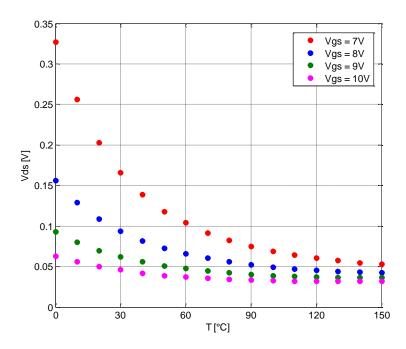

The saturated velocity  $v_{sat}$  is the maximum velocity of the carriers at high electric fields which is a pivotal parameter to determine speed of materials in switching applications [7, 10, 11]. For example,