# Converter architecture integrating detection of electric arc faults applied to continuous photovoltaic energy sources

Benjamin Vidales

#### ▶ To cite this version:

Benjamin Vidales. Converter architecture integrating detection of electric arc faults applied to continuous photovoltaic energy sources. Signal and Image processing. Université de Lorraine; Instituto tecnológico de Morelia (Mexique), 2021. English. NNT: 2021LORR0040. tel-03335792

#### HAL Id: tel-03335792 https://hal.univ-lorraine.fr/tel-03335792

Submitted on 21 Jun 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

#### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

Architecture de convertisseur intégrant une détection de défauts d'arcs électriques appliquée au sources d'énergie continues d'origine photovoltaïques.

### **THÈSE**

Présentée et soutenue publiquement le 15 Décembre 2020

Pour l'obtention du

#### Doctorat de l'Université de Lorraine

(Spécialité systèmes électroniques)

#### Par Benjamin Vidales Luna

#### Composition du jury

#### Président:

M. Bertrand Raison, Professeur, Université de Grenoble Alpes, Grenoble *Rapporteurs* :

M. Erwann Carvou, Enseignant chercheur HDR, Université de Rennes 1, Rennes

M. El-Hassane Aglzim – Professeur, Université de Bourgogne, Nevers

#### Examinateurs:

- M. Serge Weber, Professeur, Université de Lorraine, Directeur de thèse (DT)

- M. Patrick Schweitzer, MCU HDR, Université de Lorraine, Co-directeur de thèse (CDT)

- M. Manuel Madrigal Martínez Profesor SNI- II, Tecnológico Nacional de México (DT Mexique)

- M. Domingo Torres Lucio, Profesor, Tecnológico Nacional de México (CDT Mexique)

Mme. Nadia Maria Salgado Herrera, Profesora Asociada, Instituto de Energías Renovables (IER - Mexique).

M. José Luis Monroy-Morales, Profesor SNI- C, Tecnológico Nacional de México.

#### Remerciements

I want to express from the bottom of my heart my most sincere gratitude to my beloved family for all their love and support along this path in the search of knowledge, especially to my father who with his example instilled in me the will to achieve my goals with respect and honesty.

I thank my advisor and friend Dr. Manuel Madrigal Martínez for allowing me to work shoulder to shoulder on this great project, as well as sharing his valuable advice and experiences with me, which shape me as a human being and as a professional for the future.

I thank my advisor and friend Dr. Domingo Torres Lucio for having shared his french studies experience with me, which undoubtedly motivated me to have this type of experience and which allowed me to polish new skills in a great environment of work.

I thank my advisers Patrick Schweitzer and Serge Weber for all their support, advice and guidance in discovering new branches of knowledge that overcome barriers of distance, languages and cultures.

I thank all the departments of the PGIIE and IJL for all their hard work and effort which favor the high-level technological development of science without losing the human warmth and kindness that characterizes them so much.

I also thank my colleagues Dr. José Luis Monroy Morales and Dr. Juan Ramón Rodríguez Rodriguez, not only for their knowledge and experience shared but also for their kind friendship.

To the National Council of Science and Technology (CONACYT), for having allowed me to be part of the scholarship holders for postgraduate studies in both my master and doctoral degree.

I am grateful to the National Association of Universities and Institutions of Higher Education (ANUIES) for its support through the exchange project for researchers and students, México-France ECOS-NORD.

To the Technological Institute of Morelia and the University of Lorraine for given me the opportunity to train as a professional within these beautiful educational institutions.

#### Abstract

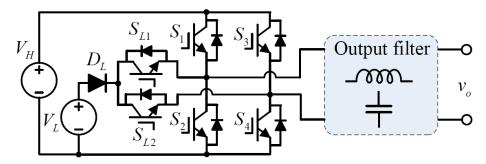

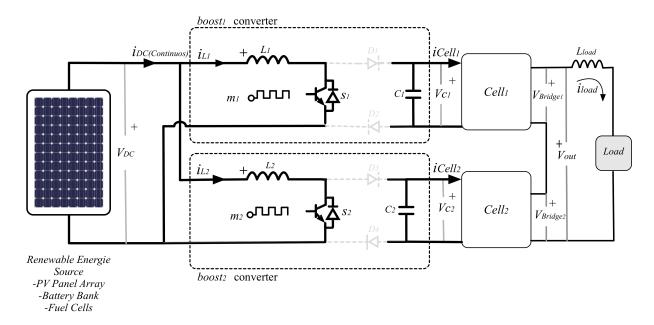

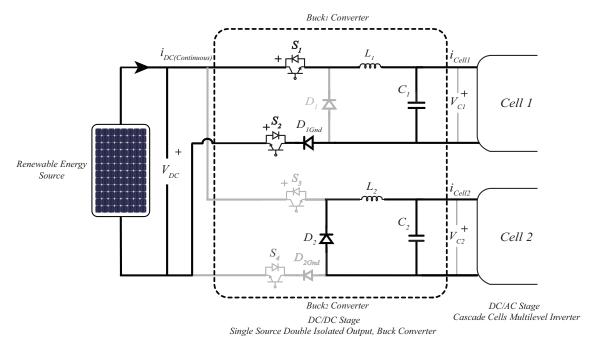

In this research work, the development of a multilevel inverter for PV applications is presented. The PV inverter, has two stages one DC/DC converter and one DC/AC inverter, and is capable of generating an AC multilevel output of nine levels, it's a transformerless inverter and uses a reduced number of components compared to other topologies. The conception of a novel DC/DC converter is capable of generating two isolated DC voltage levels needed to feed the DC/AC stage. This DC/DC stage is developed in two variants, buck and boost, the first to perform the reduction of voltage when the DC bus is too high, and second to increase the voltage when the DC bus is too low to perform interconnection with the grid through the DC/AC inverter.

This is achieved thanks to the parallel functioning of the developed topology, which make use of moderated duty cycles, that reduces the stress in the passive and switching components, reducing potential losses. The validation of the PV inverter is performed in simulation and experimental scenarios. In the other hand, the response of the inverter facing an arc fault in the DC bus is studied by performing a series of tests where the fault is generated in strategic points of the DC side, this is possible thanks to the design and construction of an arc fault generator based in the specifications of the UL1699B norm. During the tests is observed that with the apparition of an arc fault, there is a lost in the half-wave symmetry of the AC multilevel output voltage waveform, generating even harmonics which aren't present during normal operation, only when an arc fault is present in the DC system.

The monitoring of even harmonics set the direction for developing the detection technique. Since the magnitude of even harmonics in the inverter is very low, the total even harmonic distortion is employed as a base for the detection technique presented in this thesis. The effectiveness of this method is verified with a series of tests performed with different loads.

#### Résumé de Thèse

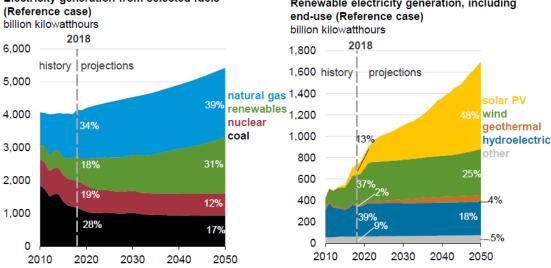

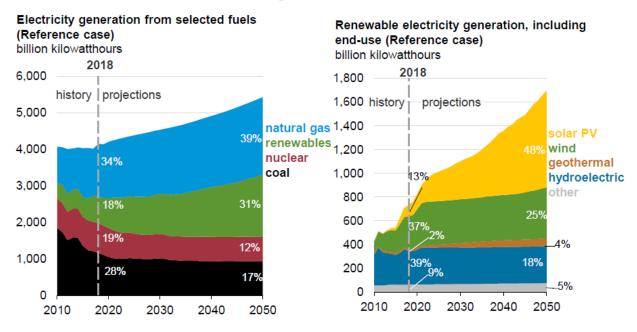

En 2019, l'EIA (Energy Information Adminitration) a publié l'annual Energy Outlook (AEO) où la projection énergétique pour les Etats-Unis est étudiée et modélisée afin de prédire d'une façon approximative la demande d'énergie nécessaire d'ici 2050. Cette étude est basée sur le système national de modélisation énergétique AEO (NEMS), un modèle intégré qui prend en compte les interactions des changements économiques, tels que l'offre et la demande mais également les prix de l'énergie. Selon cette étude, la production d'énergie au moyen de sources renouvelables, comme la production éolien et le solaire photovoltaïque seront les principales sources d'énergies du futur.

Le solaire photovoltaïque représentera 48% de la production totale et la production éolienne 25% d'ici l'an 2050, comme le montre la Fig. 1.

# Electricity generation from natural gas and renewables increases, and the shares of nuclear and coal generation decrease— Electricity generation from selected fuels (Reference case) Renewable electricity generation, including end-use (Reference case)

**Figure 1.** AEO report of renewable energy production projected to 2050.

La constante croissance des installations solaires photovoltaïques a conduit à la recherche et lu développement de convertisseurs de haute puissance nécessaires pour effectuer l'interconnexion des panneaux photovoltaïques au réseau national. Cette technologie de convertisseurs tente d'obtenir une réduction du nombre de composants, toute en mantenant

une efficacité performante et en integrant une protection contre les défauts, entre autres.

Dans le domaine des énergies renouvelables et la production d'énergie électrique, la détection des arcs électriques est d'une importance fondamentale et constitue une des préoccupations de cette thèse. Plus particulièrement nous nous concentrons sur la détection des défaut d'arc électrique série qui peuvent apparaître dans notre installation.

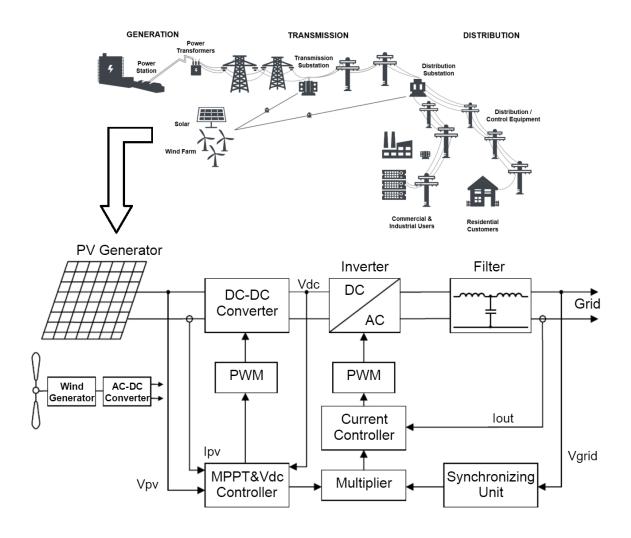

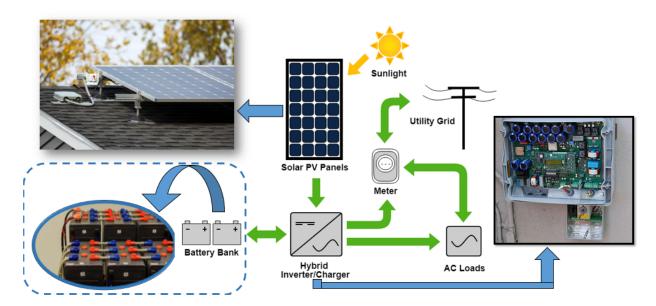

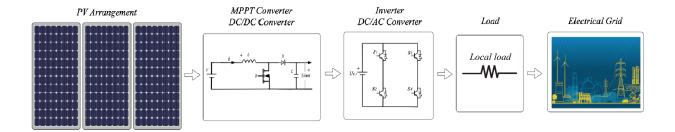

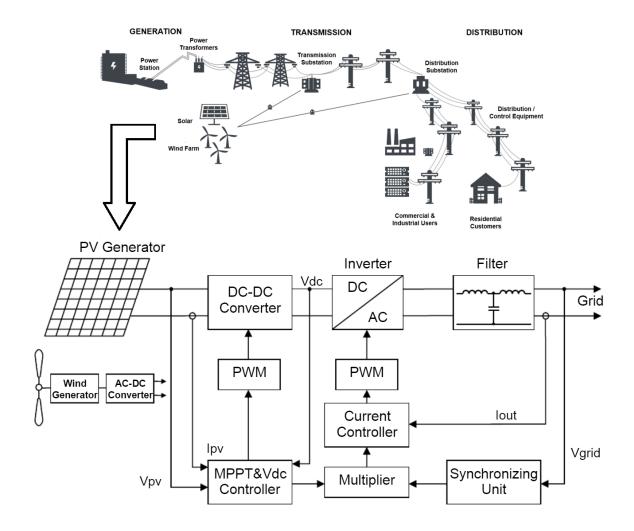

La structure principale d'un réseau smart grid est présentée sur la Fig. 2. L'ensemble se compose de convertisseurs DC/DC et DC/AC transformant l'énergie produite par les panneaux photovoltaïques en courant alternatif dans le cas particulier d'un système interconnecté au réseau électrique. Une autre configuration consiste à utiliser des batteries pour le stockage de l'énergie.

La première partie de ces travaux de thèse consiste à développer une topologie de convertisseur multiniveaux innovant. En effet une structure de convertisseur multiniveaux apporte de multiples avantages pour la génération d'énergie tels qu'un faible contenu harmonique, un nombre de composants réduit et un meilleur contrôle de la puissance transmise au réseau.

Le second thème abordé concerne l'intégration d'un système de détection de la présence d'un défaut d'arc électrique dans le convertisseur. En effet, l'apparition des défauts d'arc électrique peut conduire à l'apparition d'un incendie dans un système de génération photovoltaïque et doit absolument être détecté.

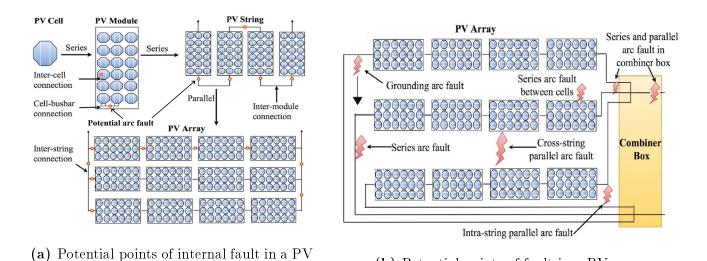

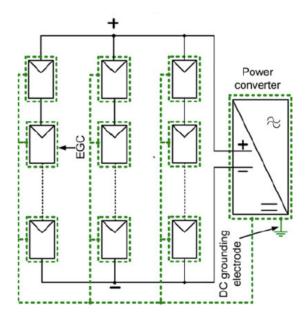

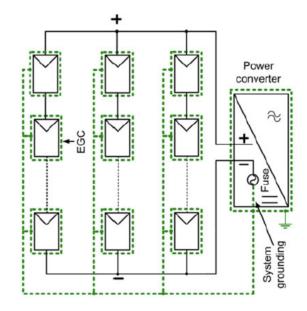

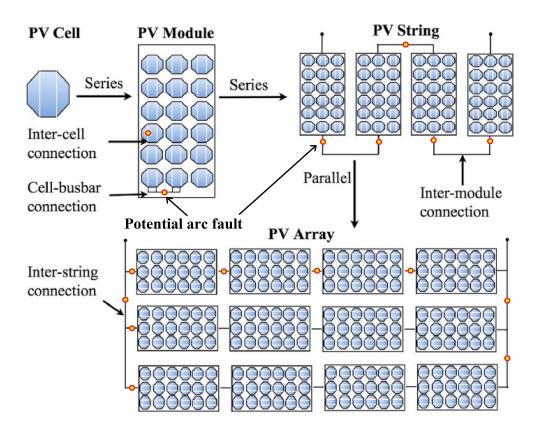

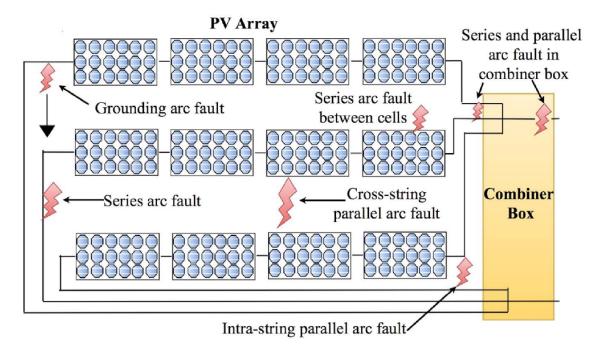

Ces arcs peuvent apparaître soit à l'intérieur de panneaux (câbles internes de connexion des cellules silicium, entre les cellules etc.) soit à l'extérieur des panneaux (boite de connexion, câbles des distributions, etc.). Ces défauts d'arc électrique sont soit des arc séries soit des arcs en parallèle. La Fig. 3 montre les principaux défaut d'arc en série ou parallèle pouvant se produire dans une installation des panneauxs solaire photovoltaïque.

panel.

Figure 2. Distribution Grid arrangement.

Figure 3. Potential Arc Fault in PV panels.

(b) Potential points of fault in a PV array.

En raison des nombreux points de défauts possibles et de leurs différentes causes, le défi de développement d'un système capable de détecter efficacement les arcs dans ce type de système est une réelle préoccupation pour la sécurité des installations et des personnes.

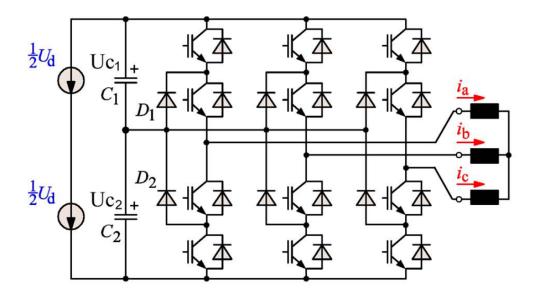

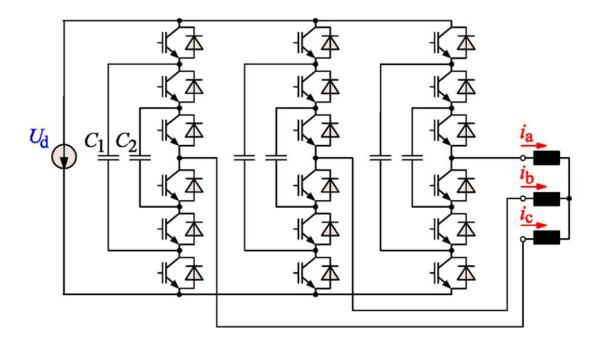

#### Convertisseur Multiniveaux

Les systèmes de production PV utilisent des convertisseurs électroniques de puissance afin de transformer l'énergie provenant des panneaux en énergie exploitable par le réseau électrique. Parmi ces types de convertisseurs, les onduleurs à plusieurs niveaux présentent des avantages clés par rapport aux onduleurs conventionnels à deux niveaux.

Les onduleurs multiniveaux sont couramment utilisés pour des applications de forte puissance. La littrature présente de nombreuses topologies multiniveaux destinées aux applications dans le domaine des énergies renouvelables, à base des les topologies clamping diode, flying capacitor et cellules en cascade. Les principaux inconvénients de ces deux premières topologies sont l'utilisation de nombreux composants ainsi que le déséquilibre des niveaux de tension des condensateurs.

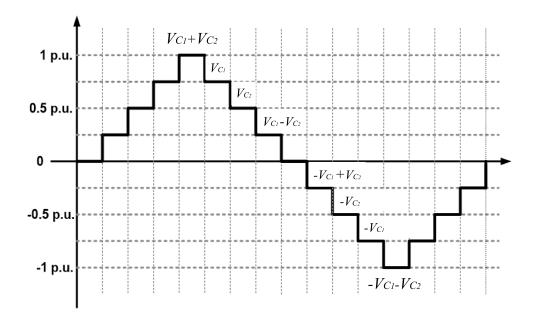

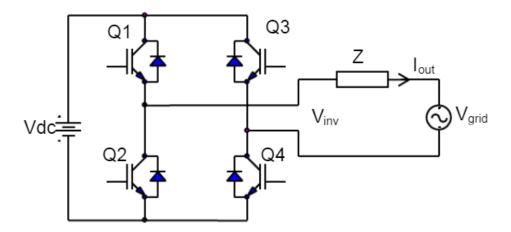

Cette topologie de cellules est constituée de plusieurs (minimum deux) modules connectés en série, sont basé sur des ponts en H complets. Le nombre de niveaux de tension peut facilement être augmenté en ajoutant de nouveaux modules, alors que les autres topologies voient le npmbre des diodes ou de condensateurs augmenter de façon exponentielle.

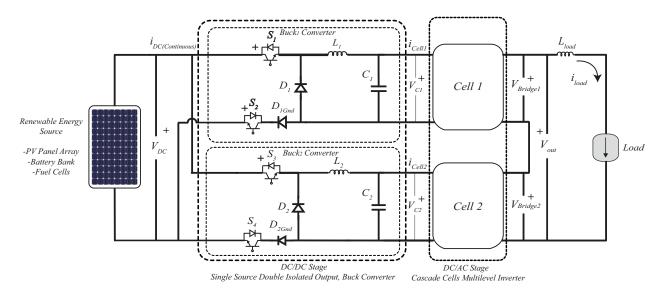

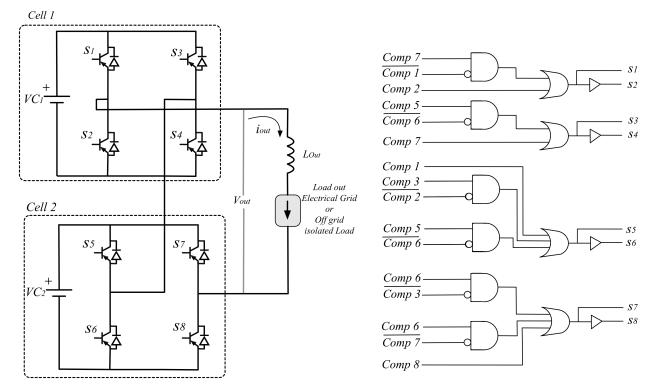

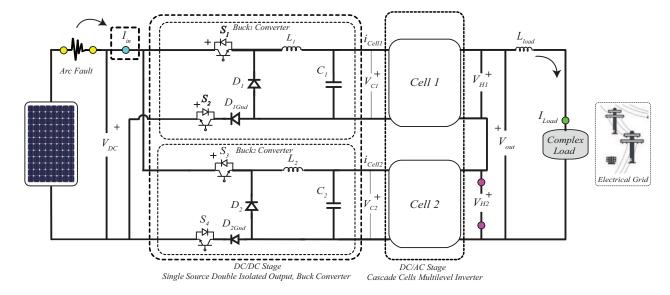

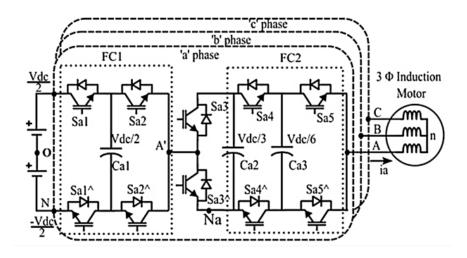

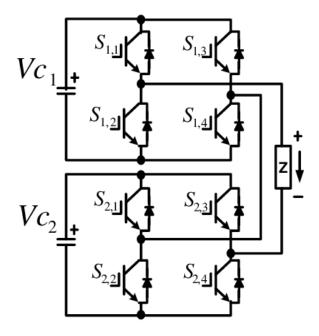

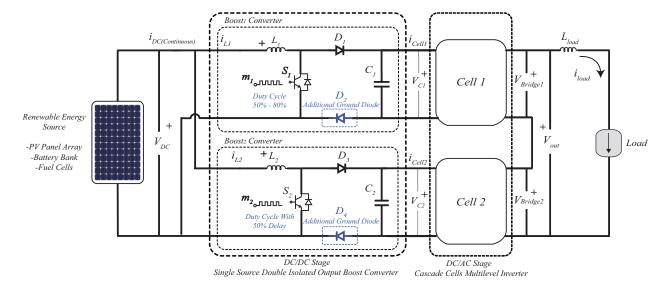

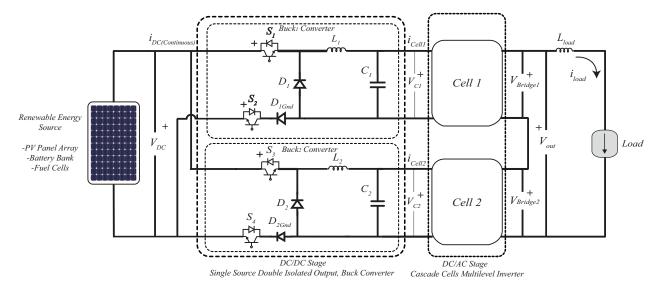

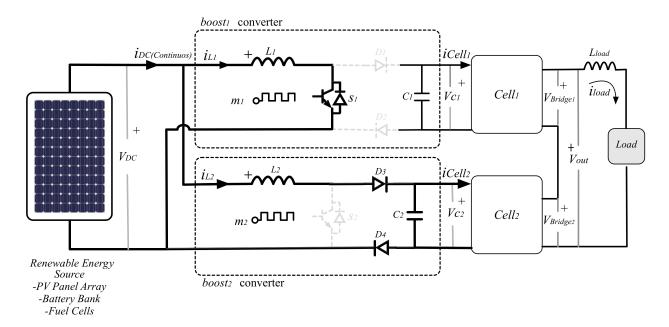

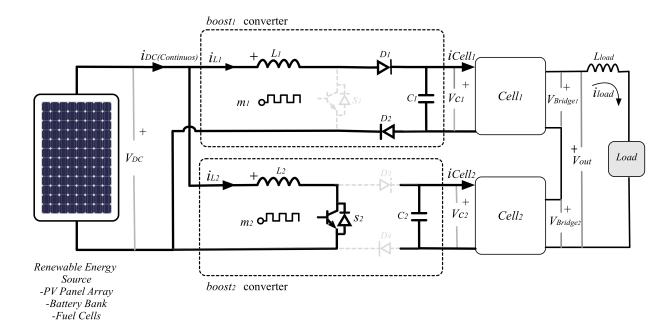

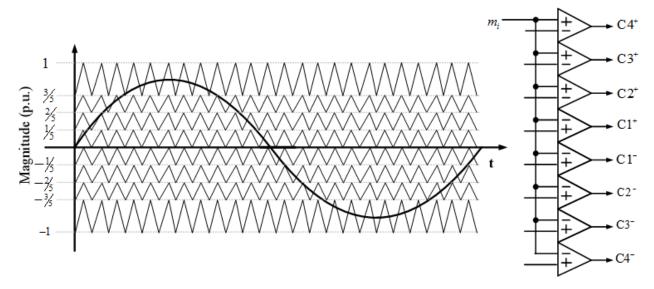

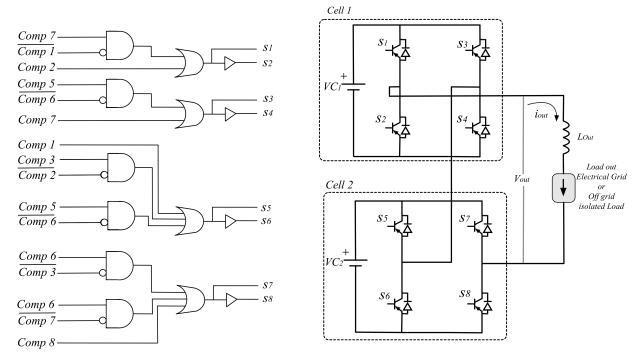

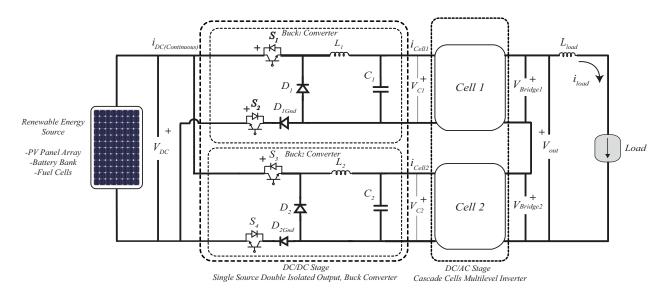

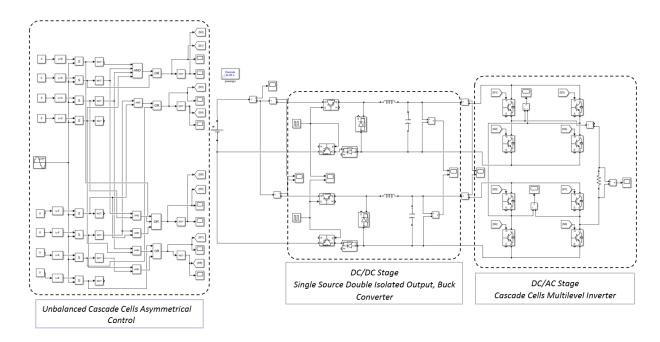

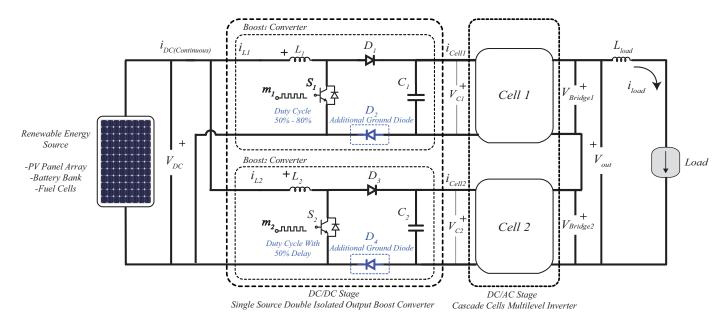

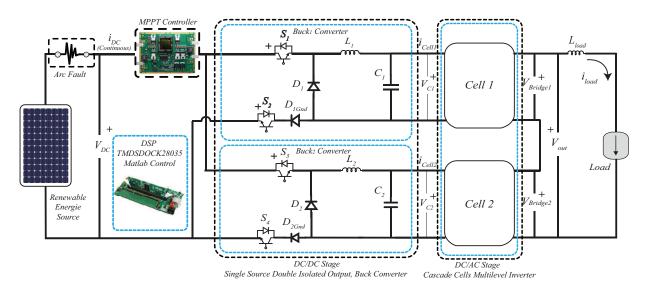

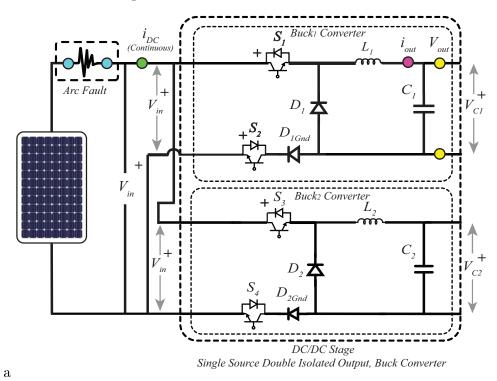

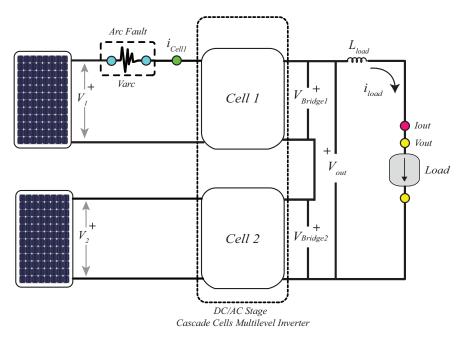

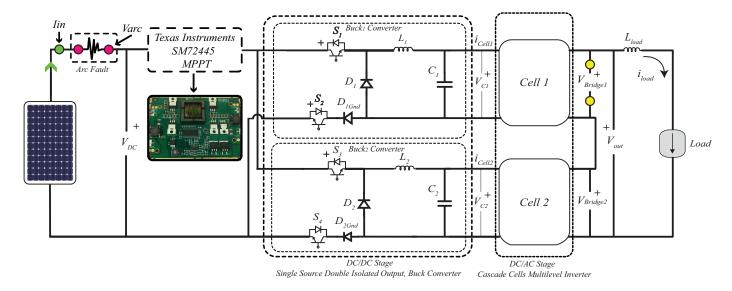

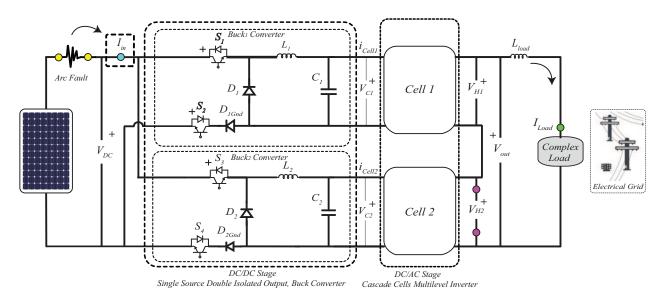

Une topologie innovante de convertisseur neuf niveaux, présentée en Fig. 4, est proposée dans le chapitre 3 de la thèse.

Figure 4. Inverter proposed system schematic diagram, buck variant.

(a) CCMI schematic circuit for a nine-level (b) Boolean logic combination for a asymmetrical inverter.

Figure 5. Cascade cells multilevel inverter topology and control.

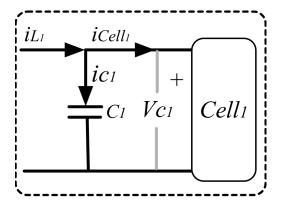

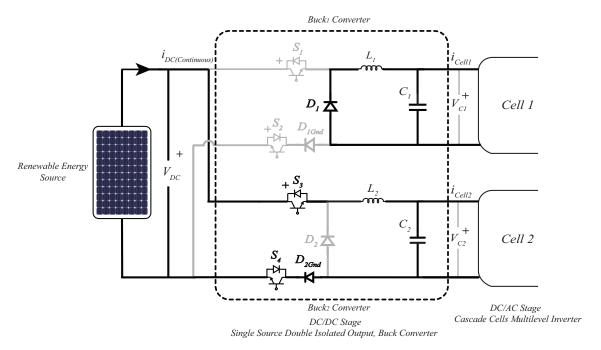

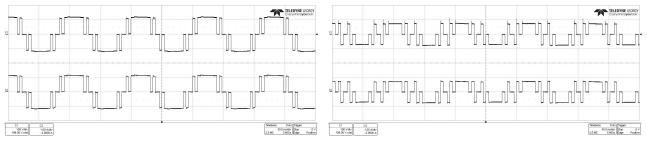

Cette topologie utilise deux cellules en cascade et ainsi qu'une topologies DC/DC qui alimente ces deux cellules à partir d'une seule source. Dans le chapitre 3, deux structures différentes de convertisseurs DC/DC (variantes buck et boost) développés spécifiquement pour cette thèse sont proposés. La configuration des cellules en cascade ainsi que leur contrôle est préséntée sur la Fig. 5 (a) et (b).

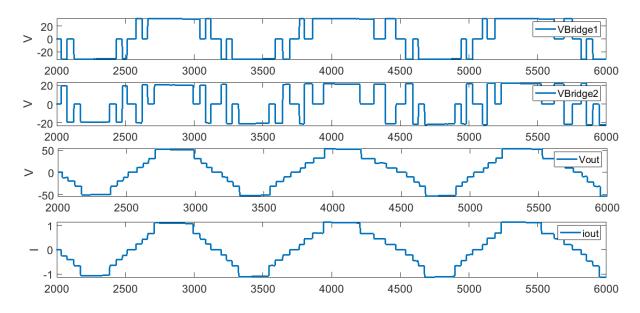

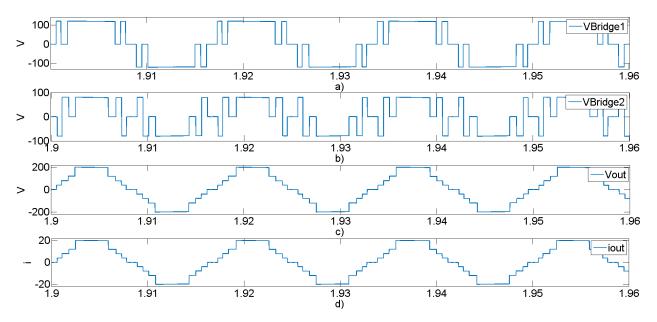

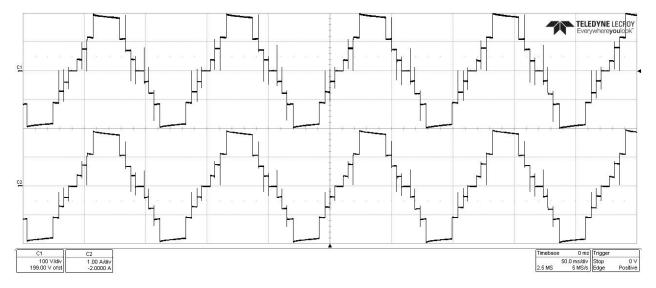

Avec cette configuration, les formes d'ondes simulée obtenues à la sortie de la cellule 1 (VBridge1) et de la cellule 2 (VBridge2), ainsi que les sorties tension et courant de convertisseur sont représentés dans la Fig.6.

**Figure 6.** Simulation results of the DC/AC stage a)VBridge1, b)VBridge2, c) $V_{out}$ , d) $I_{out}$ .

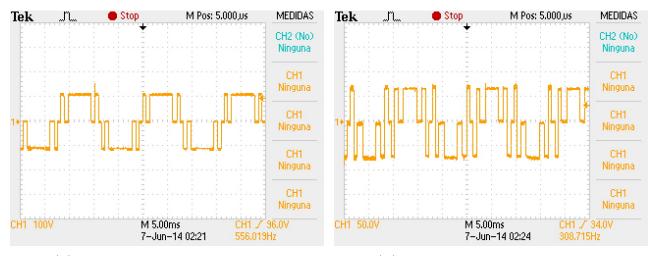

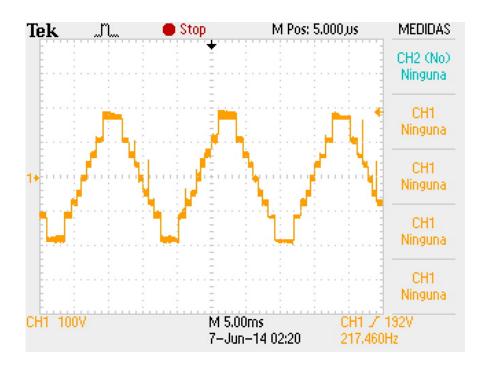

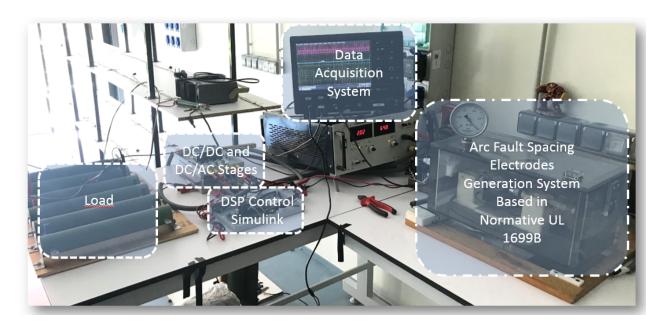

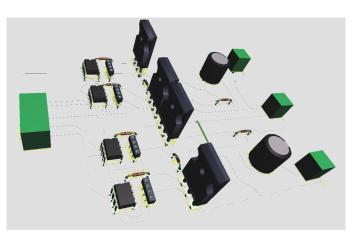

A partir des resultats de simulation, la topologie du convertisseur multiniveaux a été validée. Un banc de test a été développé pour tester expérimentalement ce convertisseur.

#### Banc d'essai

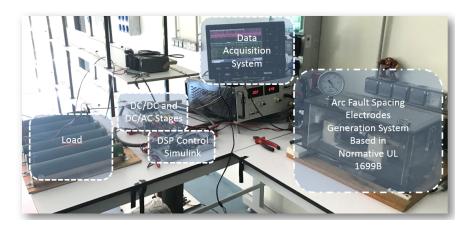

La Fig. 9 représente le banc d'essai et les éqipements utilisés qui sont également listés dans la table 0.0.1.

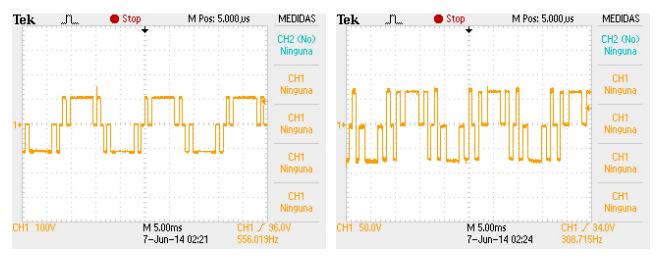

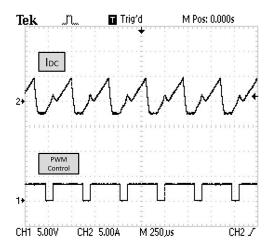

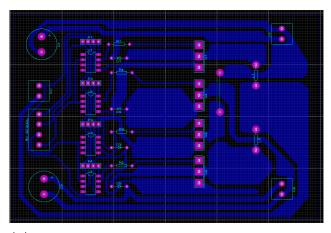

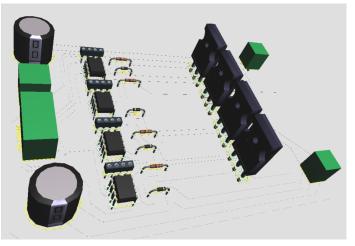

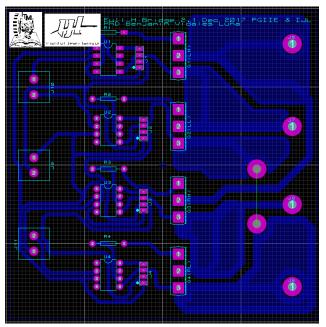

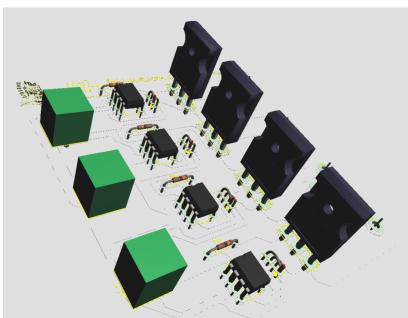

Pour la mise en oeuvre de la partie électronique des convertisseurs, les PCB sont détaillés dans l'annexe 3. Avec ce banc d'essai, les Fig. 7 et Fig. 8 représent les tensions mesurée a

VBridge1 et VBridge2 au nivaux de convertisseur.

- (a) Voltage waveform of *VBridge*1.

- (b) Voltage waveform of *VBridge*2.

Figure 7. VBridge1 and VBridge2 signals obtained using DC/DC Buck variant.

Figure 8. Voltage and current waveforms of the nine-levels AC output, using buck variant.

TABLE 0.0.1. Test Bench Equipment.

| TABLE 0.0.1. Test Bench Equipment.                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Componet                                                                                             | Value-Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Temperature  Electrodes Material                                                                     | 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                                      | (a) Carbon (b) Copper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Electrodes Distance Gap Protective Case Material                                                     | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Texas Instruments DSP Matlab Simulink                                                                | 10 mm der grie vox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| $High\ Definition$ $Osciloscope\ LeCroy\ HD4096$ $12-bit\ resolution\ up\ to\ 8\ GHz\ and\ 20\ GS/s$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| $Voltage\ Probe\ TESTEC\ TT-SI\ 9010$ $7000\ V\ 70MHz$                                               | THE THE PARTY OF T |  |  |  |

| Arc Fautl Generator UL1699B Based                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| $\begin{array}{c} Current\ Probe\ CP030A\\ 30\ A\ 50\ MHZ \end{array}$                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Load Type tested                                                                                     | $R, RL, Complex\ Motor$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| $Load\ Values\ Tested$                                                                               | $R = 22\Omega, 47\Omega$ $L = 20mH, 141mH$ $Universal\ Motor = 1200\ W\ Hammer\ Drill$ $Universal\ Motor = 600\ W\ Vacum\ Cleaner$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

Figure 9. Experimental Test bench.

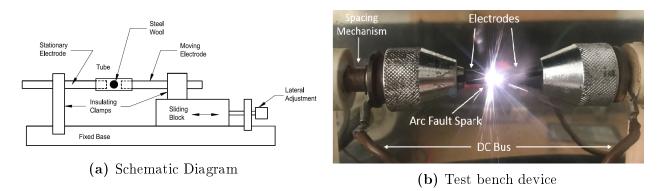

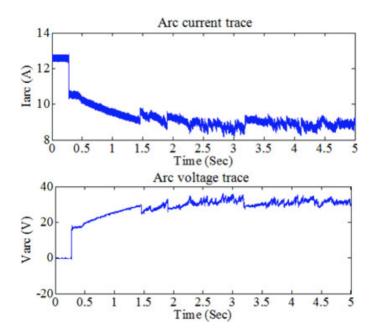

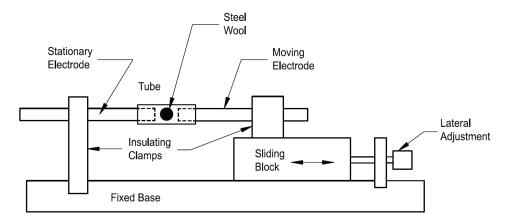

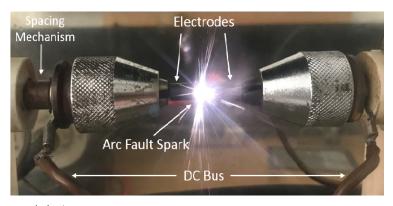

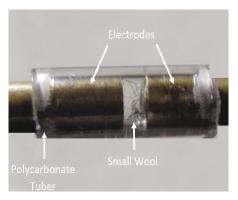

Pour étudier le comportement du convertisseur en présence des défauts d'arcs électriques, un génerateur d'arc respectant la norme UL 1699B a été proposé. Les arcs électriques sont fait en suivant ainsi les spécifications de la norme UL 1699B. La technique d'écartement des électrodes est utilisée pour générer les defauts d'arcs (AF). La Fig. 10 illustre le dispositif.

Figure 10. AF Generation device UL1699B.

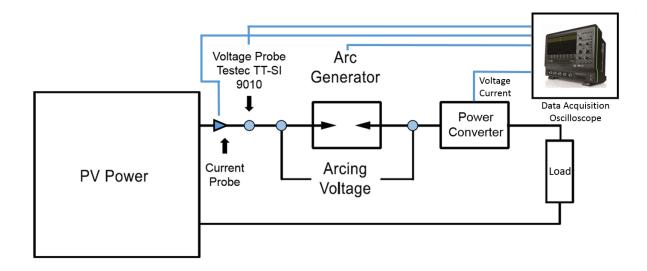

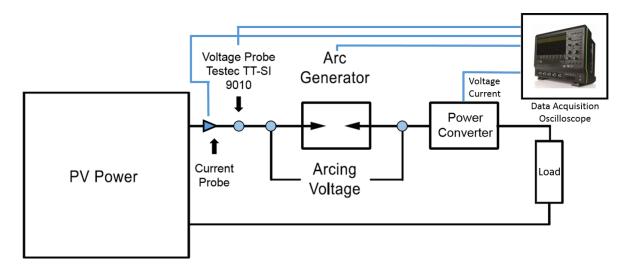

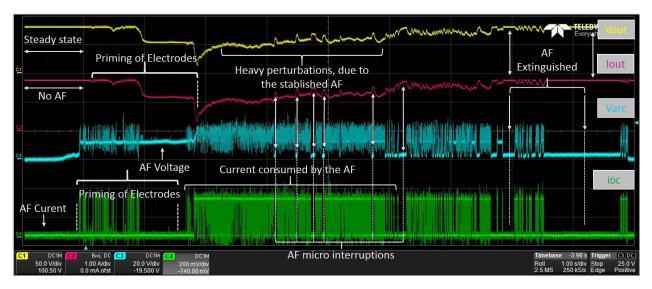

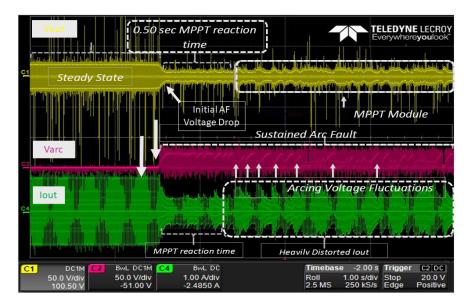

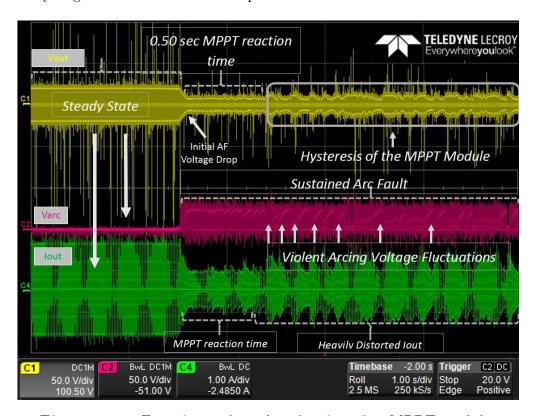

Pour évaluer le comportement des convertisseurs, la partie DC/DC est testée expérimentalement en présence d'un AF. Ensuite la partie DC/AC est soumise au même défaut. Le schéma du banc d'essais représente sur la Fig. 11 montre l'emplacement du défaut insèré dans le circuit et des mesures de tension et courant réalisées.

Avec ces expériences, nous avons pu confirmer que l'étage DC/DC du convertisseur se limite a suivre les variation produite par l'AF. Par conséquent, chacune des fluctuations de l'AF

Figure 11. AF Load Study Schematic Diagram.

affecte la tension de sortie du convertisseur (même en utilisant un bloc de régulation MPPT). Néanmoins, nous montrons que l'AF crée des perturbation au niveau de l'étage de conversion DC/AC.

#### Détection des AF

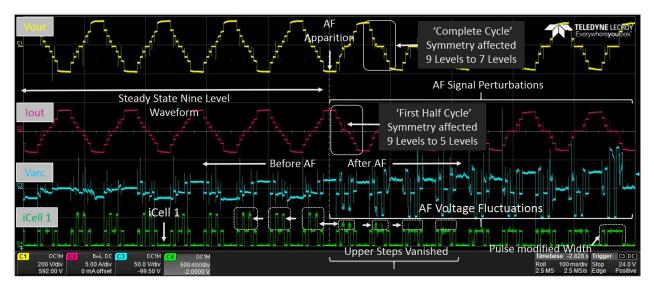

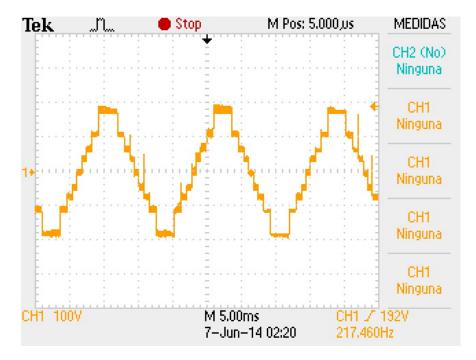

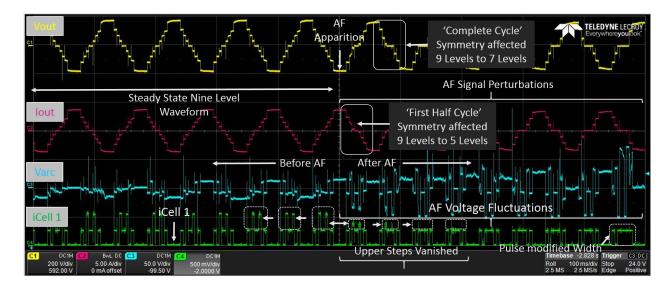

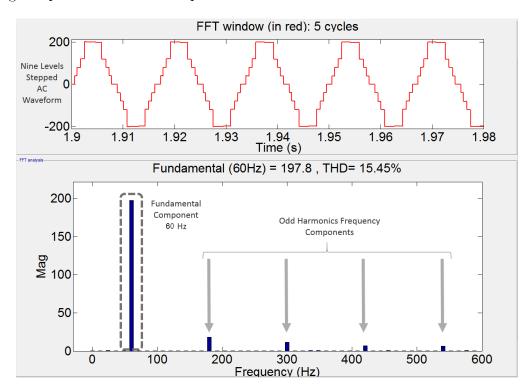

Suite à la mise en évidence de l'influence de l'AF sur la topologie proposée du convertisseur multiniveaux. Avec l'apparition de l'arc dans le système, l'équilibre entre la cellule 1 et la cellule 2 de la configuration de cellules en cascade est altéré par les rapides fluctuations de l'arc. Ce changement produit la perte de certains des neuf niveaux dans la signal de sortie.

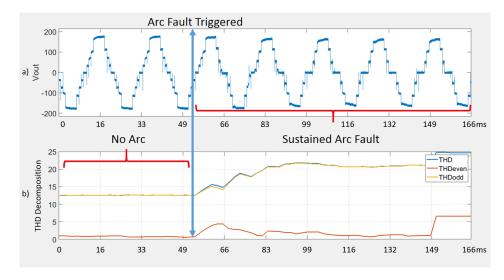

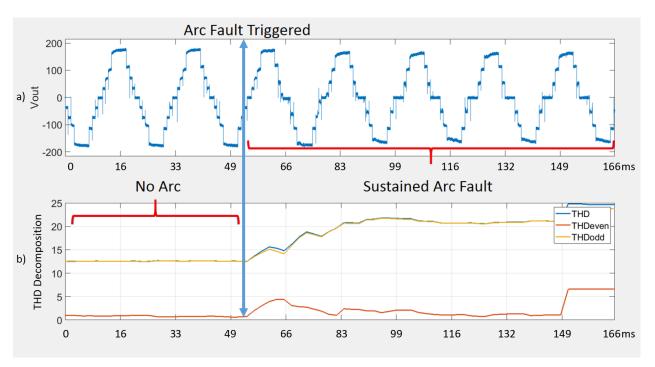

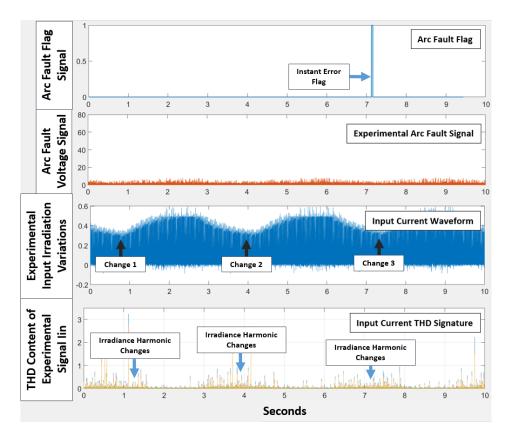

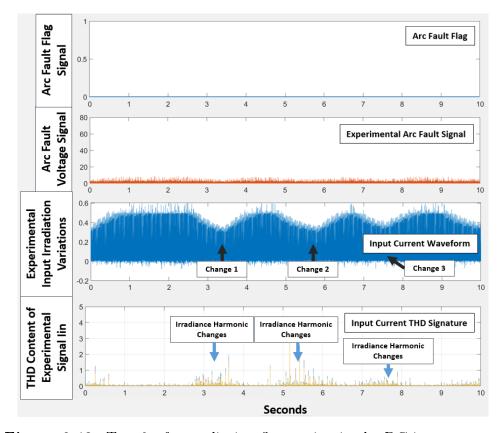

C'est sur ces phènomènes présentés dans la Fig. 12 que se base la stratégie de détection présentée dans ces travaux. La perte de niveaux associée à l'apparition est une d'arcs est une perturbation spécifique des défauts d'arc. Par contre, les modifications du rayonnement solaire sur le panneau n'affectent pas la symétrie des ondes comme le fait l'apparition d'arc.

Dans le mode de fonctionnement neuf niveaux du convertisseur (dans un mode de fonctionnement sans défaut dans le circuit), l'analyse spectrale de la tension montre que le

spectre est exclusivement composé d'harmoniques impaires.

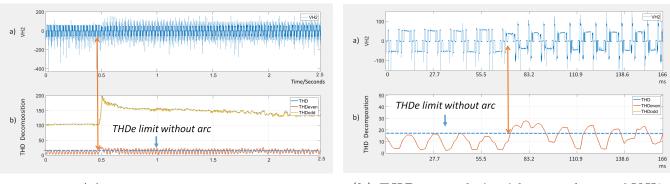

Cela signifie qu'avec l'apparition d'un arc, la symétrie de l'onde est modifieé et la quantité d'harmoniques paires (inexistante en fonctionnement normal) se voit augmentée brusquement à l'apparition d'arcs (taux de distorsion d'harmoniques paires donc THDe).

Figure 12. Multilevel waveforms obtained under AF.

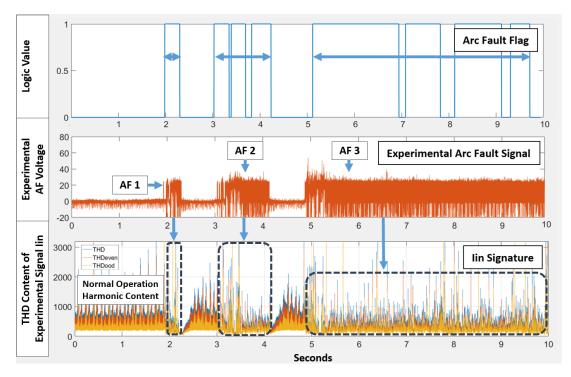

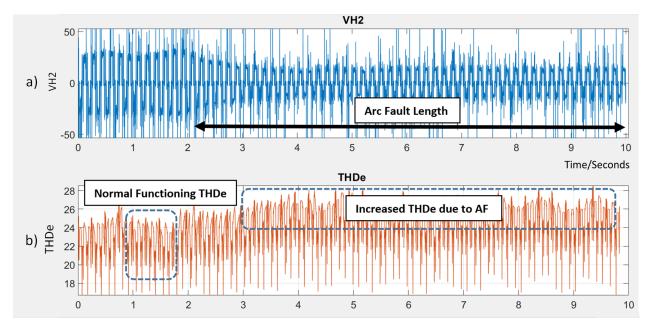

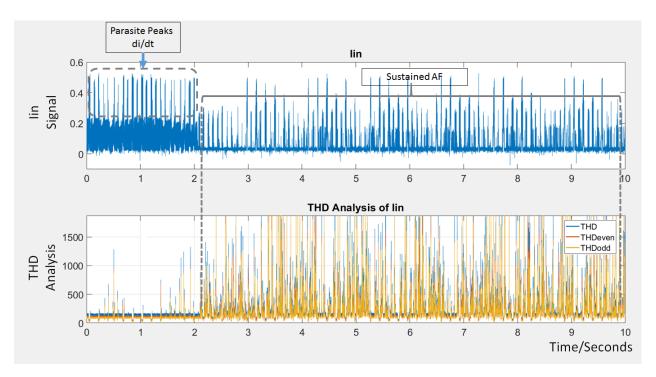

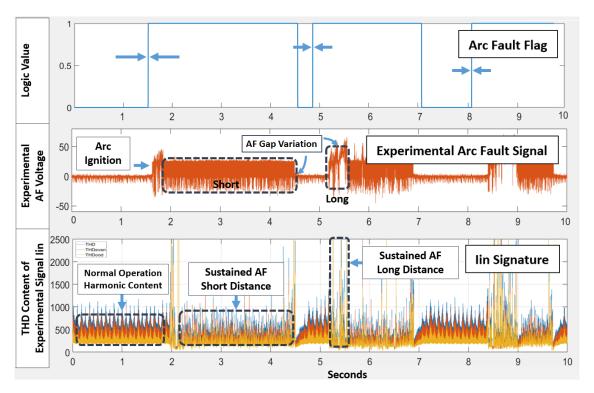

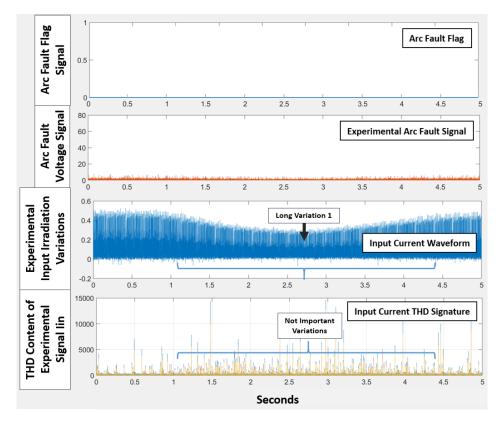

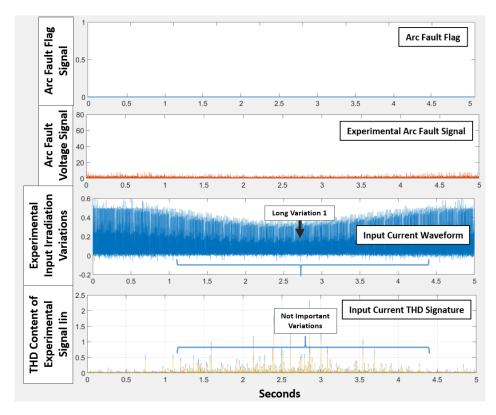

L'èchantillonnage des signaux expérimentaux se fait avec une cadence de 250 k/s afin de réaliser le traitement du signal avec Matlab. La Fig. 13 montre l'évolution du taux de distorsion harmonique en fonction de temps. Ces observations nous permettent de confirmer notre hypotèse concernant les changements sur le contenu harmonique paire au moment de l'apparition d'AF.

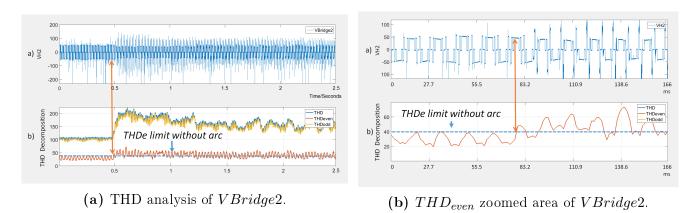

#### Génération des AF dans un Système isole

Dans un premier temps, l'approche consistant à utiliser des signaux internes provenant du convertisseur pour déterminer la présence d'AF dans le système est testée dans la configuration de génération isolée. Pour la validation de cette approche, différentes charges sont alimentées avec la topologie présentée dans la Fig. 14. Les signaux pris en consid $\tilde{A}$ l'ration et mesure sont VH2 et  $I_{out}$ .

Les tests avec cette configuration nous permettent d'analyser comment le contenu harmonique

Figure 13. THD decomposition in  $THD_{even}$  and  $THD_{odd}$  before and after an AF.

Figure 14. AF Testing protocol for different loads, with highlighted measuring points.

des signaux enregistrés varie avec l'apparition des arcs. A partir du contenu harmonique paire pour chacun de ces signaux, nous sommes en mesure de déterminer une valeur moyenne qui servira de seuil pour indiquer la présence d'arc.

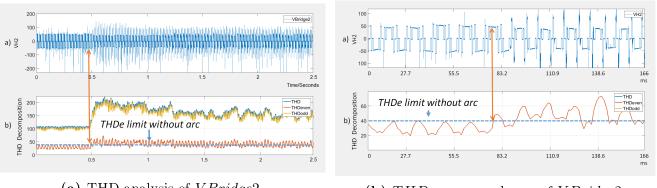

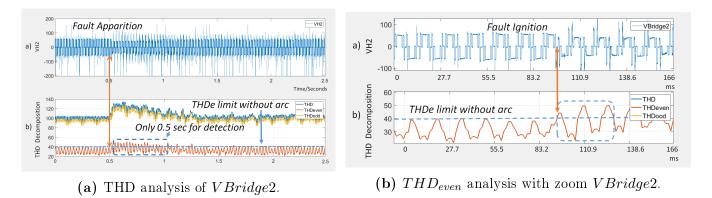

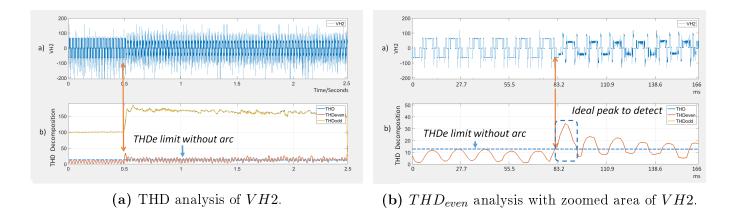

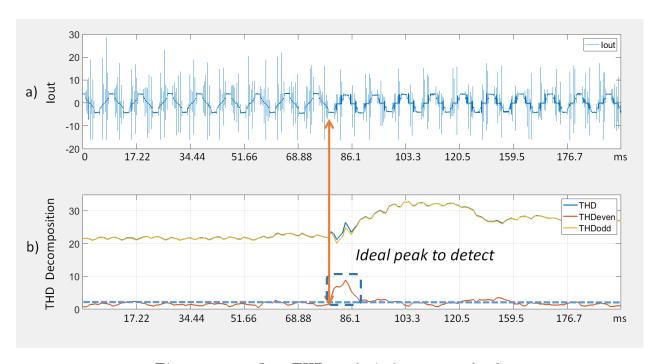

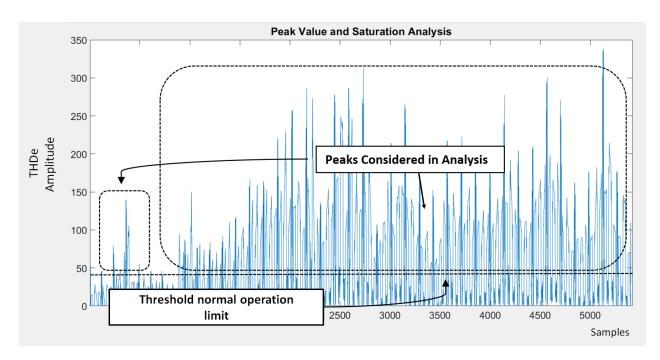

Un exemple d'utilisation de cette approche est présenté en Fig. 15 et Fig. 16 pour une charge fortement inductive utilicée dans test. Les pics du contenu harmonique paire portant sur la signal VH2 liés à l'apparition de l'arc,

L'augmentation des harmonique paires liée a l'apparition du l'AF, est validée dans la section

- (a) THD analysis of VBridge2.

- (b)  $THD_{even}$  zoomed area of VBridge2.

Figure 15. VBridge2 harmonics decomposition.

6.4 de la thèse pour l'ensemble des types de charges testées.

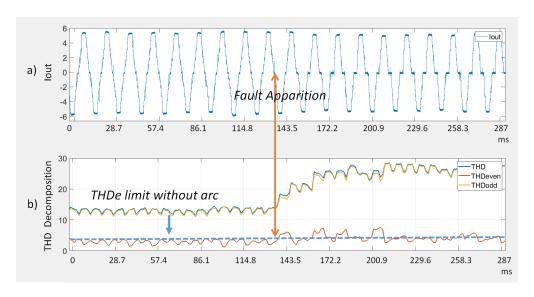

Par contre le comportement de  $I_{out}$  est très variable en fonction de la charge pressent dans le circuit, ce qui empêche sont utilisation dans un système de détection.

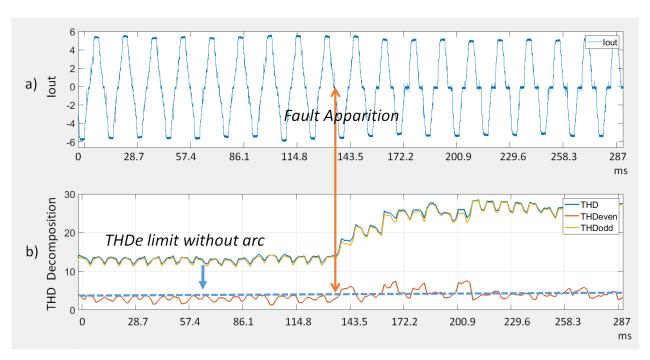

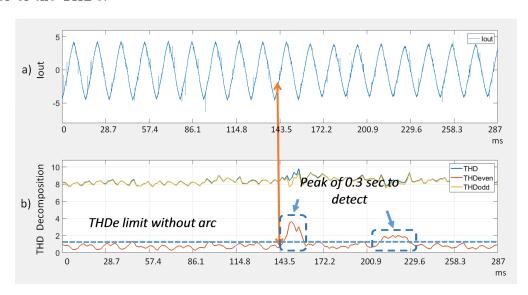

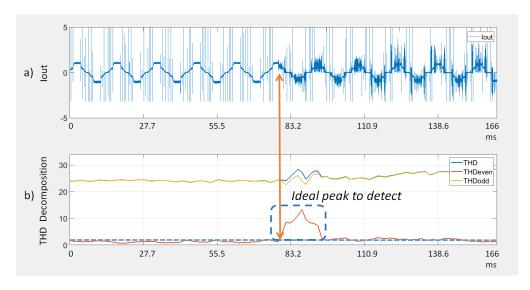

Figure 16.  $I_{out}$  THD Decomposition technique.

Le récapitulatif des changements dans le taux de distorsion avec l'apparition d'arc selon la charge connectée pour un systeme isolé est présenté dans la Fig. 17.

| Signals                                     | Without Arc | Without Arc | Without Arc                         | With Arc                         | With Arc                         | With Arc                          |

|---------------------------------------------|-------------|-------------|-------------------------------------|----------------------------------|----------------------------------|-----------------------------------|

| THD Type                                    | THD         | THDo        | THDe                                | THD                              | THDo                             | THDe                              |

| <i>Iout</i><br>22 Ohms + 20mH               | 11-14%      | 11-14%      | 2-4%                                | 25-29%                           | 25-29%                           | 5-8%                              |

| <i>VBridge</i> 2<br>22 Ohms + 20mH          | 110-115%    | 95-110%     | 20-40%                              | 150-220%                         | 145-210%                         | 38-65%                            |

|                                             |             |             |                                     | Criterion of 3%                  | of increment                     | <del>\</del>                      |

| <i>Iout</i><br>22 Ohms + <b>14</b> 1mH      | 8%          | 8%          | 0.5-1%                              | 8-10%<br>Only during<br>ignition | 8-10%<br>Only during<br>ignition | 0.5-4%<br>Only during<br>ignition |

| <i>VBridge</i> 2<br>22 Ohms + <b>14</b> 1mH | 110-115%    | 90-100%     | 22-40%<br>0.5sec during<br>ignition | 120-130%                         | 110-115%                         | 35-50%                            |

|                                             |             |             | Criterio                            | on of 13% of in                  | crement in THI                   | De                                |

| <i>Iout</i><br>Hammer-Drill                 | 24%         | 24%         | 1-2%                                | 6-29%                            | 26-25                            | 8-13%<br>Only during<br>ignition  |

| <i>VBridge</i> 2<br>Hammer-Drill            | 100%        | 100%        | 1-12%                               | 165-195%                         | 165-195%                         | 8-35%                             |

|                                             |             |             |                                     |                                  |                                  |                                   |

| <i>Iout</i><br>Vacuum                       | 22%         | 22%         | 3-4%                                | 26-34%                           | 26-34%                           | 9%<br>Only during<br>ignition     |

| <i>VBridge</i> 2<br>Vacuum                  | 100%        | 100%        | 5-13%                               | 145-200%                         | 145-200%                         | 10-29%                            |

Figure 17. Summary of Results for AF Tests.

Les mêmes expérimentations sont menées en situation de système interconecté au réseau.

#### Génération des AF dans un Système Interconnecté au Réseau

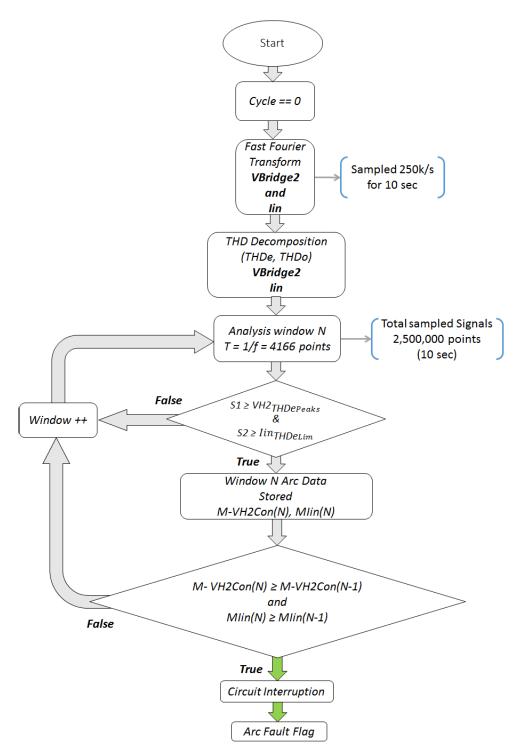

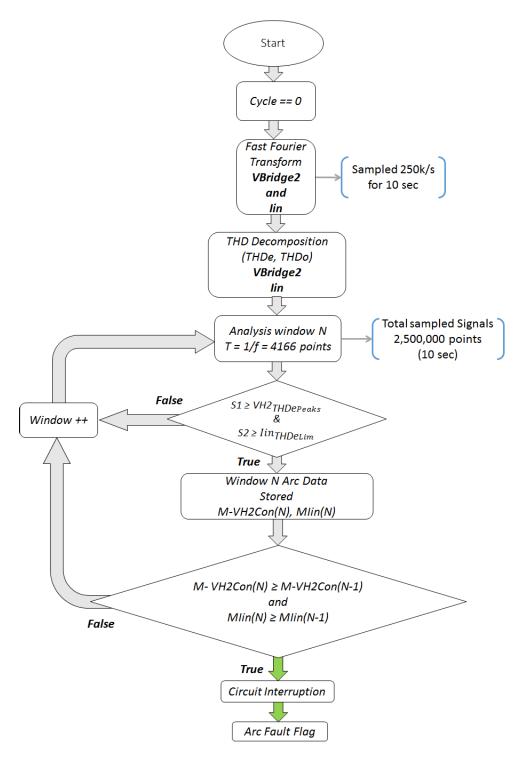

Pour étudier la réponse d'un système interconnecté au réseau en présence d'un AF, le schéma est identique à celui utilisé à la Fig. 14, avec la particularité d'avoir un filtre de couplage en sortie (calculé au paragraphe 6.5.2). Un algorithme de détection basé sur l'analyse des harmoniques paires est proposé pour tous les tests suivants. La principe de détection consiste à effectuer une analyse période par période de la valeur maximale de l'amplitude du taux de distorsion THDe de VH2, et en même temps la mesure de la quantité de pris dépassant un seuil déterminé de façon expérimentale. Pour tous les tests présentés, l'utilisation de l'algorithme de détection (basé sur l'étude des harmoniques paires) de la Fig. 18 est utilisé.

Figure 18. Proposed electric DC AF detection algorithm.

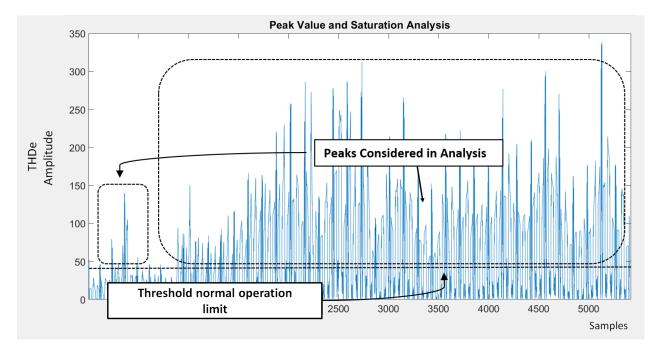

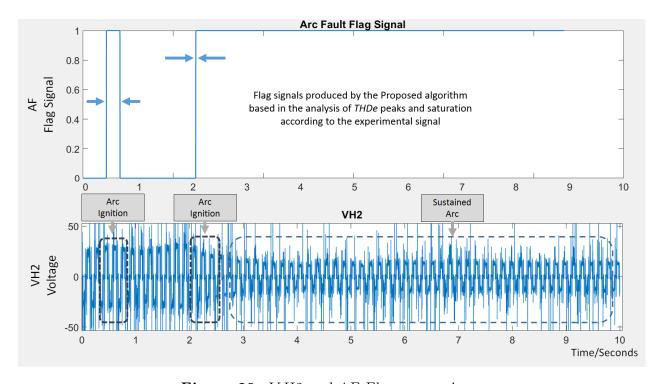

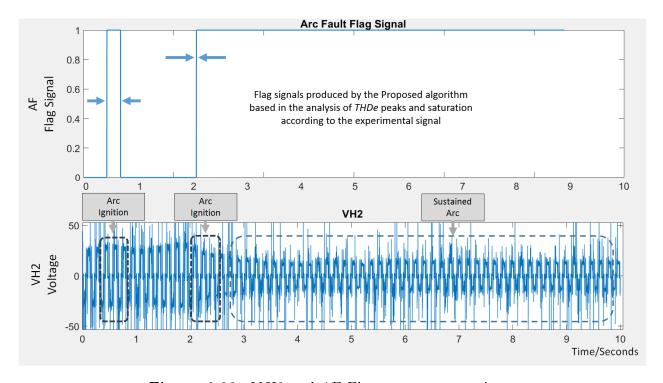

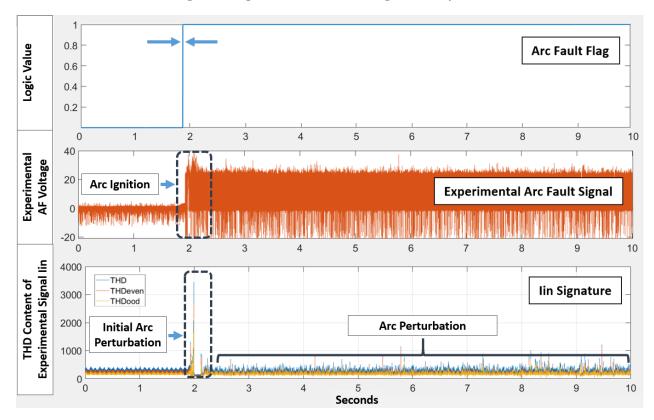

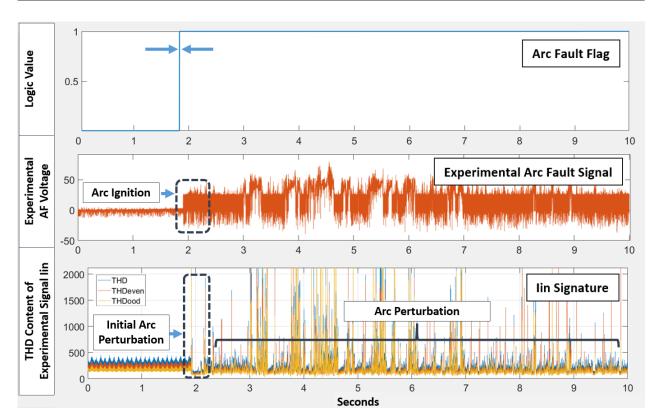

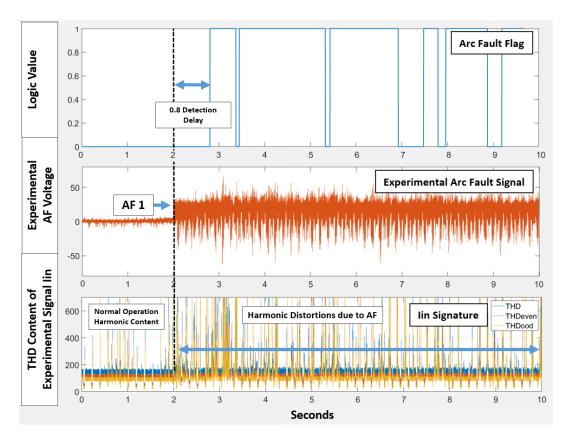

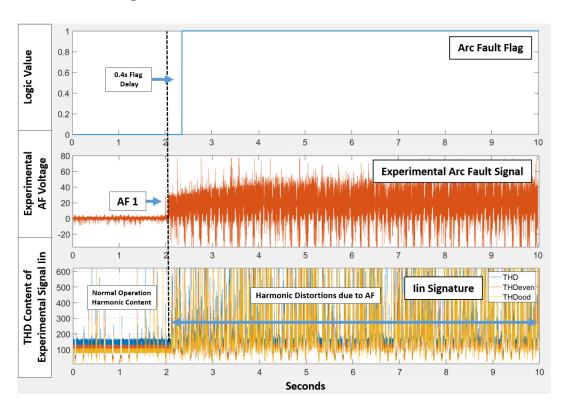

La Fig. 19 illustre comment cette opération est effectuée sur le signal VH2. Une fois ce processus terminé, l'algorithme de détection générera un signal logique avec une valeur de 1 qui restera à 1 jusqu'à ce que le défaut disparaisse. Sur la Fig. 20 est présenté le résultat obtenu dans le cas d'un AF pour une charge résistive.

Figure 19. THDe peak saturation analysis before and after an AF.

Figure 20. VH2 and AF Flag comparison.

Pour effectuer une validation approfondie, l'algorithme est soumis à une série de tests avec différents types de charges, et des variations d'illumination, de changement de charge instantané. Les valeurs spécifiques de toutes les expériences sont répertoriées dans le Tableau 0.0.3

**TABLE 0.0.3.** AF Algorithm testing with different loads.

| 9                                                |                   |

|--------------------------------------------------|-------------------|

| Loads &                                          | Value of Load     |

| Number of AF tested                              |                   |

| Resistance - 5                                   | $47\Omega$        |

| Resistance-5                                     | $22\Omega$        |

| Resistive $47\Omega$ Inductive – $5$ each = $15$ | 5mH, 30mH, 58mH   |

| Resistive $22\Omega$ Inductive – $5$ each = $15$ | 5mH, 30mH, 58mH   |

| $Resistive \ 22\Omega + 1200WVacuum - 5$         | Fast speed        |

| $Resistive \ 22\Omega + 1200WVacuum - 5$         | $Slow\ speed$     |

| LCL Couplin Filter 5                             | LCL Filter Values |

| Total-55                                         |                   |

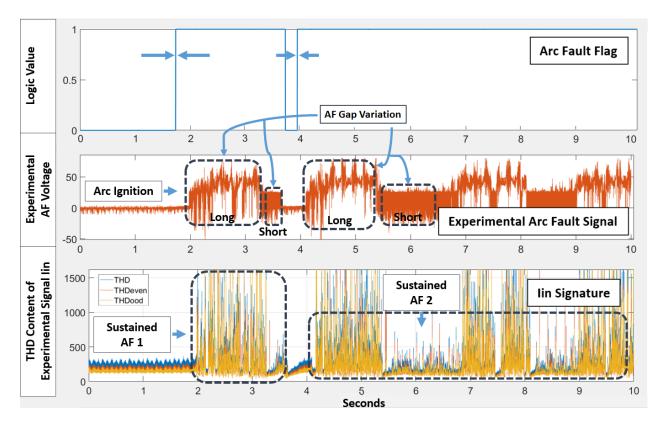

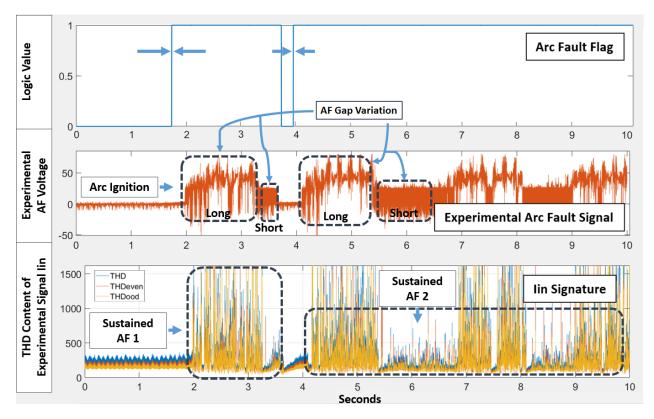

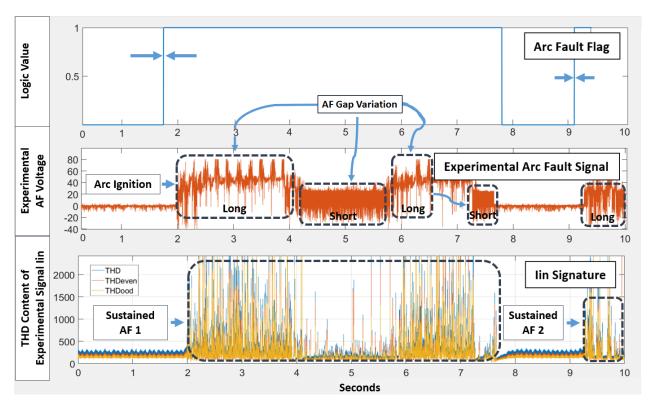

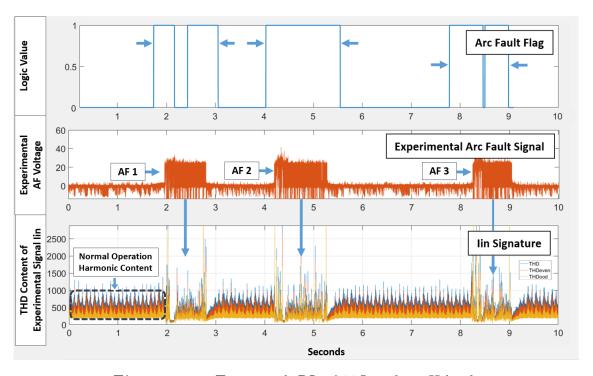

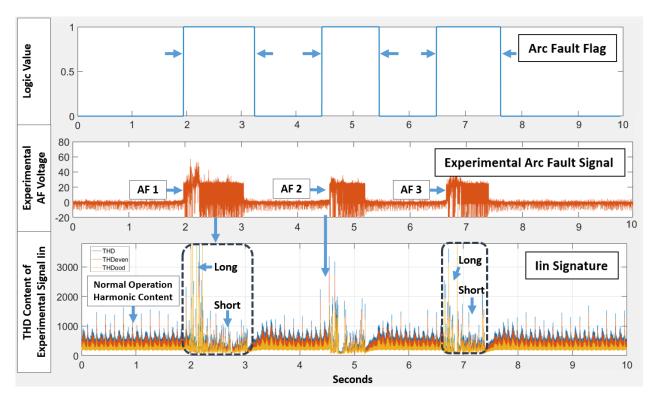

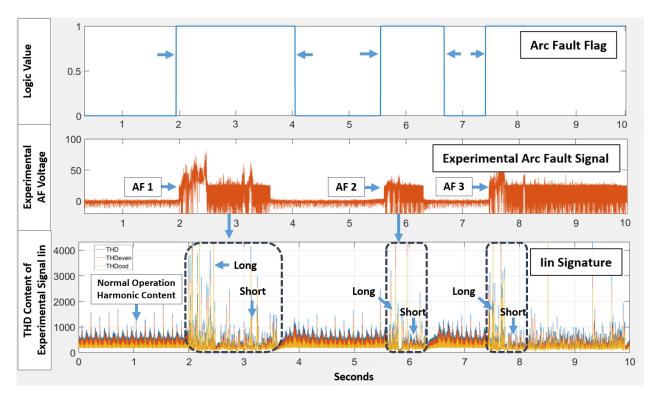

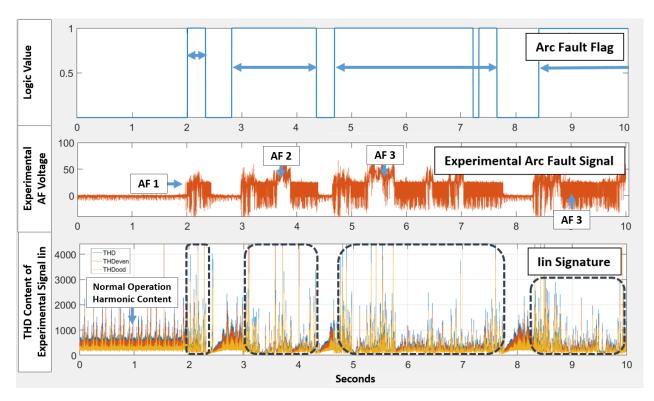

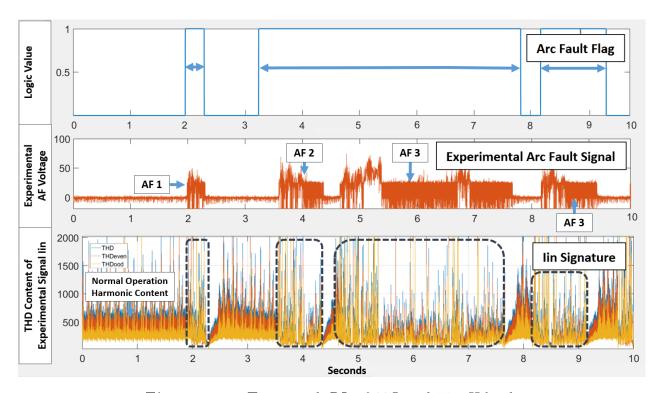

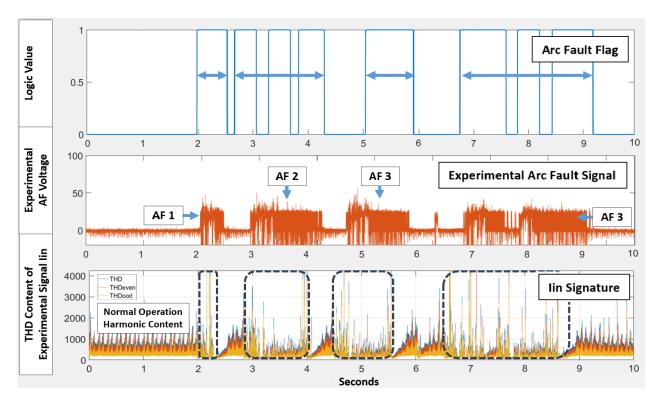

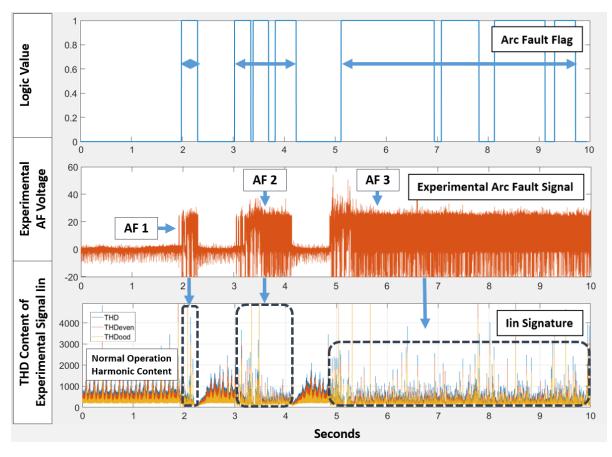

Dans l'ensemble des résultats d'expérimentation présentés dans la Fig. 21, des défauts d'arcs multiples sont générés dans un seul enregistrement afin d'augmenter la difficulté de détection et évaluer l'adaptabilité de l'algorithme. Nous remarquons également comment la distance d'écartement joue un rôle très important dans l'augmentation des perturbations. Plus grand sera l'écartement des électrodes plus grandes seront les variations générées par le défaut.

Les résultats expérimentaux préséntés dans les différentes figures sont obtenus par concaténation de plusieurs enregistrements différents de défauts d'arc afin de tester la robustesse d l'algorithme de détection.

Figure 21. Multiple AF scenario with a  $47\Omega$  load.

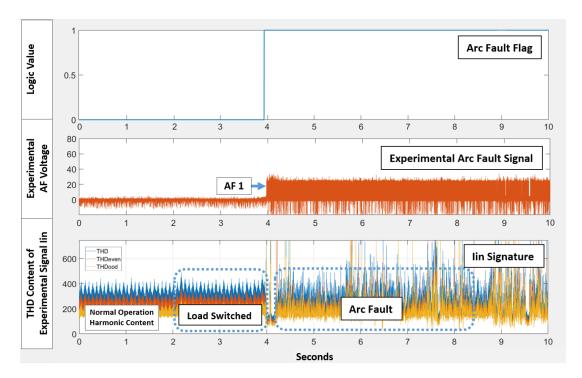

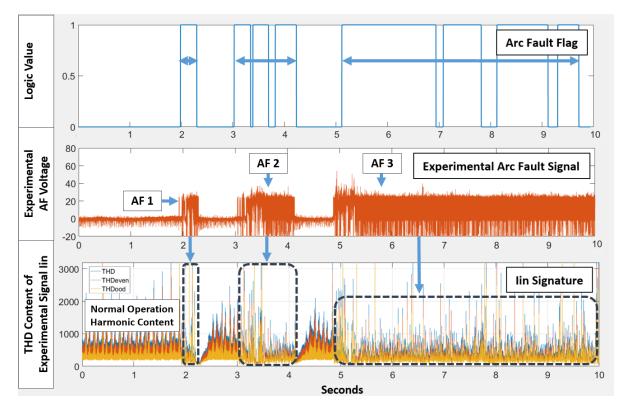

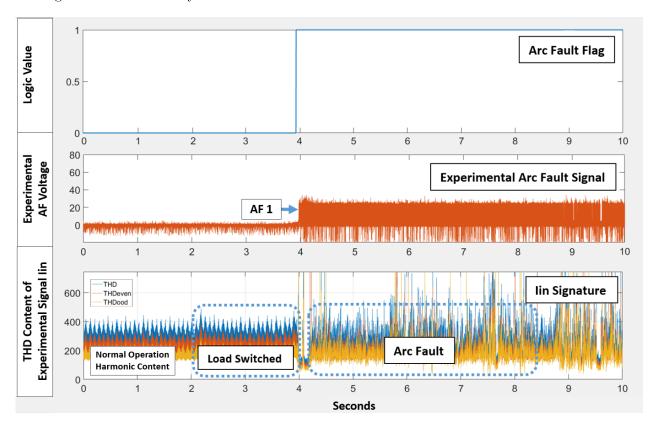

Pour le cas du moteur comme charge, trois défauts sont générés dans le système. En Fig. 22 on observe que l'algorithme détecte sans diffilcutés tous les défauts. Néanmoins pour cette charge au moment de défaut le moteur s'arrête et redémarre très rapidement tout le long de défaut.

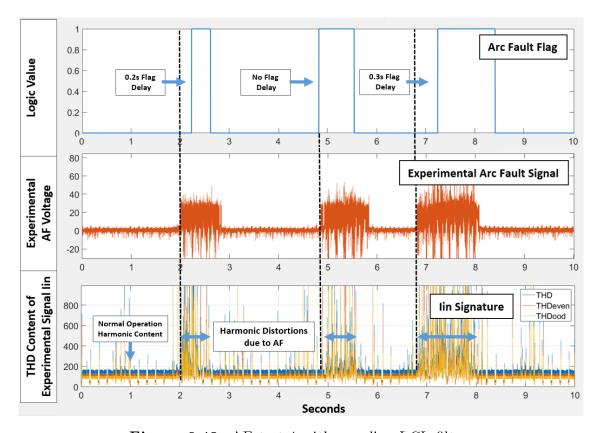

La Fig. 23 présente le comportement de la détection en cas de commutation de charges. Le résultat de détection n'est pas perturbé.

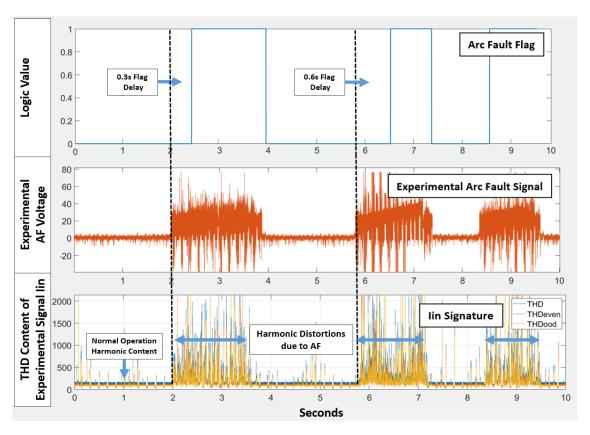

Pour le cas d'une connexion au réseau électrique les résultats de détection sont concluants malgré un retard compris entre 0.3 et 0.6 seconde.

Dans les deux cas on peut observer de légères variations dans le spectre harmonique mais sans conséquances sur l'exactitude de la détection. Ces résultats sont discuteés plus en détail à la section 6.6.

Figure 22. Test 2, algorithm results with 1200 W vacuum load.

Figure 23. AF test side by side with a resistive switched load and its effect in the THD content.

### Symbols and Abbreviation

IGBT Insulated Gate Bipolar Transistor

AF Electric Arc Fault

PV Photovoltaic

AFDD Arc Fault Detection Devices

DC Direct Current

AC Alternating Current

DC/AC Direct Current to Alternating Current

MPPT Maximum Power Point Tracking

NCC Non Current Carrying

CCC Current Carrying Conductor

EGC Equipment Grounding Conductor

NEC National Electric Code

AFCI Arc Fault Circuit Interrupter

kW kilowatt = 1000 Watts

RC Resistive Capacitive

RLC Resistive Inductive and Capacitive

EIA Energy Information Administration

AEO Annual Energy Outlook

NEMS National Energy Modeling System

MLC Multilevel Converter

MLI Multilevel Inverter

NPC Neutral Point Clamped

FLC Flying Capacitor

CCMI Cascade Cells Multilevel Inverter

EMI Electro Magnetic Interference

UPS Uninterpretable Power Supply

$DETL \qquad \hbox{Distributed Energy Technologies Laboratory}$

DFT Discrete Fourier Transform

Tws Time Windows

MPWM Multiple Pulse Width Modulation

SPWM Sinusoidal Pulse Width Modulation

THD Total Harmonic Distortion

$THD_{even}$  Total Even Harmonic Distortion

$THD_{odd}$  Total Odd Harmonic Distortion

# List of Figures

| 1  | AEO report of renewable energy production projected to 2050 iv                                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------|

| 2  | Distribution Grid arrangement vi                                                                                                      |

| 3  | Potential Arc Fault in PV panels vi                                                                                                   |

| 4  | Inverter proposed system schematic diagram, buck variant viii                                                                         |

| 5  | Cascade cells multilevel inverter topology and control viii                                                                           |

| 6  | Simulation results of the DC/AC stage a) $VBridge1$ , b) $VBridge2$ , c) $V_{out}$ , d) $I_{out}$ . ix                                |

| 7  | $VBridge1 \ {\rm and} \ VBridge2 \ {\rm signals} \ {\rm obtained} \ {\rm using} \ {\rm DC/DC} \ {\rm Buck} \ {\rm variant.}  .  .  x$ |

| 8  | Voltage and current waveforms of the nine-levels AC output, using buck variant. $\mathbf{x}$                                          |

| 9  | Experimental Test bench xii                                                                                                           |

| 10 | AF Generation device UL1699B xii                                                                                                      |

| 11 | AF Load Study Schematic Diagram xiii                                                                                                  |

| 12 | Multilevel waveforms obtained under AF xiv                                                                                            |

| 13 | THD decomposition in $THD_{even}$ and $THD_{odd}$ before and after an AF xv                                                           |

| 14 | AF Testing protocol for different loads, with highlighted measuring points xv                                                         |

| 15 | VBridge2 harmonics decomposition xvi                                                                                                  |

| 16 | $I_{out}$ THD Decomposition technique xvi                                                                                             |

| 17 | Summary of Results for AF Tests                                                                                                       |

| 18 | Proposed electric DC AF detection algorithm xviii                                                                                     |

| 19 | THDe peak saturation analysis before and after an AF xix                                                                              |

| 20 | VH2 and AF Flag comparison                                                                                                            |

| 21 | Multiple AF scenario with a $47\Omega$ load xxi                                                                                       |

xxvi List of Figures

| 22   | Test 2, algorithm results with 1200 W vacuum load                             | xxi |

|------|-------------------------------------------------------------------------------|-----|

| 23   | AF test side by side with a resistive switched load and its effect in the THD |     |

|      | content                                                                       | xxi |

| 1.1  | Schematic diagram of proposed converter in [1]                                | 38  |

| 1.2  | Schematic diagram of proposed converter in [2]                                | 39  |

| 2.1  | AEO report of renewable energy production projected to 2050                   | 48  |

| 2.2  | Main structure of a PV installation                                           | 49  |

| 2.3  | Schematic diagram of three-level NPC MLI                                      | 52  |

| 2.4  | Schematic diagram of four-level FLC MLI                                       | 53  |

| 2.5  | Schematic diagram of nine-level CCMI                                          | 55  |

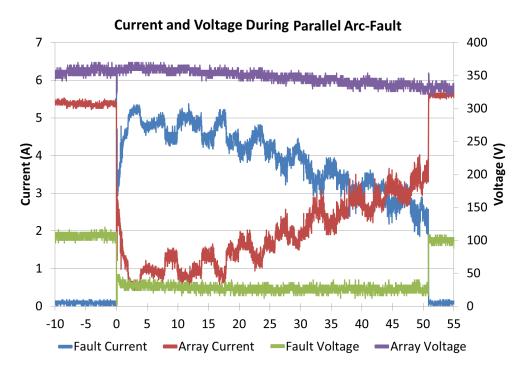

| 2.6  | Output DC voltage and current of a PV array under normal and AF conditions.   | 56  |

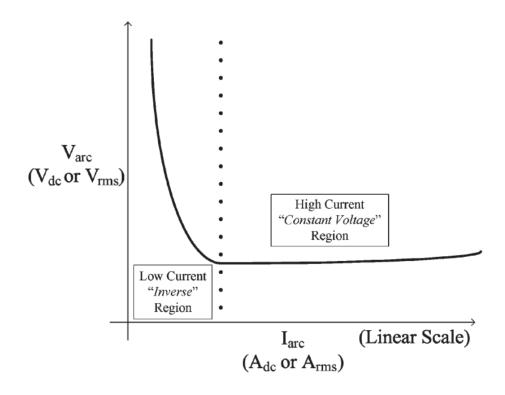

| 2.7  | The volt-ampere (V-I) characteristics of electric arcs fault                  | 57  |

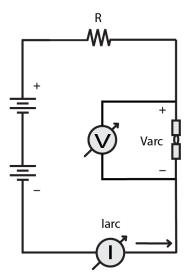

| 2.8  | AF generator schematic diagram                                                | 58  |

| 2.9  | Main blocks diagram of a PV installation                                      | 59  |

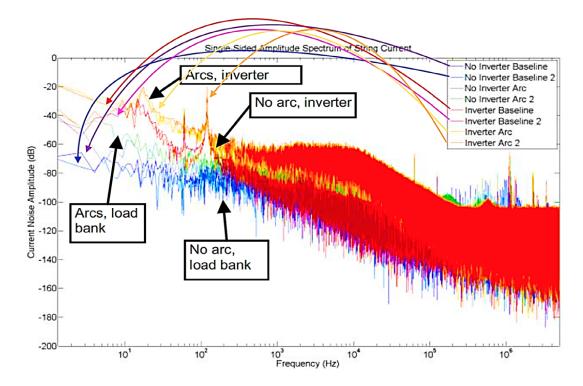

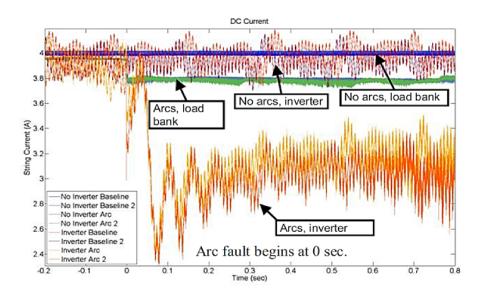

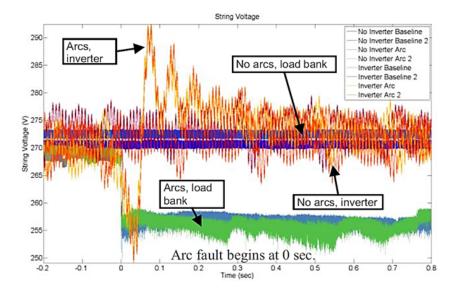

| 2.10 | PV system current signature tested with two different inverters and without   |     |

|      | inverter, after an AF scenario                                                | 62  |

| 2.11 | PV system current signatures tested with two different types of inverter and  |     |

|      | without it, under AF scenario                                                 | 63  |

| 2.12 | PV system current signatures tested with two different types of inverter and  |     |

|      | without it, under AF scenario                                                 | 63  |

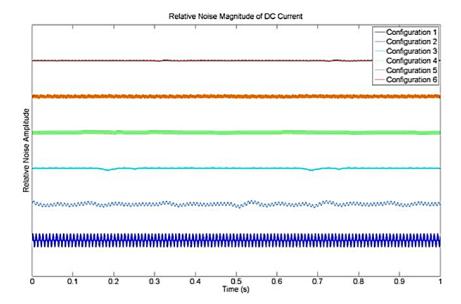

| 2.13 | Single string current waveform for PV configurations of Table 2.5.1           | 64  |

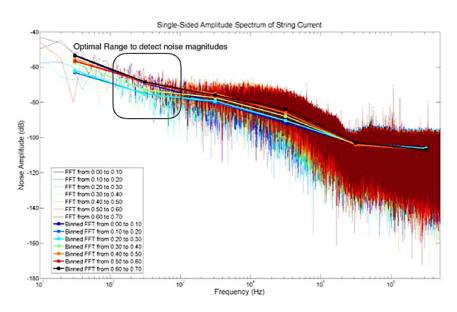

| 2.14 | String current arc signatures, applying DFT for 0.10s subsections             | 65  |

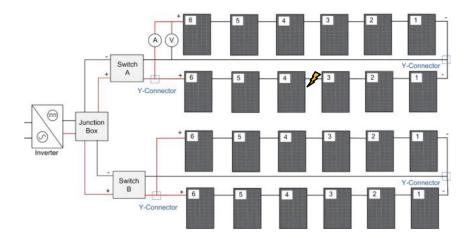

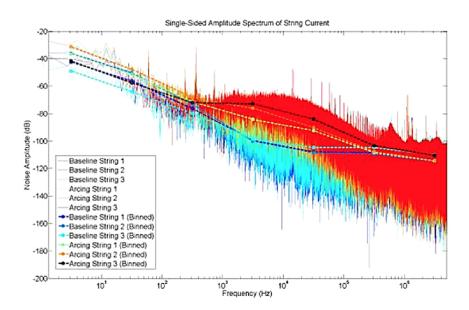

| 2.15 | PV modules distribution for noise recording in tests of Sandia Labs           | 66  |

| 2.16 | Noise recordings with AF scenario and baseline system in DETL                 | 66  |

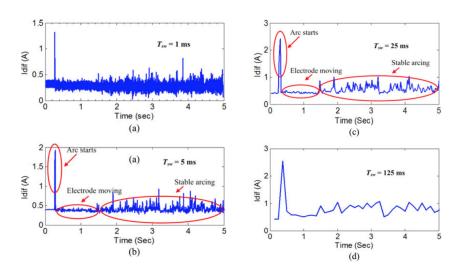

| 2.17 | Idif waveform from different time window length (a) $Tsw=1$ ms. (b) $Tsw=1$   |     |

|      | 5 ms. (c) $Tsw = 25$ ms. (d) $Tsw = 125$ ms                                   | 67  |

| 2.18 | Baseline AF signature to perform calculations                                 | 68  |

List of Figures xxvii

| 3.1  | Inverter proposed system schematic diagram, Boost variant                                                                  | 70 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Inverter proposed system schematic diagram, Buck variant                                                                   | 70 |

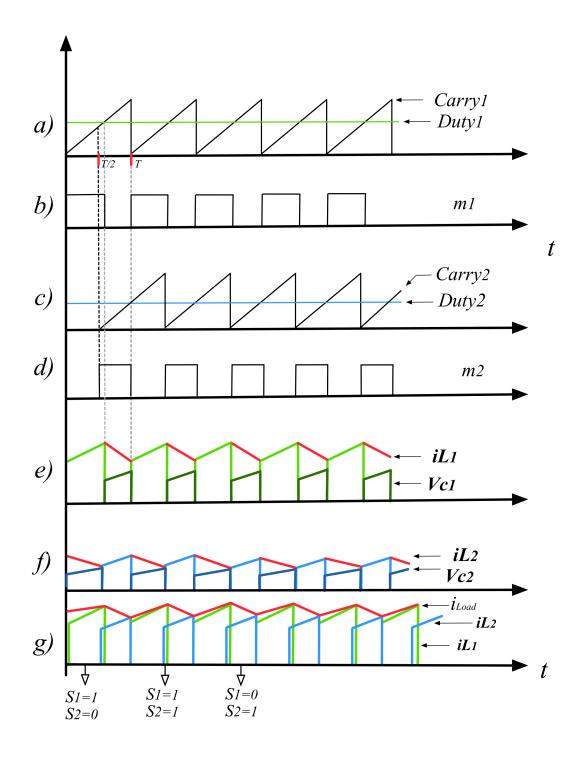

| 3.3  | Control strategy for boost variant converter; a) $Carry_1$ and $Duty_1$ , b) Pulse                                         |    |

|      | $m_1$ c) $Carry_2$ and $Duty_2$ , d) Pulse $m_2$ , e) $i_{L_1}$ and $V_{C_1}$ , f) $i_{L_2}$ and $V_{C_2}$ g) $i_{Load}$ . | 73 |

| 3.4  | Discharging circuit during state 0                                                                                         | 75 |

| 3.5  | Proposed topology in switching state 3 where $S_1=1,\ S_2=0$ with highlighted                                              |    |

|      | currents paths.                                                                                                            | 76 |

| 3.6  | Proposed topology in switching state 2 where $S_1=0,\ S_2=1$ with highlighted                                              |    |

|      | currents paths.                                                                                                            | 77 |

| 3.7  | Proposed topology in switching state $S_1=1,\ S_2=1$ with highlighted currents                                             |    |

|      | paths                                                                                                                      | 78 |

| 3.8  | Proposed topology buck variant in switching state $S_1=1,\ S_2=0$ with                                                     |    |

|      | highlighted currents paths                                                                                                 | 79 |

| 3.9  | Proposed topology buck variant in switching state $S_1$ =0, $S_2$ =1 with                                                  |    |

|      | highlighted currents paths                                                                                                 | 80 |

| 3.10 | Multilevel $V_{out}$ for cascaded converter                                                                                | 82 |

| 3.11 | Nine-level SPWM technique                                                                                                  | 83 |

| 3.12 | Cascade cells multilevel inverter topology and control                                                                     | 84 |

| 4.1  | Schematic diagram of the smart inverter buck variant                                                                       | 86 |

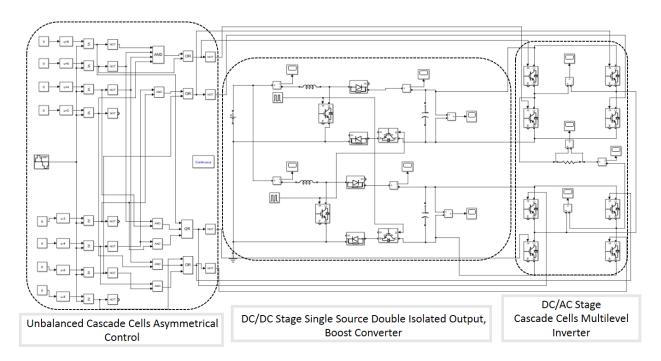

| 4.2  | Simulink resulting schematic diagram of the Fig. 4.1                                                                       | 87 |

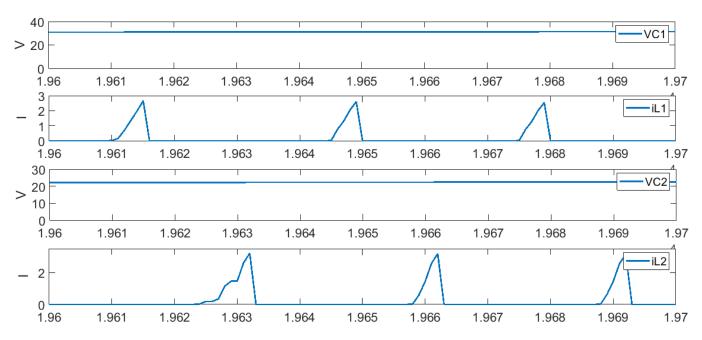

| 4.3  | Stimulation results of the DC/DC stage a) $V_{C_1}$ b) $iL_1$ c) $V_{C_2}$ d) $iL_2$                                       | 87 |

| 4.4  | Stimulation results of the DC/AC stage a) $VBridge1$ , b) $VBridge2$ , c) $V_{out}$ , d) $I_{out}$ .                       | 88 |

| 4.5  | Schematic diagram of the inverter boost variant                                                                            | 89 |

| 4.6  | Simulink resulting schematic diagram of the Fig. 4.5                                                                       | 90 |

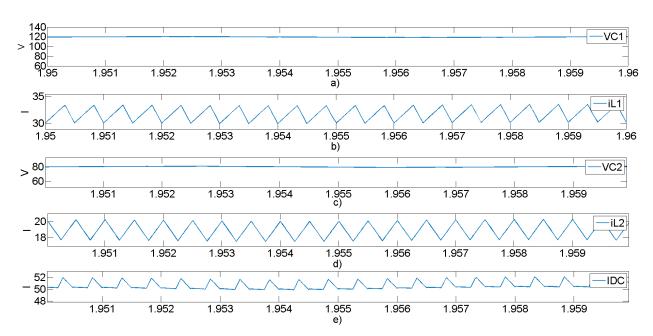

| 4.7  | Simulation results of the DC/DC stage a) $V_{C_1}$ b) $iL_1$ c) $V_{C_2}$ d) $iL_2$ e) $iDC$                               | 90 |

| 4.8  | Simulation results of the DC/AC stage a) $VBridge1$ , b) $VBridge2$ , c) $V_{out}$ , d) $I_{out}$ .                        | 91 |

| 4.9  | VBridge1 and $VBridge2$ signals obtained using DC/DC Buck variant                                                          | 92 |

| 4.10 | Voltage and current waveforms of the nine-levels AC output, using buck variant                                             | 93 |

xxviii List of Figures

| 4.11 | VBridge1 and $VBridge2$ signals obtained using DC/DC boost variant               | 93  |

|------|----------------------------------------------------------------------------------|-----|

| 4.12 | Voltage and current waveforms of the nine-levels AC output, using boost variant. | 94  |

| 4.13 | Experimental test bench                                                          | 94  |

| 5.1  | UL1699B AF generator mechanism diagram                                           | 96  |

| 5.2  | AF generation "Fixed Distance Ignition"                                          | 97  |

| 5.3  | AF Load Study Schematic Diagram                                                  | 98  |

| 5.4  | UL1699B AF generator mechanism diagram                                           | 98  |

| 5.5  | $\mathrm{DC}/\mathrm{DC}$ stage (Buck variant), with highlighted measuring point | 101 |

| 5.6  | Current waveform $i_{DC}$ delivered for the DC/DC stage                          | 101 |

| 5.7  | Conventional DC/DC boost converter behavior, before and after an AF. $$          | 102 |

| 5.8  | Cascade cells configuration for AF testing                                       | 104 |

| 5.9  | Multilevel waveforms obtained under AF                                           | 104 |

| 5.10 | Texas Instruments MPPT Prototyping Board                                         | 106 |

| 5.11 | Schematic diagram for AF testing with AF before MPPT module                      | 107 |

| 5.12 | Experimental results of arcing before MPPT module                                | 108 |

| 5.13 | Schematic diagram for AF testing with AF after MPPT module                       | 108 |

| 5.14 | Experimental results of arcing after MPPT module                                 | 109 |

| 6.1  | THD study of multilevel waveform                                                 | 114 |

| 6.2  | THD decomposition in $THD_{even}$ and $THD_{odd}$ before and after an AF         | 115 |

| 6.3  | AF Testing protocol for different loads, with highlighted measuring points       | 117 |

| 6.4  | VBridge2 harmonics decomposition                                                 | 119 |

| 6.5  | $I_{out}$ THD Decomposition technique                                            | 119 |

| 6.6  | VBridge2 harmonics decomposition                                                 | 120 |

| 6.7  | Iout Harmonic Decomposition.                                                     | 120 |

| 6.8  | VH2 harmonics decomposition                                                      | 122 |

| 6.9  | $I_{out}$ THD analysis for hammer-drill load                                     | 122 |

| 6.10 | VH2 harmonics decomposition                                                      | 123 |

| 6.11 | Iout THD analysis for vacuum load                                                | 123 |

List of Figures xxix

| 6.12 | Summary of Results for AF Tests                                                    | 124 |

|------|------------------------------------------------------------------------------------|-----|

| 6.13 | Distribution Grid arrangement                                                      | 126 |

| 6.14 | Schematic diagram of impedance between the converter and the grid                  | 128 |

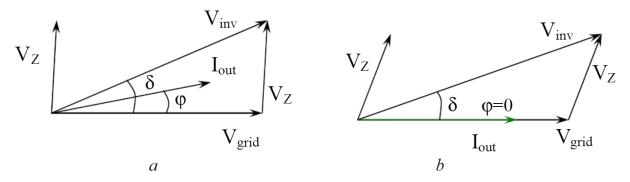

| 6.15 | Phasor-diagram of the voltages and currents of the single-phase inverter           | 128 |

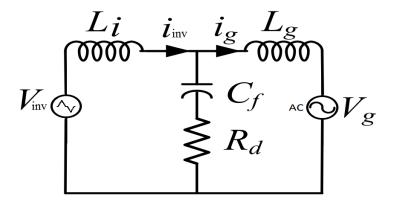

| 6.16 | LCL coupling filter schematic                                                      | 131 |

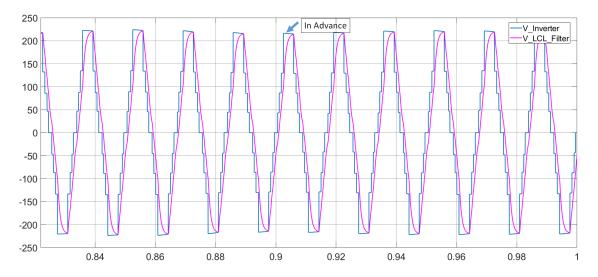

| 6.17 | Nine level inverter voltage and LCL coupling filter smoothed voltage               | 131 |

| 6.18 | THDe Analysis of $VH2$ before and after an AF                                      | 133 |

| 6.19 | THDe peak saturation analysis before and after an AF                               | 134 |

| 6.20 | VH2 and AF Flag output comparison                                                  | 134 |

| 6.21 | THD Analysis of Iin                                                                | 135 |

| 6.22 | Proposed electric DC AF detection algorithm                                        | 137 |

| 6.23 | Single AF with a $22\Omega$ load, constant electrodes spacing, detection algorithm |     |

|      | result                                                                             | 141 |

| 6.24 | Single AF with a $22\Omega$ load, variable electrodes spacing, detection algorithm |     |

|      | result                                                                             | 142 |

| 6.25 | Multiple AF scenario with a 47 $\Omega$ load                                       | 143 |

| 6.26 | Multiple AF scenario with a 47 $\Omega$ load                                       | 143 |

| 6.27 | Test 1 with RL of $22\Omega$ and $5mH$ load                                        | 145 |

| 6.28 | Test 2 with RL of $22\Omega$ and $5mH$ load                                        | 145 |

| 6.29 | Test 3 with RL of $22\Omega$ and $31mH$ load                                       | 146 |

| 6.30 | Test 4 with RL of $22\Omega$ and $31mH$ load                                       | 146 |

| 6.31 | Test 5 with RL of $22\Omega$ and $51mH$ load                                       | 147 |

| 6.32 | Test 6 with RL of $22\Omega$ and $51mH$ load                                       | 147 |

| 6.33 | Test 1 algorithm results, 1200 W vacuum load                                       | 148 |

| 6.34 | Test 2 algorithm results, 1200 W vacuum load                                       | 149 |

| 6.35 | Test 3 for Vacuum cleaner of 1200W                                                 | 149 |

| 6.36 | AF test side by side with a resistive switched load and its effect in the THD      |     |

|      | content                                                                            | 150 |

xxx List of Figures

| 6.37 | AF test 1 with coupling LCL filter                                               | 152 |

|------|----------------------------------------------------------------------------------|-----|

| 6.38 | AF test 2 with coupling LCL filter                                               | 152 |

| 6.39 | AF test 3 with coupling LCL filter                                               | 153 |

| 6.40 | AF test 4 with coupling LCL filter                                               | 153 |

| 6.41 | Test 1 - fast radiation fluctuation in the DC input source                       | 155 |

| 6.42 | Test 2 - fast radiation fluctuation in the DC input source                       | 155 |

| 6.43 | Test 3 - slow radiation fluctuation in the DC input source                       | 156 |

| 6.44 | Test 4 - slow radiation fluctuation in the DC input source                       | 156 |

| A.1  | Schematic diagram of an ungrounded PV system                                     | 175 |

| A.2  | Schematic diagram of a grounded PV system                                        | 175 |

| A.3  | RC model representation of PV panel                                              | 176 |

| A.4  | Potential points of internal fault in a PV panel                                 | 178 |

| A.5  | Potential points of fault in a PV array                                          | 178 |

| A.6  | Arc Fault damage in a 10 kW installation, due to inappropriate AF handling.      | 179 |

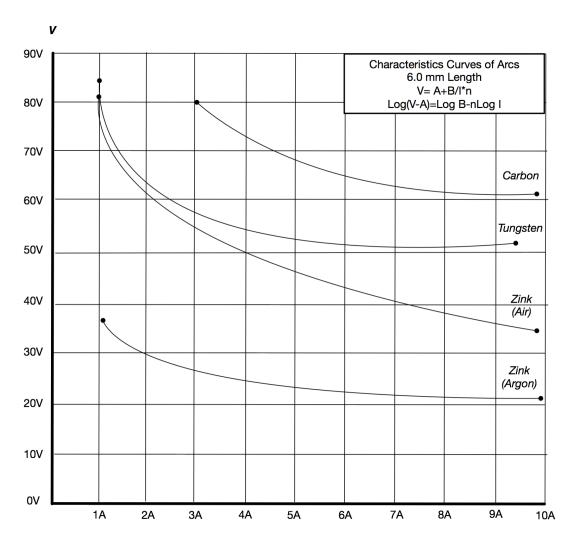

| A.7  | V-I characteristics curves of AF for different materials of electrodes           | 181 |

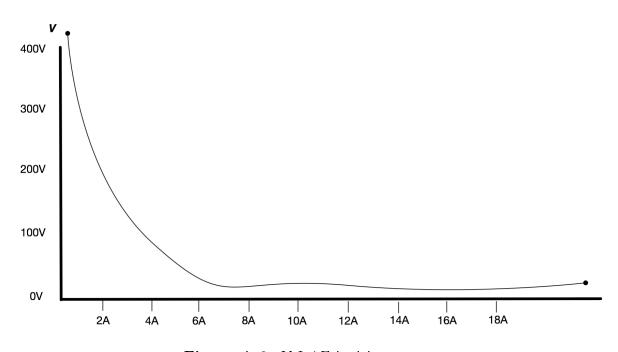

| A.8  | V-I AF ignition curve                                                            | 183 |

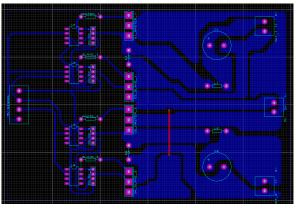

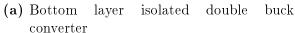

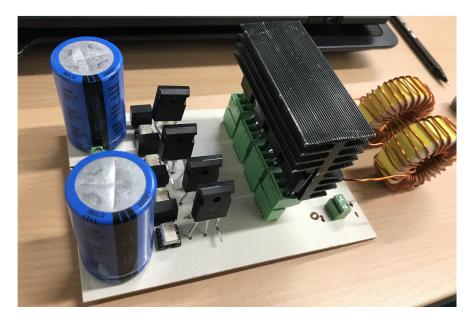

| B.1  | Design of isolated double buck converter                                         | 186 |

| B.2  | Developed double DC/DC buck converter                                            | 186 |

| В.3  | Design of isolated double boost converter                                        | 187 |

| B.5  | Developed double DC/DC boost converter (left) and full H bridge (Right). $$ .    | 187 |

| B.4  | PCB Design of the full bridge for the DC/AC stage                                | 188 |

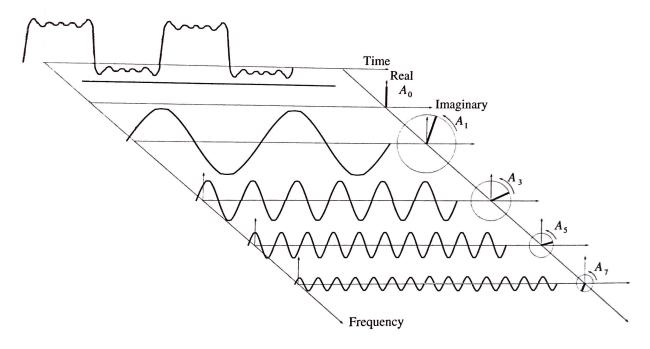

| C.1  | Fourier representation of a square waveform as the sum of a series of sinusoidal |     |

|      | waves                                                                            | 193 |

# List of Tables

| 0.0.1 Test Bench Equipment                      | X   |

|-------------------------------------------------|-----|

| 0.0.3 AF Algorithm testing with different loads | XX  |

| 1.1.1 Single Sourced Converters Comparison      | 40  |

| 2.5.1 PV Configurations                         | 65  |

| 3.2.1 Boost Variant Switching States            | 72  |

| 3.2.2 Buck Variant Switching States             | 79  |

| 3.3.1 Stepping Logic for a Nine-Level Converter | 82  |

| 4.2.1 Simulation Components Values              | 88  |

| 4.2.2 Component Values and Settings             | 92  |

| 5.3.1 Test Bench Equipment and Values           | .00 |

| 5.5.1 Experimental Values for MPPT Test         | .06 |

| 6.7.1 AF Algorithm testing with different loads | .40 |

| C 1 1 Wayoform Symmetry Characteristics         | 03  |

# Contents

| $\mathbf{S}_{\mathbf{J}}$ | mbc   | ls and Abbreviation xx                                        | ciii                   |

|---------------------------|-------|---------------------------------------------------------------|------------------------|

| Li                        | st of | Figures                                                       | $\mathbf{x}\mathbf{v}$ |

| Li                        | st of | Tables                                                        | xi                     |

| 1                         | Intr  | oduction                                                      | 36                     |

|                           | 1.1   | PV Converters                                                 | 37                     |

|                           | 1.2   | Electric DC Arc Fault Detection                               | 40                     |

|                           | 1.3   | PV Converters and Electric DC Arc Detector                    | 42                     |

|                           | 1.4   | Objectives                                                    | 43                     |

|                           | 1.5   | Justification                                                 | 43                     |

|                           | 1.6   | Chapters Description                                          | 44                     |

|                           | 1.7   | Results of this Research                                      | 44                     |

| <b>2</b>                  | Inve  | erter for PV Applications and electric DC arc Fault Detection | 47                     |

|                           | 2.1   | Introduction                                                  | 47                     |

|                           | 2.2   | Context of this Study                                         | 47                     |

|                           | 2.3   | Photovoltaic Installation Structure                           | 48                     |

|                           |       | 2.3.1 Neutral Point Clamped Multilevel Inverter               | 51                     |

|                           |       | 2.3.2 Flying Capacitor Multilevel Inverter                    | 52                     |

|                           |       | 2.3.3 Cascade Cells Multilevel Inverter                       | 53                     |

Contents xxxiii

|   | 2.4 | Arc Fault Modeling                                                               | 55 |

|---|-----|----------------------------------------------------------------------------------|----|

|   | 2.5 | Arc Fault Detection Techniques                                                   | 59 |

|   |     | 2.5.1 Spectrum Analysis Detection Technique                                      | 60 |

| 3 | Inv | erter Proposal for PV Applications                                               | 69 |

|   | 3.1 | Main Structure of the Proposed Inverter Topology                                 | 69 |

|   | 3.2 | Development of the DC/DC Stage                                                   | 70 |

|   |     | 3.2.1 Isolated Double Boost Converter for DC/DC Stage                            | 71 |

|   |     | 3.2.2 Isolated Double Buck Converter for DC/DC Stage                             | 77 |

|   | 3.3 | Multilevel DC/AC Stage                                                           | 81 |

|   |     | 3.3.1 DC/AC Proposal Operational Principle                                       | 81 |

|   |     | 3.3.2 Nine-Level SPWM Modulation                                                 | 83 |

| 4 | Inv | erter Simulation and Experimental Results                                        | 85 |

|   | 4.1 | Introduction                                                                     | 85 |

|   | 4.2 | Simulation Results                                                               | 85 |

|   |     | 4.2.1 Inverter Buck Variant                                                      | 86 |

|   |     | 4.2.2 Inverter Boost Variant                                                     | 88 |

|   | 4.3 | Inverter Experimental Implementation Results                                     | 91 |

|   |     | 4.3.1 Inverter Buck Variant                                                      | 91 |

|   |     | 4.3.2 Inverter Boost Variant                                                     | 92 |

| 5 | Ana | alysis of Internal Signal Perturbations in $\mathrm{DC/DC}$ and $\mathrm{DC/AC}$ |    |

|   | Cor | nverters Under AF                                                                | 95 |

|   | 5.1 | Introduction                                                                     | 95 |

|   | 5.2 | DC Arc Fault Generation                                                          | 96 |

|   |     | 5.2.1 Series Arcing Test Connection                                              | 96 |

|   | 5.3 | Converter Configuration for Arcing Test                                          | 98 |

|   | 5.4 | Converter Behavior under DC Arc Fault                                            | 99 |